使用Synplify综合时保留logic

在使用Synplify综合时,此工具会自动优化我的设计。

当然此功能有好有坏,最近有个项目需要使用Chipscope观察内部信号,打开inserter就懵了,信号列表中我的设计有的是名字被改了,有的是干脆给优化没了。

网上当然也有人提出这个问题, 例如 http://www.xilinx.com/support/answers/5249.html 就提供了一个 /* synthesis syn_keep = 1 */ 的语法来保留自己的设计。

随后又以 /* synthesis syn_keep = 1 */ 为关键词搜索了一下,又发现了其他的新内容,随即记录一下。

在 Synopsys FPGA Synthesis Attribute Reference Manual 中提到了三个语法:syn_keep ,syn_preserve, syn_noprune 并对三种语法做出了比较。

然而看了此表还是很模糊,再看了一下Synplify Pro for Microsemi Edition User Guide文档中 Preserving Objects from Being Optimized Away 部分则会有更深入的解释。

由此可以总结一下:

syn_keep最常用,可以用于wire,reg和shared register两种情况;

syn_probe处于观察的目的可以使用于wire或者reg (ChipScope观察信号的话使用此语法应该足够了);

syn_preseve使用于固定值驱动(constant-driven)的register或者状态机register中;

而syn_noprune使用于例化的模块(instance),即使例化模块有未使用的端口,也可以让模块保留下来。

关于Shared register:

共享的register又可以称为重复的logic。

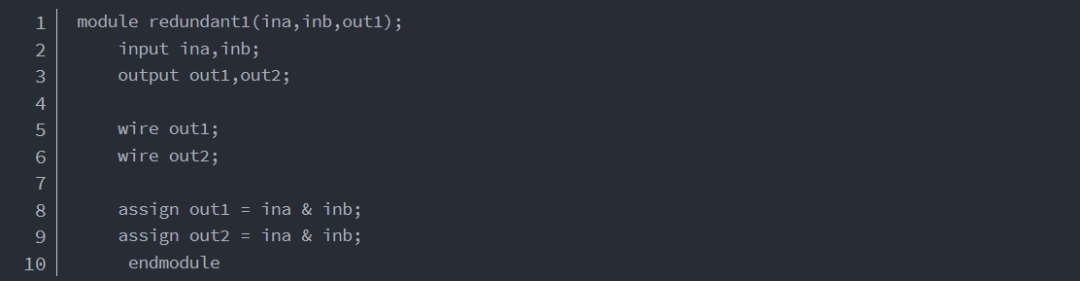

参考如下的代码:

代码如上编写的话,综合工具自动去掉一个AND gate,因为out1和out2使用同样的AND gate就足够了

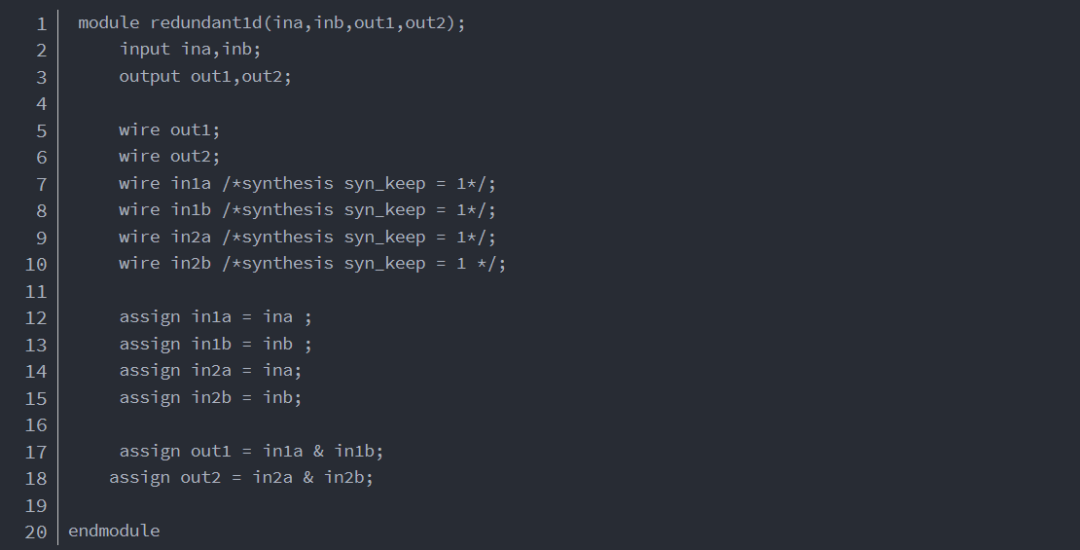

若是代码如下的话:

由于加了syn_keep语法导致综合结果是两个AND gate都会保留下来。

需要注意的一点是syn_keep语法需要用在例化程序的输入端(input of instance)才会有效果,例如上面代码syn_keep加在out1,out2之后是没有任何效果的。

关于固定驱动值(Constant-driven)

指某一个flip-flop的输入总是为常数,例如有一个flip-flop总是被logic 1 驱动,则在综合的时候工具会自动移除此flip-flop且把信号绑到VCC上。使用syn_preseve的话可以保留此flip-flop。

776

776

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?