基于Vivado DDS ip核的DDS信号发生器:

在Vivado软件中调出DDS ip核进行设置,很多参数可以参考xilinx官方手册,比较重要的是System Clock系统时钟和Phase Widh相位宽度的设置,这是最终得到波形的频率和相位所需要的基础参数,在这里我分别设置为50Mhz和16bit。

在implementation页面设置频率控制字和相位控制字是手动输入还是固定,这里phase increment programmability(频率控制字)设置为programmable,phase offset programmability(相位控制字)设置为streaming(none或fixed为固定,programmable意为可改变,streaming意为可以更快速高效地接收控制并改变,注意频率控制字和相位控制字选programmable还是streaming都可以,但是不能选同一个)。输出选sine(这个看自己需求)。

在这一页将output tready打钩,相当于加入几个握手信号。

可以看到最后的参数数据是这样的。

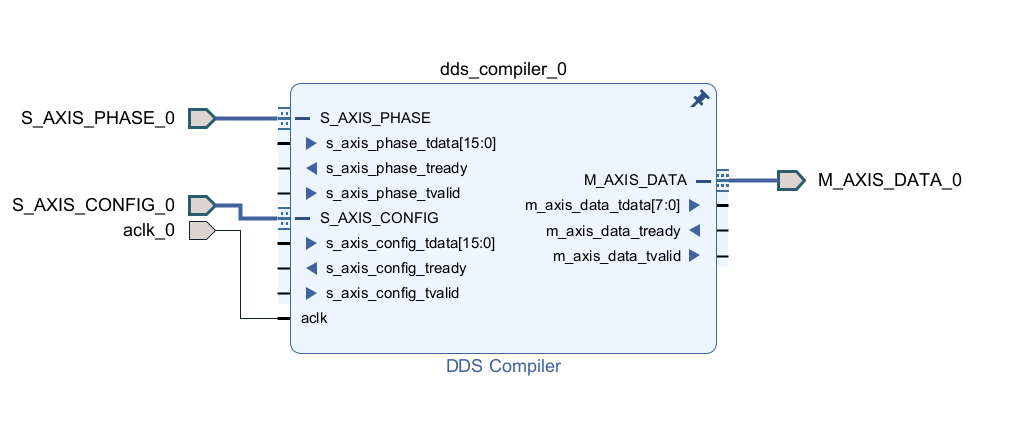

其他都设为默认,可以看到最后DDS结构图是这样,除了频率控制字、相位控制字、时钟作为输入以外,还有几个ready和valid握手信号,这些ready和valid信号均为1时输入信息才会被接收。

经过Generate Output Products和create HDL Wrapper生成封装文件后,新建testbench文件如下图:

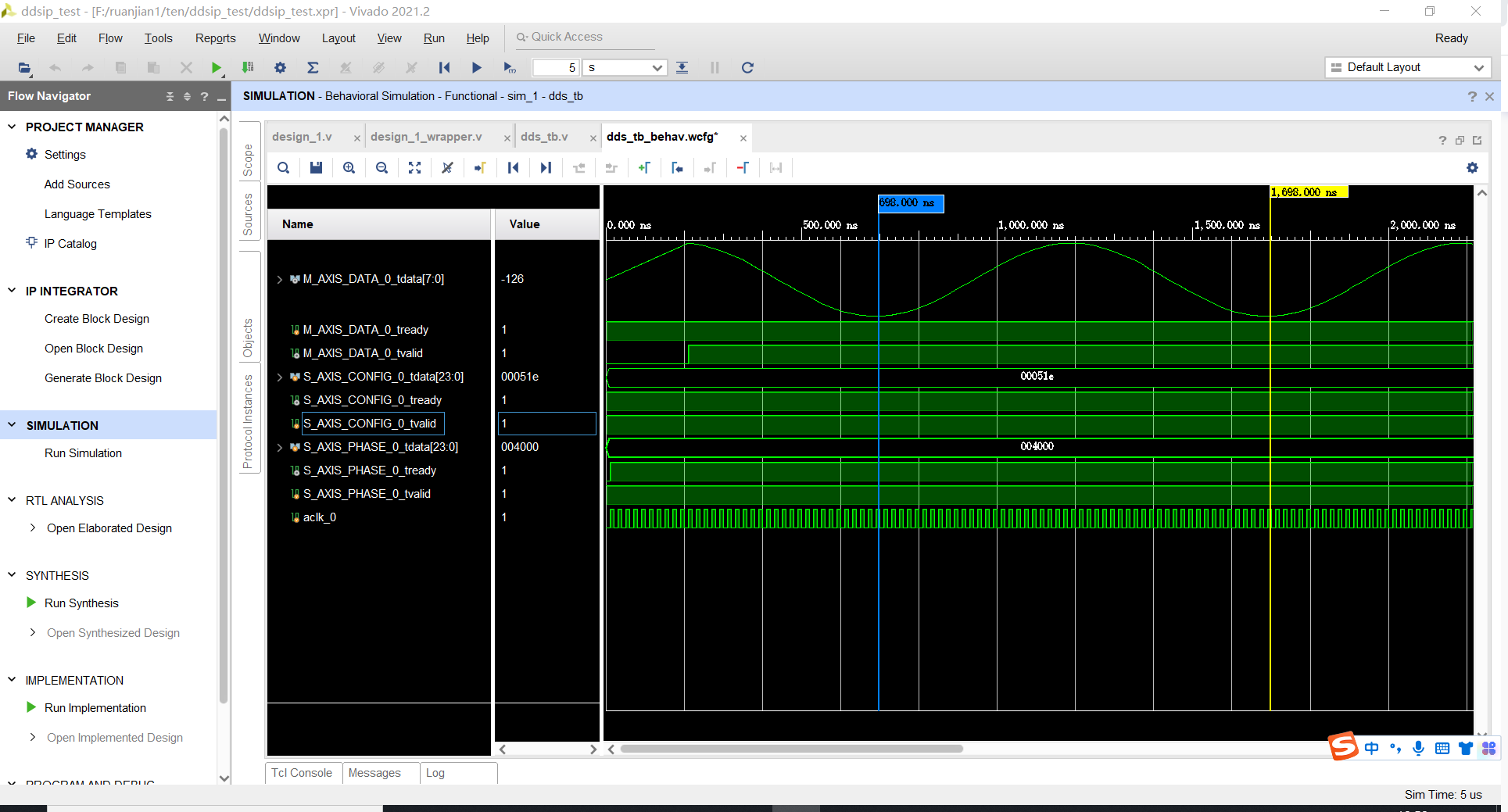

根据频率控制字和相位控制字的公式,我这里fclk=50mhz,N=16,如最终需要得到频率1Mhz,相位π/2的波形,经过计算,频率控制字为1310,相位控制字为16384,输入的ready和valid均设置为1。从最终仿真波形中可以看出频率为周期为1000ns,也就是频率1Mhz,相位也是正确的。

5404

5404

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?