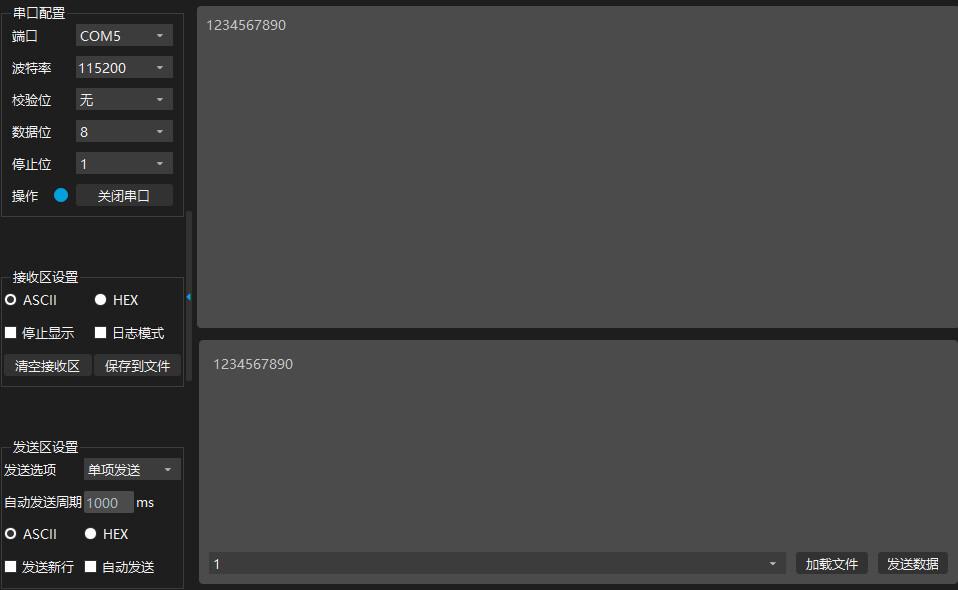

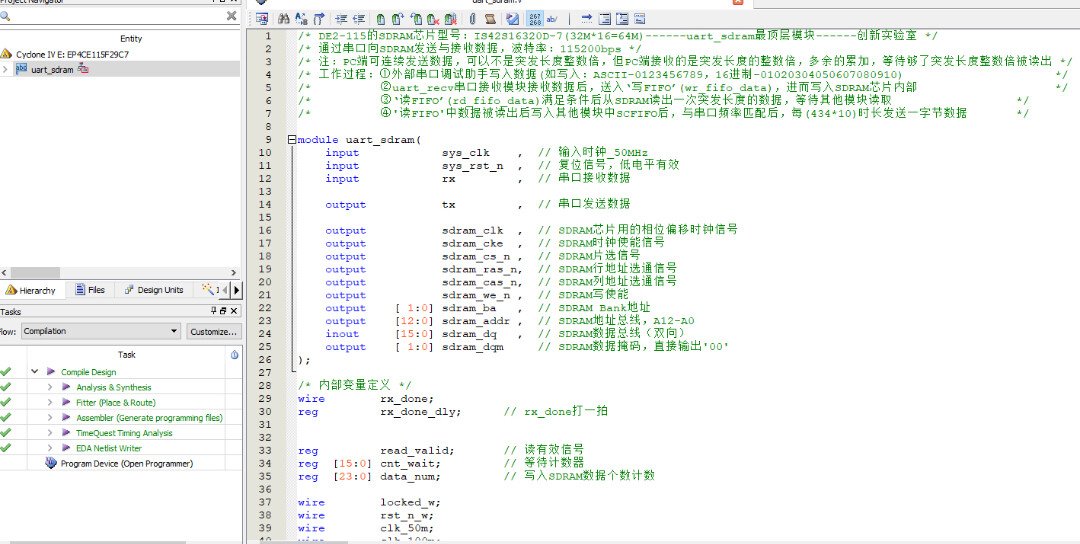

FPGA开发:SDRAM驱动代码,使用串口向sdram写数据,数据环回后被SDRAM送回到串口进行输出,中间使用FIFO进行跨时钟域处理,所用开发板DE2-115,SDRAM型号IS42S16320D-7,代码进行了详细注释,改动少于参数即可适配其他型号

ID:3480641046197573

白衫如初oh

【标题】FPGA开发中的SDRAM驱动代码设计与实现

【摘要】本文围绕FPGA开发中的SDRAM驱动代码展开讨论,介绍了如何使用串口向SDRAM写入数据,并进行环回测试,最后通过SDRAM将数据送回串口输出。文章重点探讨了跨时钟域处理中的FIFO设计,并结合开发板DE2-115和SDRAM型号IS42S16320D-7进行具体实现。

【关键词】FPGA开发、SDRAM驱动代码、串口通信、数据环回、跨时钟域处理、FIFO设计、DE2-115开发板、IS42S16320D-7型号

【正文】

-

引言

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,广泛应用于嵌入式系统中。S

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

601

601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?