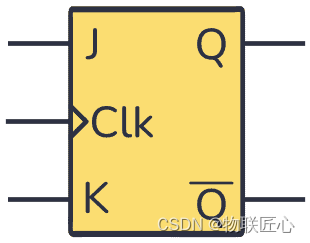

JK触发器符号

JK触发器符号

JK触发器是一种可以设置、重置和切换的人字拖。它可用于制造计数器、事件检测器、分频器等等。

触发器是可以在其输出上存储数字值的组件。它们有一个时钟输入(Clk),用于确定何时可以更改输出状态。

Flip-Flop的两个输入“J”和“K”并不是引脚功能的缩写(S-R锁存器就是这种情况)。它们的发明者杰克·基尔比(JK)选择了它们,以将他的人字拖设计与其他类型的人字拖设计区分开来。

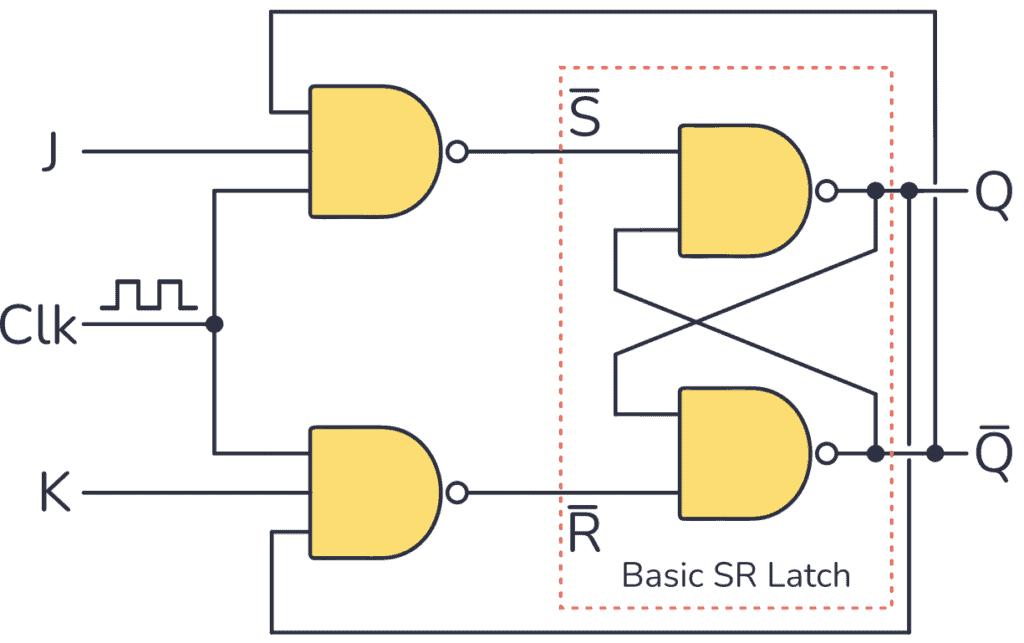

您可以在下面看到该电路的基本实现。它基于 S-R 锁存器,采用 NAND 门构建:

JK触发器基本电路

JK 触发器的 J 和 K 输入可用于设置、复位或切换输出,如下所示:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?