大学期间开始的第二个项目实习,这次是利用Altera MAX+plus Ⅱ设计一个简单的CISC模型机,能实现计算机简单的逻辑运算功能。

设计选题

- 设计题目

输入5个有符号整数(8位二进制补码表示),求最大负数的绝对值并输出显示。 - 开发环境

Altera MAX+plus Ⅱ - 设计完成的内容

(1)完成系统的总体设计,画出模型机数据通路框图;

(2)设计微程序控制器(CISC模型计算机)的逻辑结构框图;

(3)设计机器指令格式和指令系统;

(4)设计时序产生器电路;

(5)设计所有机器指令的微程序流程图;

(6)设计操作控制器单元;在CISC模型计算机中,设计的内容包括微指令格式(建议采用全水平型微指令)、微指令代码表(根据微程序流程图和微指令格式来设计)和微程序控制器硬件电路(包括地址转移逻辑电路、微地址寄存器、微命令寄存器和控制存储器等。具体电路根据微程序控制器的逻辑结构框图、微指令格式和微指令代码来设计)。

(7)设计模型机的所有单元电路,并用VHDL语言(也可使用GDF文件----图形描述文件)对模型机中的各个部件进行编程,并使之成为一个统一的整体,即形成顶层电路或顶层文件;

(8)由给出的题目和设计的指令系统编写相应的汇编语言源程序;

(9)根据设计的指令格式,将汇编语言源程序手工转换成机器语言源程序,并将其设计到模型机中的ROM中去;

(10)使用EDA软件进行功能仿真,要保证其结果满足题目的要求;(其中要利用EDA软件提供的波形编辑器,选择合适的输入输出信号及中间信号进行调试。)

(11)器件编程,并在EDA实验平台上进行操作演示。 - 设计基本要求

要求掌握CISC模型机的组成和工作原理(CISC模型机可以是任何计算机组成原理教材上的结构图),学会Altera MAX+plus Ⅱ或Quartus Ⅱ EDA软件的使用,能用EDA软件设计一个能完成一定功能的模型计算机,并通过功能仿真和在EDA实验平台上运行一个程序来验证模型机设计的正确性。

系统总体设计

- 设计模型机通路框图

- 设计控制器的逻辑结构框图

- 设计机器指令格式和指令系统

说明:15-12位作为指令的操作码字段,11-10位属于源寄存器(Rs),而9-8位属于目的寄存器(Rd),7-0位后八位则是模型机立即数,采用定点整数补码表示。

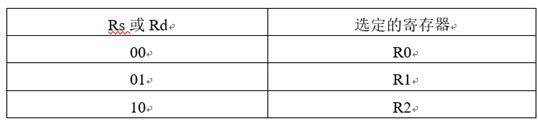

对Rs和Rd的规定:

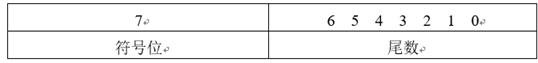

模型机规定数据的表示采用定点整数的补码形式表示,单字长为8位:

- 设计时序产生器电路

T1,T2,T3,T4与CLR,Q之间的关系图:

- 设计微程序流程图

- 设计操作控制器单元

(1)设计微指令格式和微指令代码表

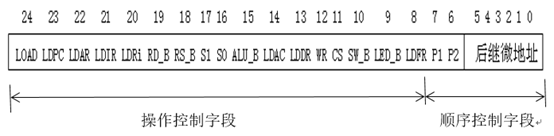

CISC模型机系统使用的微指令采用全水平型微指令,字长为25位,其中微命令字段为17位,P字段为2位,后继微地址为6位,其格式如下:

微指令格式中的后继微地址从左到右以此为μA5,μA4,μA3,μA2,μA1和

μA0。

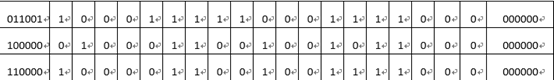

由微指令格式和微程序流程图编写的微指令代码表如下所示, 在微指令的代码表中微命令字段从左边到右代表的微命令信号依次为:LOAD、LDPC、LDAR、LDIR、LDRi、RD_B、RS_B、S1、S0、ALU_B、LDAC、LDDR、WR、CS、SW_B、LED_B、LDFR。

(2)设计地址转移逻辑电路

地址转移逻辑电路是根据微程序流程图中的棱形框部分及多个分支微地址,利用微地址寄存器的异步置“1”端,实现微地址的多路转移。由于是采用逻辑电路来实现的,故而称之为地址转移逻辑电路。在微地址流程图中,P(1)(高电平有效)测试时,根据指令的操作I7~I4强制修改后继地址的低四位;在P(2)(高电平有效)时,根据状态条件进行2路分支,并且都在T4内形成后继微指令的微地址。

SE5=FS·P(2)·T4

SE4=I7·P(1)·T4

SE3=I6·P(1)·T4

SE2=I5·P(1)·T4

SE1=I4·P(1)·T4 - 设计嵌入式CISI模型计算机的顶层电路图

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?