1. 编译 riscv-gnu-toolchain

1.1 预备环境

$ sudo apt-get install autoconf automake autotools-dev curl python3 libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev libexpat-dev1.2 下载源代码

https://github.com/riscv-collab/riscv-gnu-toolchain

git clone --recursive https://github.com/riscv-collab/riscv-gnu-toolchain.git1.3 编译elf 工具

cd riscv-gnu-toolchain/

for riscv64-unknown-elf-gcc:

./configure --prefix=/opt/riscv

sudo make -j1.4 编译 linux 工具

for riscv64-unknown-linux-gnu-gcc:

./configure --prefix=/opt/riscv --enable-multilib

sudo make linux -j

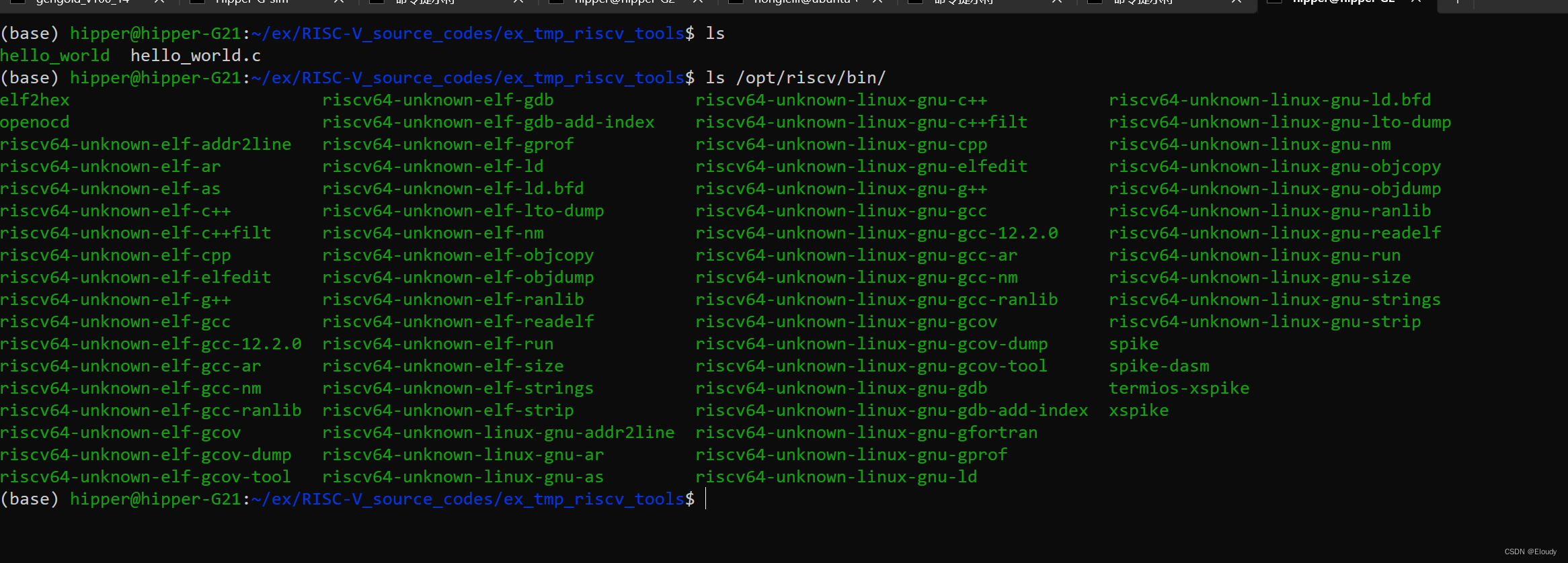

export PATH=/opt/riscv/bin:$PATH2. 编译 riscv-tools

for Spike, the ISA simulator:

2.1 预备环境

$ sudo apt-get install autoconf automake autotools-dev curl libmpc-dev libmpfr-dev libgmp-dev libusb-1.0-0-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev device-tree-compiler pkg-config libexpat-dev

$ sudo apt-get install device-tree-compiler2.2 下载代码

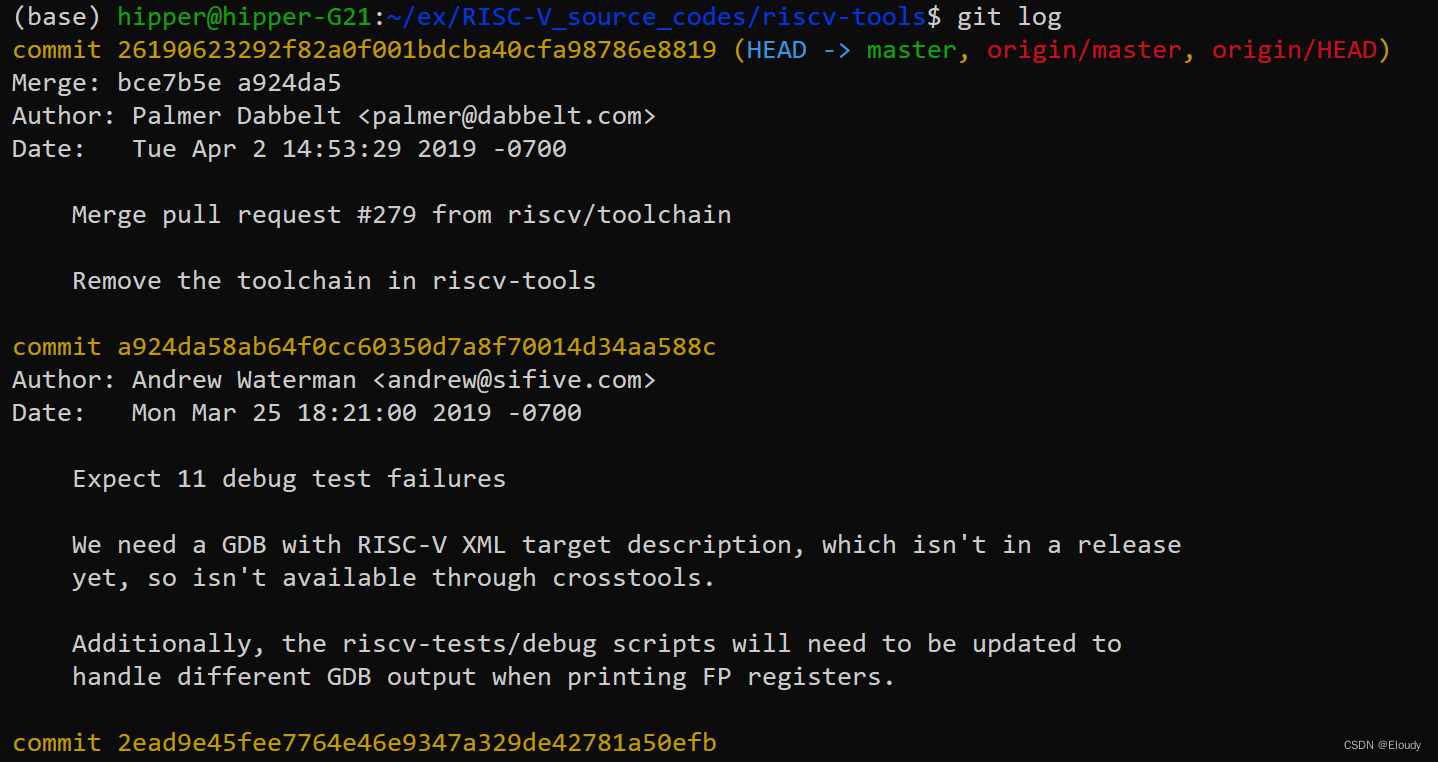

https://github.com/riscv-software-src/riscv-tools

git clone --recursive https://github.com/riscv-software-src/riscv-tools.git 2.3 编译并处理编译错误

cd riscv-tools \

&& git submodule update --init --recursive \

&& export RISCV=/opt/riscv \

&& sudo ./build.sh

-1. 设置了PATH

export PATH=/opt/riscv/bin:$PATH

0. 指定安装目录

第一行加入RISCV

vim build.sh

RISCV=/opt/riscv1. 重复定义变量

/home/hipper/ex/RISC-V_source_codes/riscv-tools/riscv-openocd/build/../src/jtag/drivers/bitbang.h:60: multiple definition of `bitbang_swd';

//LL:: 60 line 注释掉 .h 文件中的这个变量定义声明2. 忘记包含头文件

../fesvr/dtm.cc:488:16: error: ‘runtime_error’ is not a member of ‘std’

vim riscv-isa-sim/fesvr/dtm.cc

#include <stdexcept>3. 忘记包含头文件

../riscv/devices.h:45:18: error: ‘runtime_error’ is not a member of ‘std’

vim riscv-isa-sim/riscv/devices.h

#include <stdexcept>4. 指定架构 rv64gc_zifencei

../machine/flush_icache.c:4: Error: unrecognized opcode `fence.i', extension `zifencei' required

vim ./riscv-tools/build.sh

CC= CXX= build_project riscv-pk --prefix=$RISCV --host=riscv64-unknown-elf --with-arch=rv64gc_zifencei

5.

multiple definition of `tohost'; /tmp/ccMXpCzH.o:(.sbss+0x10): first defined here

extern

6.

multiple definition of `fromhost'; /tmp/ccMXpCzH.o:(.sbss+0x8): first defined here

extern

3. 示例

3.1 源码 example:

用如下编译器指示语句包一下

#pragma GCC push_options

#pragma GCC optimize ("no-tree-loop-distribute-patterns")

... ...

#pragma GCC pop_options

#include <stdio.h>

#pragma GCC push_options

#pragma GCC optimize ("no-tree-loop-distribute-patterns")

int main(void)

{ //printf("Hello RISC-V World!\n");

int a = 2;

int b = 3;

int c = 2;

c = a+b;

printf("c=%d\n", c);

return 0;

}

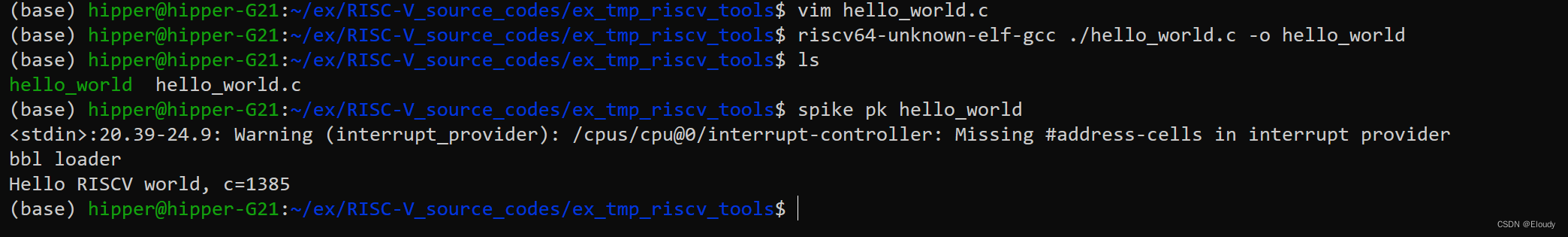

#pragma GCC pop_options3.2 编译示例

$ riscv64-unknown-elf-gcc ./hello_world.c -o hello_world

$ spike pk ./hello_world3.3 运行

$ spike pk ./hello_world

<stdin>:20.39-24.9: Warning (interrupt_provider): /cpus/cpu@0/interrupt-controller: Missing #address-cells in interrupt provider

bbl loader

c=5

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/ex_tmp_riscv_tools$

大家都这么来建立测试c代码文件:

$echo -e '#include <stdio.h>\n int main(void) { printf("Hello RISC-V World!\\n"); return 0; }' > hello_world.c参考文件:

./riscv-tools/regression.sh

4. 显摆显摆成果

一些git diff的输出:

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/riscv-tools$ git diff

diff --git a/build.sh b/build.sh

index 2ebe825..1ba0fe7 100755

--- a/build.sh

+++ b/build.sh

@@ -3,6 +3,7 @@

# Script to build RISC-V ISA simulator, proxy kernel, and GNU toolchain.

# Tools will be installed to $RISCV.

+RISCV=/opt/riscv

. build.common

echo "Starting RISC-V Toolchain build process"

@@ -19,7 +20,7 @@ check_version autoconf 2.64 "OpenOCD build"

build_project riscv-openocd --prefix=$RISCV --enable-remote-bitbang --enable-jtag_vpi --disable-werror

build_project riscv-isa-sim --prefix=$RISCV

-CC= CXX= build_project riscv-pk --prefix=$RISCV --host=riscv64-unknown-elf

+CC= CXX= build_project riscv-pk --prefix=$RISCV --host=riscv64-unknown-elf --with-arch=rv64gc_zifencei

build_project riscv-tests --prefix=$RISCV/riscv64-unknown-elf

echo -e "\\nRISC-V Toolchain installation completed!"

diff --git a/riscv-isa-sim b/riscv-isa-sim

--- a/riscv-isa-sim

+++ b/riscv-isa-sim

@@ -1 +1 @@

-Subproject commit 2710fe575e7e6a4e2418224f8d254d5ca31f6c0e

+Subproject commit 2710fe575e7e6a4e2418224f8d254d5ca31f6c0e-dirty

diff --git a/riscv-openocd b/riscv-openocd

--- a/riscv-openocd

+++ b/riscv-openocd

@@ -1 +1 @@

-Subproject commit 35eed36ffdd082f5abfc16d4cc93511f6e225284

+Subproject commit 35eed36ffdd082f5abfc16d4cc93511f6e225284-dirty

diff --git a/riscv-tests b/riscv-tests

--- a/riscv-tests

+++ b/riscv-tests

@@ -1 +1 @@

-Subproject commit 79064081503b53fdb44094e32ff54a3ab20a9bf2

+Subproject commit 79064081503b53fdb44094e32ff54a3ab20a9bf2-dirty

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/riscv-tools$

____________________________________________________________________________

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/riscv-tools$ cd riscv-openocd/

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/riscv-tools/riscv-openocd$ git diff

diff --git a/src/jtag/drivers/bitbang.h b/src/jtag/drivers/bitbang.h

index 577717ebd..32eb69f53 100644

--- a/src/jtag/drivers/bitbang.h

+++ b/src/jtag/drivers/bitbang.h

@@ -57,7 +57,7 @@ struct bitbang_interface {

void (*swdio_drive)(bool on);

};

-const struct swd_driver bitbang_swd;

+//LL:: const struct swd_driver bitbang_swd;

extern bool swd_mode;

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/riscv-tools/riscv-openocd$

____________________________________________________________________________

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/riscv-tools$ cd riscv-isa-sim/

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/riscv-tools/riscv-isa-sim$ git diff

diff --git a/fesvr/dtm.cc b/fesvr/dtm.cc

index 5409321a..7c8f83c8 100644

--- a/fesvr/dtm.cc

+++ b/fesvr/dtm.cc

@@ -6,7 +6,7 @@

#include <string.h>

#include <assert.h>

#include <pthread.h>

-

+#include <stdexcept>

#define RV_X(x, s, n) \

(((x) >> (s)) & ((1 << (n)) - 1))

#define ENCODE_ITYPE_IMM(x) \

diff --git a/riscv/devices.h b/riscv/devices.h

index 4e4d27ff..aee50892 100644

--- a/riscv/devices.h

+++ b/riscv/devices.h

@@ -6,7 +6,7 @@

#include <string>

#include <map>

#include <vector>

-

+#include <stdexcept>

class processor_t;

class abstract_device_t {

(base) hipper@hipper-G21:~/ex/RISC-V_source_codes/riscv-tools/riscv-isa-sim$

____________________________________________________________________________

参考:

最后解决example 代码包裹问题,借鉴了这位仁兄的记录,发现遇到的问题也如出一辙:

343

343

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?