-1,PCIe specification

官网下载需要注册该集团的企业id,

7.0已经出来了,下面 update 到从6.0

PCI Express® Base Specification Revision 6.0

base 6.0

https://pan.baidu.com/s/1kUrho2M7hRJeCNXSxwLN8A?pwd=7zkx

pwd=7zkx

base 5.0

https://pan.baidu.com/s/1aqRrbmR7dNO3gHz3Q3kF0Q

提取码:62b8

4.0

http://pan.baidu.com/s/1dFxqX9Z

3.0

链接:https://pan.baidu.com/s/1lydqD_SiS54bq7Zyz9VsCA

提取码:evpx

2.0

https://www.intel.com/content/dam/support/us/en/programmable/support-resources/fpga-wiki/asset03/pci-express-base-r2.1.pdf

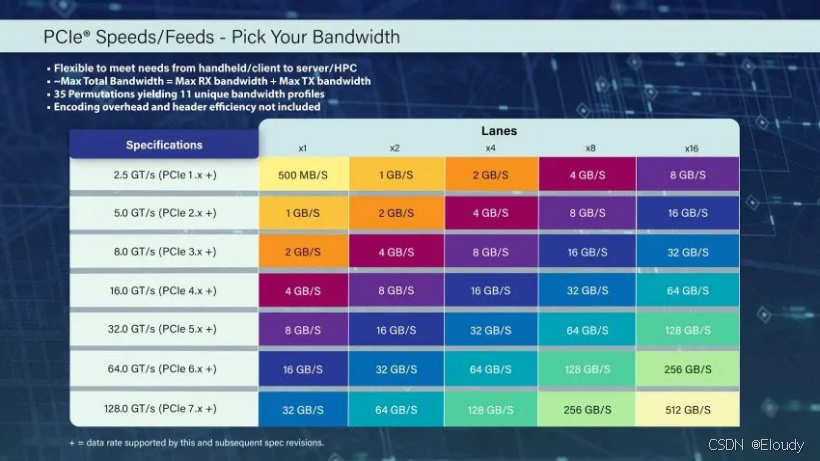

各代带宽:

0,总体Topology

x86 处理器系统中 PCIe的拓扑结构:

PCIe Switch的总体结构

1,PCIe 枚举

BIOS 负责枚举与分派配置设备的 BusID[7:0] : DeviceID[4:0] : FunctionID[2:0];

cpu先识别 Host-PCI-Bridge,其下是Bus0;

在Host-PCI-Bridge 的Bus0下会链接几个固定的 Virtual P2P 节点,CPU出厂前就定义完了,融合在 CPU 的 RootComplex中,类似集成了几个以前的pci桥。

第一个 Virtual下边是Bus1,Bus1下可以链接一个EP或者也给PCIe-SWITCH,内含多个 Virtual P2P,每个P2P都可以延伸出一条 Bus,每个Bus下面要么挂一个EP,要么挂一个PCIe-SWITH,l来衍生出更多Bus。

cpu通过挨家挨户虚拟敲门的方式来探测BUS和其下之设备或总线的存在的可能性。

探测存在后,cpu在根据策略来分配 BUS-id,Device-id,Function-id等,通过配置事务传递对应的PCIe实体,它们会记住自己的id。

这是一个深度优先的过程。

下边是一个分配好配置信息的Xilin的FPGA板卡的信息,使用TeleScanPE软件在Linux上采集了内核的相关的PCIe信息。

2,PCIe 设备 Type0 配置空间

作用:用于EP的描述,每个PCIe的设备的每个Function包含一个Type0的配置空间。

读了Type0的值之后,便可以知道这个设备的功能的类属:网卡,显卡,声卡,。。。这由PCI-SIG来分类定义,参考规范:

《PCI Local Bus Specification Revision 3.0》

《PCI Code and ID Assignment Specification》

必须由RC来读写 Function的 Type0的寄存器。

其配置寄存器信息如下,每个Function 对应一张这样的寄存器 空间表:

还有256 Bytes 之后的扩展配置空间,可以加入一些产品个性化的配置信息:

4042

4042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?