个人爱好写一下,能力有限,文章难免错误,仅供参考和学习。

1 电灯泡

众所周知,爱迪生(Thomas Edison)在1883年发明了电灯。

2 电子管

这个是以前在HIFI音响的时候时不时看到,江湖诨号的“胆机”。不过一直没懂电子管这玩意是干嘛的。最近在看硬件知识,所以大概懂了一些。

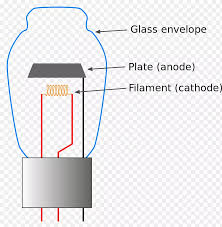

原来这玩意也是源于爱迪生发明的电灯。。。当年爱迪生在试验各种电灯的材质时,有一种实验出现了电流的效应。也就是在灯泡中额外放置一个金属板(阳极),当灯丝(阴极)加热且阳极带正电时,会产生电流。当时爱迪生仅仅注意到了,并未对这个现象深入研究。

后面爱迪生公司的员工弗莱明(John Ambrose Fleming),注意到了这个现象,在1904年将这个特性用于无线电。也就是真空二极管。

此时,真空二极管的主要作用就是整流,利用单向导通的特性来实现无线电报的检波。

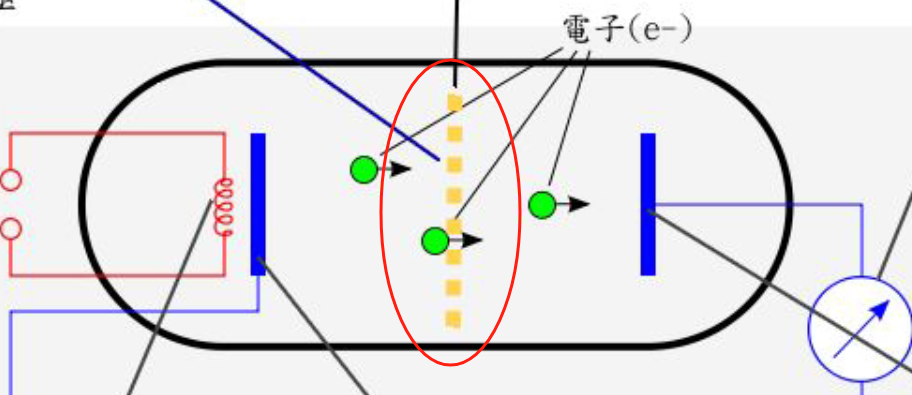

在单机的无线电报完善之后,后面就是无线电报网络,主要就是要解决远距离信号衰减需要放大的问题。这时就诞生了电子三极管。

发明人是德福雷斯特(Lee De Forest),时间是1906年。本质就是在中间增加了一个电路板栅极,通过给这个栅极施加电压来控制两端的电流。于是原始信号就作为栅极上的电压,这样就实现了放大的两端电流电压。。

3 晶体管

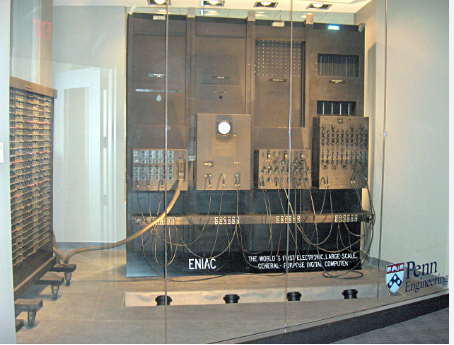

电子管虽然解决了从无到有的过程,但是本身有很多缺陷。体积大、功耗高、易碎、寿命短。第一台电脑ENIAC(Electronic Numerical Integrator and Computer)就是电子管做的,随时都有里面的电子管坏掉。

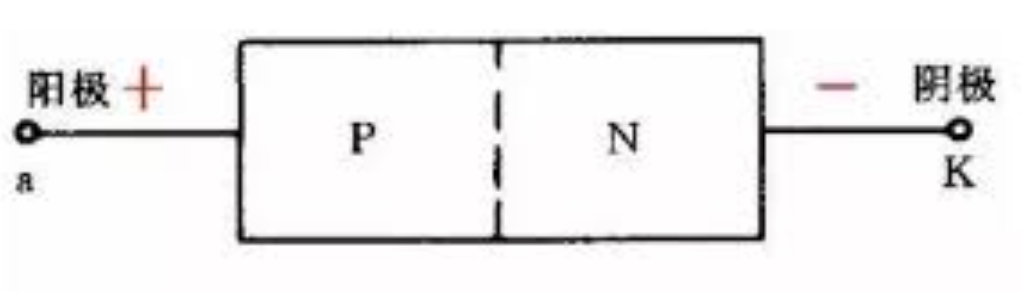

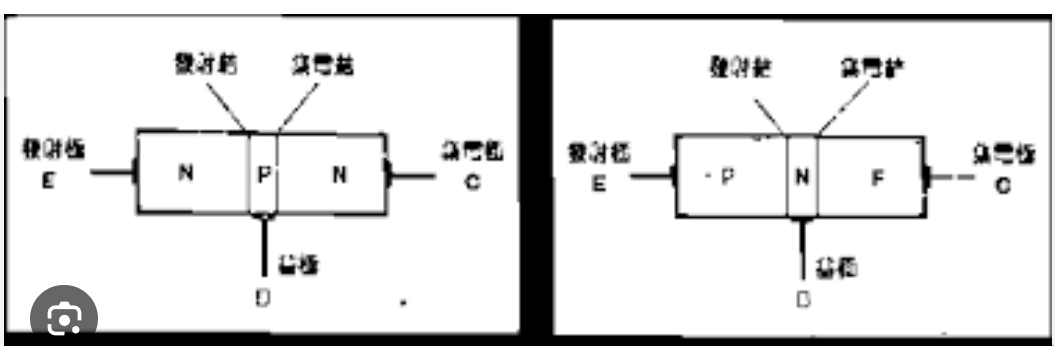

在1920年代,科学家发现硅(Si)和锗(Ge)等材料的导电性介于导体与绝缘体之间。二战结束后1947年,贝尔实验室成立了半导体小组。巴丁和布拉顿用锗晶体、金箔和塑料楔子制作出首个点接触晶体管。肖克利(William Shockley)于1948年提出结型晶体管(Bipolar Junction Transistor, BJT)理论。 结构:由P-N-P或N-P-N三层半导体组成,通过“基极”电流控制“集电极-发射极”电流。

**贝尔实验室(Bell Labs)** 是美国历史上最具影响力的工业研究机构之一,成立于1925年,由AT&T和西方电气公司共同创立。作为通信与电子技术的摇篮,贝尔实验室孕育了众多划时代的发明,包括**晶体管(1947年)**、**激光(1958年)**、**UNIX操作系统(1969年)**和**光纤通信技术**等,共获得9项诺贝尔奖。其创新不仅奠定了现代信息技术的基础,还推动了从电话网络到互联网的全球通信革命。尽管21世纪后规模缩减,但其“基础研究+应用开发”的模式至今仍是科技创新的典范。

由此,晶体管几乎完全取代了电子管。同时,晶体管的特性也让大规模集成成为了可能。

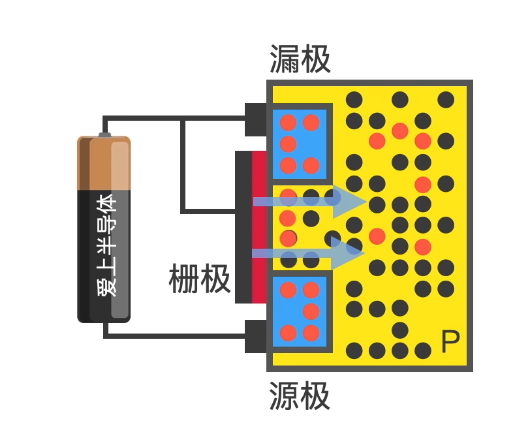

1940年前后,绝缘栅场效应的理论开始出现,在1960年,还是贝尔实验室(真是伟大!),由姜大元(Dawon Kahng)和马丁·阿塔拉(Martin Atalla)制造了MOS管。1963年仙童半导体发明的CMOS(互补MOS)结合N-MOS和P-MOS。

CMOS静态功耗接近零(仅动态切换时耗电),抗噪声能力强,适合大规模逻辑电路,与硅平面工艺完美契合,可批量生产。所以MOS管成为了现代CPU的基石。现在一个CPU几乎99%都是由MOS构成。

4 计算机

上面说过第一台电脑ENIAC(Electronic Numerical Integrator and Computer)就是电子管做的,那么具体是怎么实现的呢?

首先还是理论。1937年,克劳德·香农(Claude Shannon)的硕士论文《继电器与开关电路的符号分析》中,证明布尔代数可以通过继电器开关电路实现逻辑运算。提出了用“真/假”(1/0)对应电路的“开/关”状态,将逻辑门(如AND、OR)物理化。

ENIAC是1943年由宾夕法尼亚大学的工程师完成,此时已经隐含了布尔逻辑(如加法器、触发器),但是理论尚不完善。

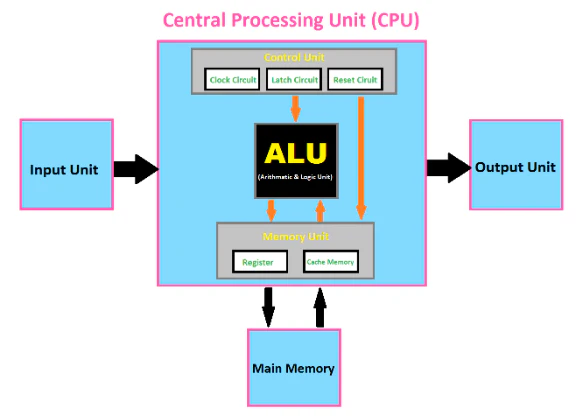

1945年,冯·诺依曼(John von Neumann)完善了这一结构。在《EDVAC报告》中提出“存储程序”计算机架构,明确要求使用逻辑门(如与、或、非)构建算术逻辑单元(ALU)和控制单元。改进了ENIAC并实现了新一代的EDVAC(Electronic Discrete Variable Automatic Computer)。EDVAC也就是现在真正意义的计算机了。

4.1 逻辑门

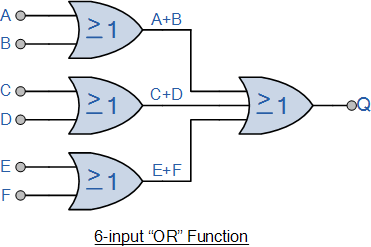

逻辑门是计算机的“最小计算单元”。通过组合三极管,可构建基本逻辑门。

1 非门(NOT Gate)

结构:1个MOSFET + 电阻(或CMOS互补结构)。

功能:输入1 → 输出0,输入0 → 输出1。

2 与非门(NAND Gate)

结构:2个NMOS串联 + 2个PMOS并联(CMOS工艺)。

功能:仅当所有输入为1时输出0,否则输出1。

意义:NAND门是通用逻辑门,可组合实现任何复杂计算。

3 或非门(NOR Gate)

结构和与非门类似,但NMOS并联、PMOS串联。

4.2 功能模块

多个逻辑门可以构成功能模块。算术逻辑单元(ALU),控制单元(CU),寄存器组(Registers)等等。

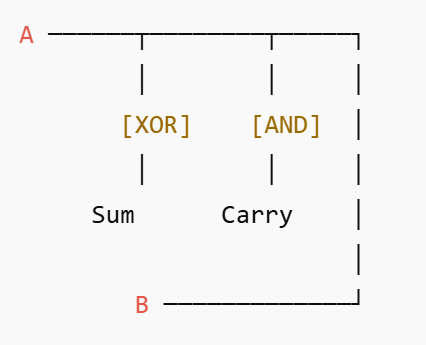

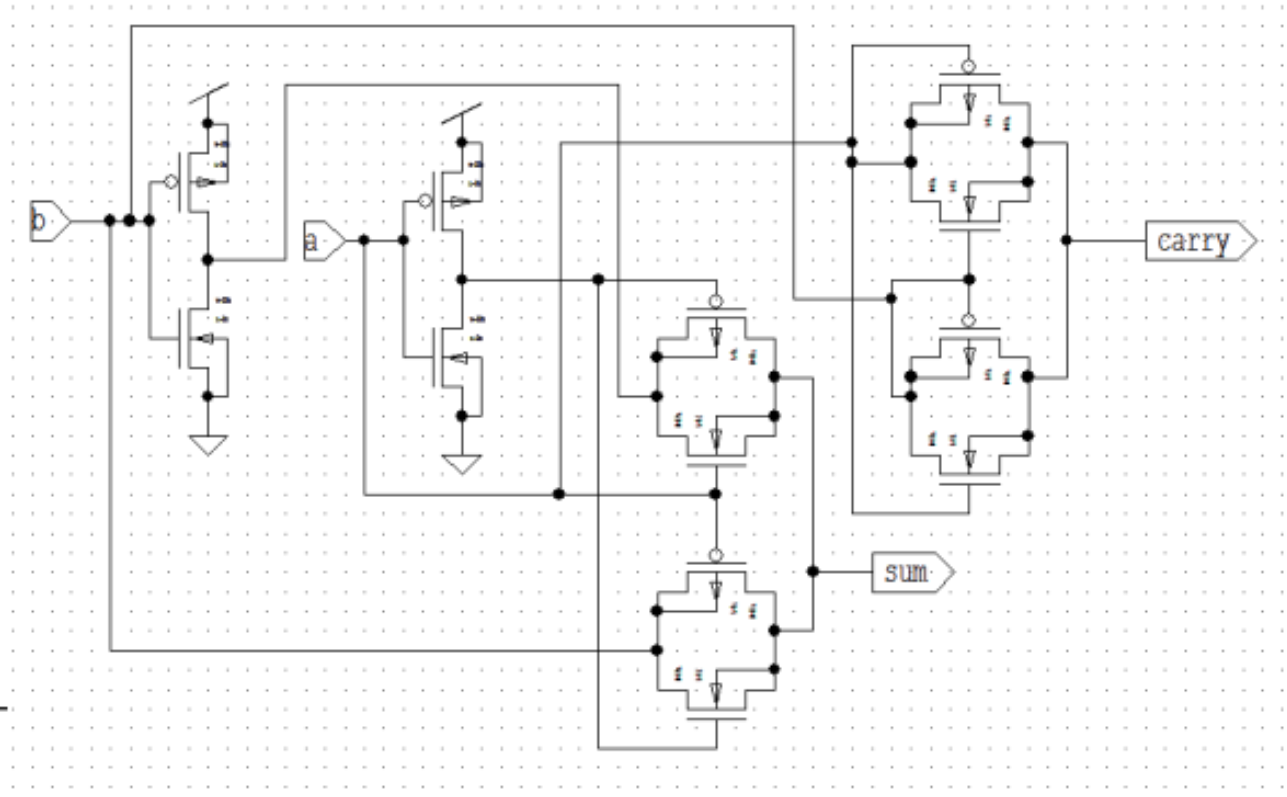

这里就简单说一下ALU中的简单加法器(Half Adder)。

要实现二进制的A+B可以采用如下架构。

真值表如下。

| A | B | Sum | Carry | 解释 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 + 0 = 0(无进位) |

| 0 | 1 | 1 | 0 | 0 + 1 = 1(无进位) |

| 1 | 0 | 1 | 0 | 1 + 0 = 1(无进位) |

| 1 | 1 | 0 | 1 | 1 + 1 = 10(进位1) |

其中,

AND门需要通过NAND门 + 非门组合实现。

XOR门需要更复杂的MOS管组合,基于NAND、NOR和NOT的组合。XOR是非线性逻辑,需更多MOS管(通常8-12个),因此芯片中XOR比NAND/OR更占面积。

整体CMOS电路如下(供参考):

这样无数个mos管构成无数个逻辑门,无数个逻辑门构成功能模块,功能模块垒起来,就可以完成复杂的功能,就形成了现在的芯片CPU。。

5 参考

Design of CMOS Half adder ||step by step process || Explore the way

https://www.researchgate.net/figure/Schematic-diagram-of-existing-half-adder-using-Static-CMOS-technique_fig3_320557527 https://www.researchgate.net/figure/Half-adder-circuit-using-TG_fig9_304353741

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?