基于FPGA的VGA图像显示

前言:

本文主要介绍了基于FPGA的VGA图像显示原理及操作过程。使用的软件是Quartus Ⅱ,该实验使用fpga芯片为cyclone IV EP4CE115F29C7。

1. VGA显示原理

VGA,英文全称“Video Graphics Array”,译为视频图形阵列,是一种使用模拟信号进行视频传输的标准协议,由IBM公司于1987年推出,因其分辨率高、显示速度快、颜色丰富等优点,广泛应用于彩色显示器领域。

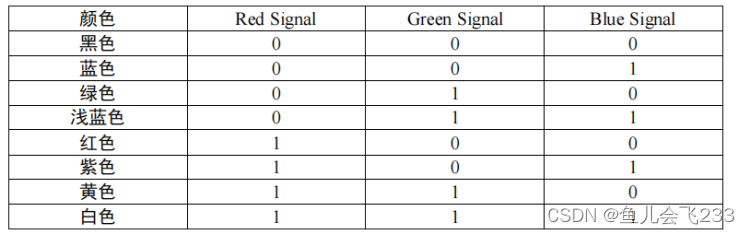

分为:RGB565,RGB332, RGB888—RBG总共24位,其中每种色8位,总2^24次方。

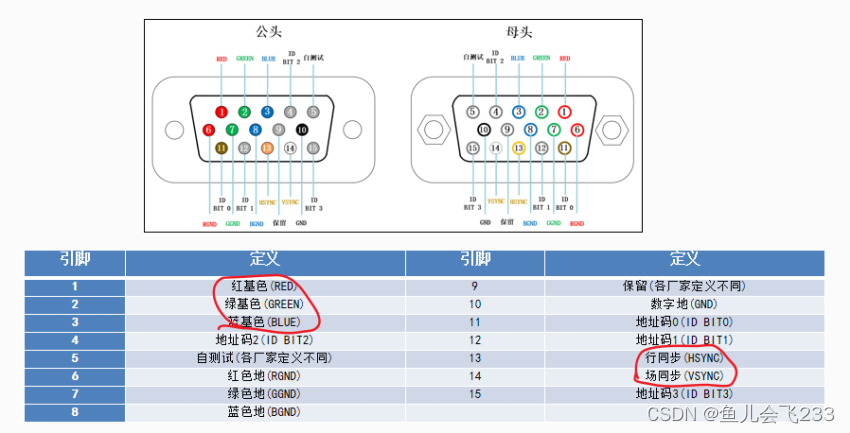

1.1 VGA接口及引脚定义

上图为VGA引脚图,其中最主要的就是引脚1,2,3实现RGB三色输出,引脚13,14实现时钟同步与数据输出控制。

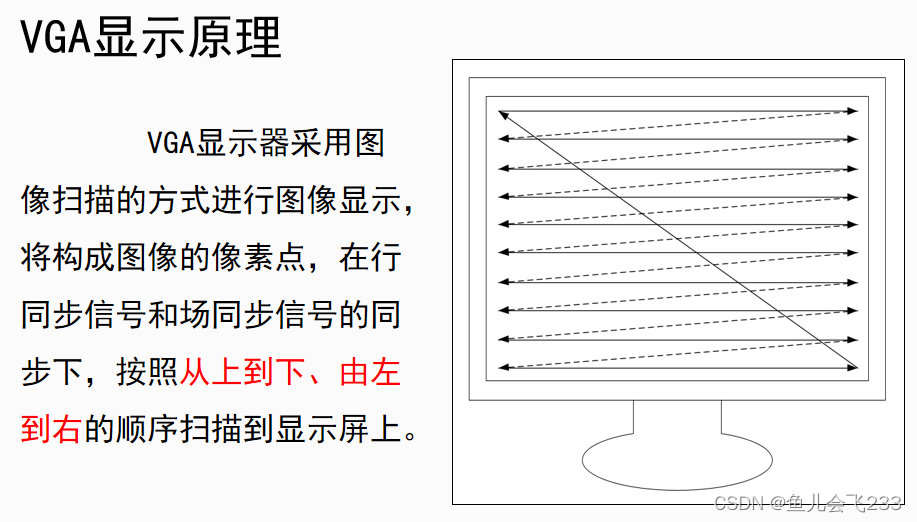

1.2 VGA显示原理

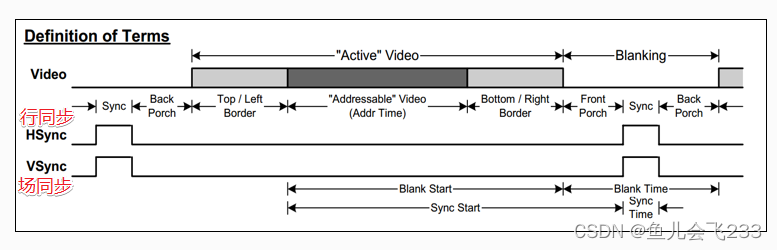

1.3 VGA时序标准

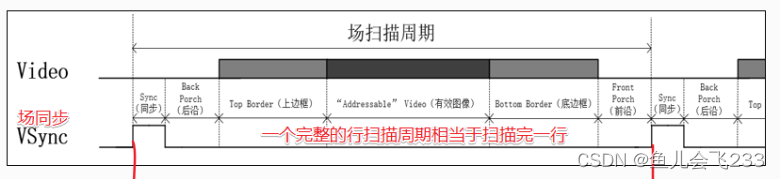

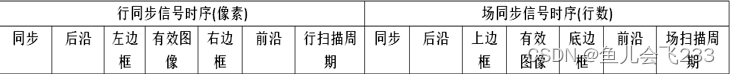

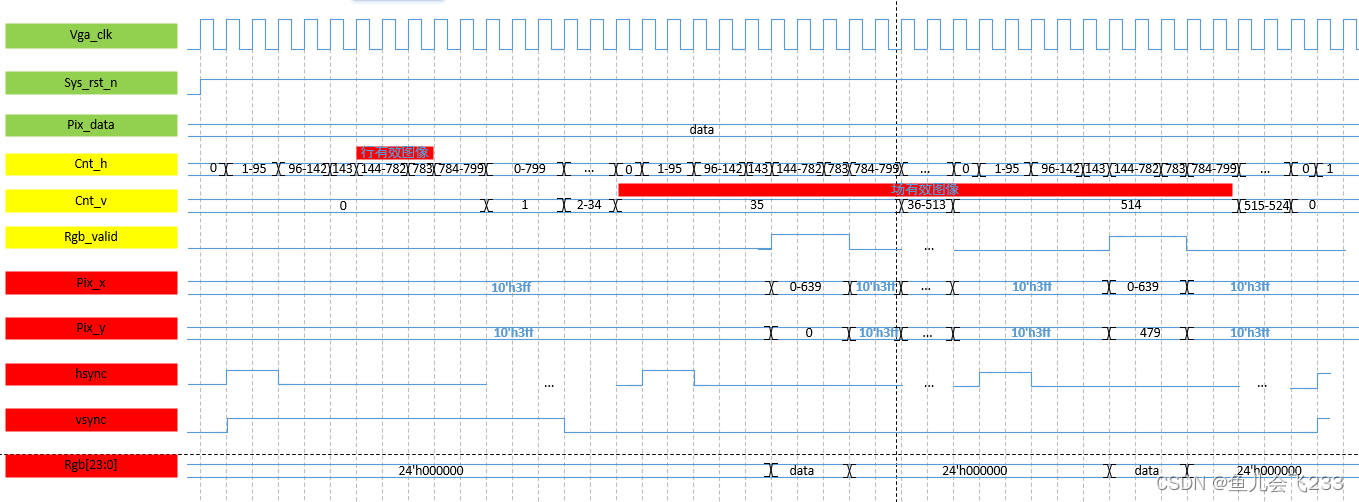

下图为VGA时序标准波形图,只有当行同步与场同步信号同时有效时才控制数据输出,需要注意的是两者时间是不等同的,下文逐一介绍。

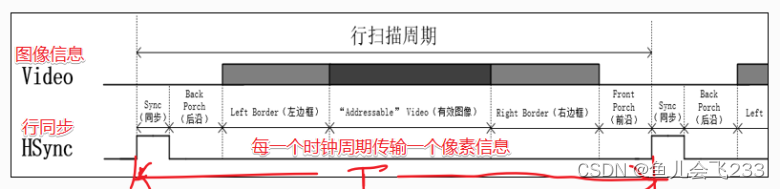

每一个时钟周期传输一个像素信息,时钟周期即VGA显示工作时钟。

每一个行扫描周期相当于扫描完一行, 行-屏幕行

每一个场扫描周期相当于扫描完整个屏幕,场-屏幕列

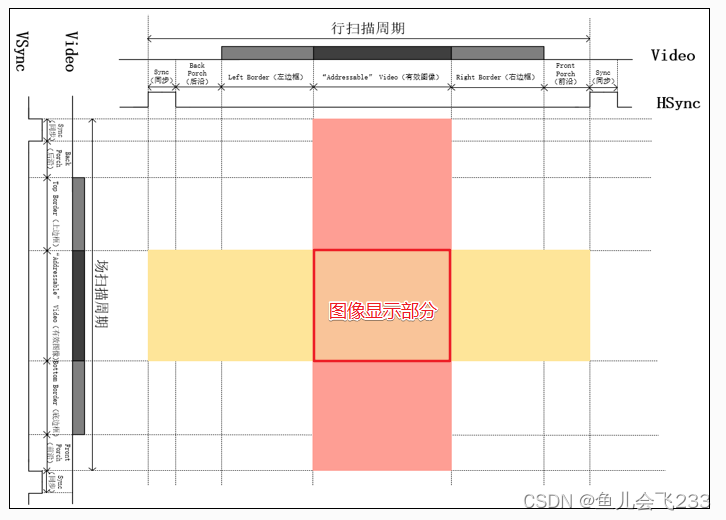

上图中六个部分与下图各部分一一对应。

具体实现过程如下图所示:

可以看到,只有当行扫描周期与场扫描周期都处于有效图像时序部分才产生图像。

1.4 VGA显示模式及相关参数

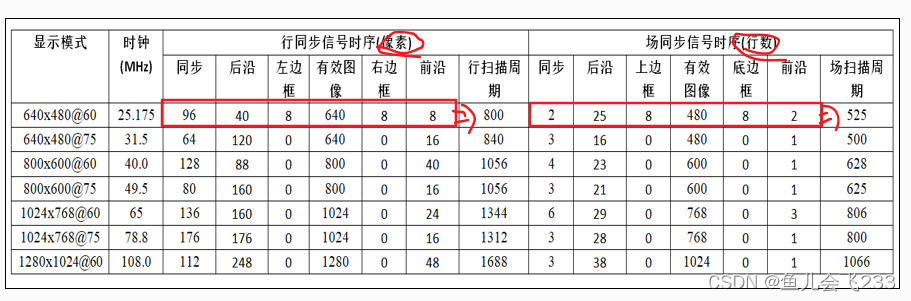

下图为VGA显示模式显示模式选择。本次实验选择640x480@60

即每一行640像素点,一帧完整图像有480行 @60表示每秒显示60帧图像

时钟设计:VGA显示工作时钟/像素点扫描频率,即完成一个像素点扫描的频率

F= 行扫描周期x场扫描周期x帧率

=800* 525* 60 ==25_200_000 取25MHZ

1.5 RGB888颜色合成

parameter WHITE = 24'hFFFFFF, //白色

BALCK = 24'h000000, //黑色

RED = 24'hFF0000, //红色

ORANGE = 24'hFF8800, //橙色

YELLOW = 24'hFFFF00, //黄色

GREEN = 24'h00FF00, //绿色

CYAN = 24'h00FFFF, //青色

BLUE = 24'h0000FF, //蓝色

PURPLE = 24'hFF00FF, //紫色

GRAY = 24'hC0C0C0; //灰色

2. VGA模块设计

2.1 顶层模块vga_colorbar

`timescale 1ns/1ns

module vga_colorbar

(

input wire sys_clk , //输入工作时钟,频率50MHz

input wire sys_rst_n , //输入复位信号,低电平有效

output wire hsync , //输出行同步信号

output wire vsync , //输出场同步信号

output wire [23:0] rgb , //输出像素信息

output wire vga_clk_dis , //vga引脚时钟 跟vga_clk同步反向

output wire disp_vld //背光开启标志

);

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//wire define

wire vga_clk ; //VGA工作时钟,频率25MHz

wire locked ; //PLL locked信号

wire rst_n ; //VGA模块复位信号

wire [9:0] pix_x ; //VGA有效显示区域X轴坐标

wire [9:0] pix_y ; //VGA有效显示区域Y轴坐标

wire [23:0] pix_data; //VGA像素点色彩信息

//rst_n:VGA模块复位信号

assign rst_n = (sys_rst_n & locked);

//********************************************************************//

//*************************** Instantiation **************************//

//********************************************************************//

//------------- clk_gen_inst -------------

pll clk_gen_inst (

.areset ( ~sys_rst_n ),//输入复位信号,高电平有效,1bit

.inclk0 ( sys_clk ), //输入50MHz晶振时钟,1bit

.c0 ( vga_clk ),

.locked ( locked ) //输出VGA工作时钟,频率25Mhz,1bit

); //输出pll locked信号,1bit

//------------- vga_ctrl_inst -------------

vga_ctrl vga_ctrl_inst

(

.vga_clk (vga_clk ), //输入工作时钟,频率25MHz,1bit

.sys_rst_n (rst_n ), //输入复位信号,低电平有效,1bit

.pix_data (pix_data ), //输入像素点色彩信息,16bit

.pix_x (pix_x ), //输出VGA有效显示区域像素点X轴坐标,10bit

.pix_y (pix_y ), //输出VGA有效显示区域像素点Y轴坐标,10bit

.hsync (hsync ), //输出行同步信号,1bit

.vsync (vsync ), //输出场同步信号,1bit

.rgb (rgb ), //输出像素点色彩信息,16bit

.vga_clk_dis(vga_clk_dis), //vga引脚时钟

.disp_vld (disp_vld ) //背光开启标志

);

//------------- vga_pic_inst -------------

vga_pic vga_pic_inst

(

.vga_clk (vga_clk ), //输入工作时钟,频率25MHz,1bit

.sys_rst_n (rst_n ), //输入复位信号,低电平有效,1bit

.pix_x (pix_x ), //输入VGA有效显示区域像素点X轴坐标,10bit

.pix_y (pix_y ), //输入VGA有效显示区域像素点Y轴坐标,10bit

.pix_data (pix_data ) //输出像素点色彩信息,16bit

);

endmodule

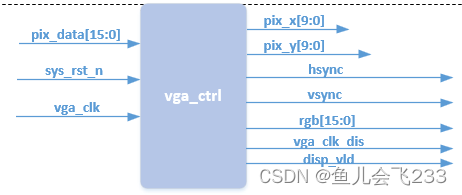

2.2 有效图像坐标信息模块Vga_ctrl

该模块产生有效图像的坐标信息传入图像生成模块vga_pic,然后vga_pic会回传图像数据,接着该模块将传入的图像数据同步在行场同步下输出控制显示。

下图为时序图:

module vga_ctrl

(

input wire vga_clk , //输入工作时钟,频率25MHz

input wire sys_rst_n , //输入复位信号,低电平有效

input wire [23:0] pix_data , //输入像素点色彩信息

output wire [9:0] pix_x , //输出VGA有效显示区域像素点X轴坐标

output wire [9:0] pix_y , //输出VGA有效显示区域像素点Y轴坐标

output wire hsync , //输出行同步信号

output wire vsync , //输出场同步信号

output wire [23:0] rgb , //输出像素点色彩信息

output wire vga_clk_dis , //vga引脚时钟 跟vga_clk反向

output wire disp_vld //背光开启标志

);

assign vga_clk_dis = ~vga_clk;

//parameter define

parameter H_SYNC = 10'd96 , //行同步

H_BACK = 10'd40 , //行时序后沿

H_LEFT = 10'd8 , //行时序左边框

H_VALID = 10'd640 , //行有效数据

H_RIGHT = 10'd8 , //行时序右边框

H_FRONT = 10'd8 , //行时序前沿

H_TOTAL = 10'd800 ; //行扫描周期

parameter V_SYNC = 10'd2 , //场同步

V_BACK = 10'd25 , //场时序后沿

V_TOP = 10'd8 , //场时序上边框

V_VALID = 10'd480 , //场有效数据

V_BOTTOM = 10'd8 , //场时序下边框

V_FRONT = 10'd2 , //场时序前沿

V_TOTAL = 10'd525 ; //场扫描周期

reg [11:0] cnt_h;//行同步计数器

reg [11:0] cnt_v;//场同步计数器

wire rgb_valid;

//cnt_h 行同步计数器

always@(posedge vga_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt_h <= 12'd0;

else if(cnt_h == H_TOTAL-1'd1)

cnt_h <= 12'd0;

else

cnt_h <= cnt_h + 1'd1;

//hsync:行同步信号

assign hsync = (cnt_h <= H_SYNC - 1'd1) ? 1'b1 : 1'b0 ;

//cnt_v 场同步计数器

always@(posedge vga_clk or negedge sys_rst_n)

if(!sys_rst_n)

cnt_v <= 12'd0;

else if((cnt_v == V_TOTAL-1'd1) && (cnt_h == H_TOTAL-1'd1))

cnt_v <= 12'd0;

else if(cnt_h == H_TOTAL-1'd1)

cnt_v <= cnt_v + 1'd1;

//vsync:场同步信号

assign vsync = (cnt_v <= V_SYNC - 1'd1) ? 1'b1 : 1'b0 ;

//rgb_valid:VGA有效显示区域

assign rgb_valid = ((cnt_h >= (H_SYNC+H_BACK+H_LEFT)) && (cnt_h <= (H_SYNC+H_BACK+H_LEFT+H_VALID-1'd1)) //cnt_h:144-783

&& (cnt_v >= (V_SYNC+V_BACK+V_TOP)) && (cnt_v <= (V_SYNC+V_BACK+V_TOP+V_VALID-1'd1))) //cnt_v:35-514

? 1'b1 : 1'b0;

//pix_x,pix_y:VGA有效显示区域像素点坐标

assign pix_x = (rgb_valid == 1'b1) ? (cnt_h - (H_SYNC+H_BACK+H_LEFT)): 10'h3ff;

assign pix_y = (rgb_valid == 1'b1) ? (cnt_v - (V_SYNC+V_BACK+V_TOP)): 10'h3ff;

//rgb:输出像素点色彩信息

assign rgb = (rgb_valid == 1'b1) ? pix_data : 24'b0 ;

assign disp_vld = (rgb_valid == 1'b1) ? 1'b1 : 1'b0 ;

endmodule

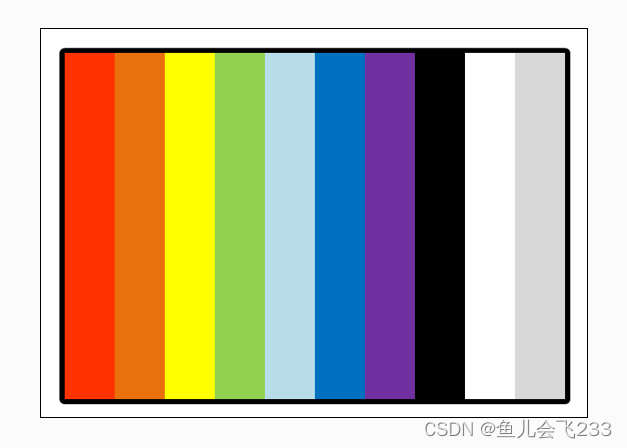

2.3 图像生成模块vga_pic

原理十分简单,即根据Vga_ctrl模块传入的xy坐标确定要显示的位置,然后根据需求对对应位置赋颜色即可。

module vga_pic

(

input wire vga_clk , //输入工作时钟,频率25MHz

input wire sys_rst_n , //输入复位信号,低电平有效

input wire [9:0] pix_x , //输入VGA有效显示区域像素点X轴坐标

input wire [9:0] pix_y , //输入VGA有效显示区域像素点Y轴坐标

output reg [23:0] pix_data //输出像素点色彩信息

);

//parameter define

parameter H_VALID = 10'd640 , //行有效数据

V_VALID = 10'd480 ; //场有效数据

//RGB

parameter WHITE = 24'hFFFFFF, //白色

BALCK = 24'h000000, //黑色

RED = 24'hFF0000, //红色

ORANGE = 24'hFF8800, //橙色

YELLOW = 24'hFFFF00, //黄色

GREEN = 24'h00FF00, //绿色

CYAN = 24'h00FFFF, //青色

BLUE = 24'h0000FF, //蓝色

PURPLE = 24'hFF00FF, //紫色

GRAY = 24'hC0C0C0; //灰色

//0-639 分成8份 80

//pix_data:输出像素点色彩信息,根据当前像素点坐标指定当前像素点颜色数据

always@(posedge vga_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

pix_data <= BALCK;

else

begin

case (pix_x)

10'd0 : pix_data <= WHITE ;

10'd80 : pix_data <= RED ;

10'd160 : pix_data <= ORANGE ;

10'd240 : pix_data <= YELLOW ;

10'd320 : pix_data <= GREEN ;

10'd400 : pix_data <= CYAN ;

10'd480 : pix_data <= BLUE ;

10'd560 : pix_data <= PURPLE ;

default: pix_data <= pix_data ;

endcase

end

endmodule

3. 实验现象

3547

3547

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?