4 总线协议和cache一致性内联

将硬件的一致性扩展到多cluster系统要求一个一致性总线协议。AMBA 4 ACE spec包括AXI一致性扩展ACE。完整的ACE接口使能了cluster之间的硬件一致性和使能了SMP操作可以运行在多core上。

如果你有超过一个cluster,任何在一个cluster上的共享内存访问可以snoop到其他cluster上的cache中来看是否数据在那里,或是否必须从外部内存中加载。AMBA 4 ACE-lite 接口是完整接口的一个子集,它为一路IO一致性master比如DMA引擎,网络接口和GPU。

这些设备可能自己没有cache,但可以从ACE处理器读取共享数据。对于非core的master的cache通常不需要与core的cache一致。比如,在很多系统中core不会snoop到一个GPU的cache中但反过来通常不正确。

ACE-lite允许其他master snoop到其他cluster的cache中。这意味着对于shareable位置,如果有必要,读从一致性cache中被填充,共享的写被与一个来自一致性cache line的强制的clean和无效化合并。ACE spec使能TLB和I cache维护操作,这些操作被广播到有能力接受到它们的设备上。数据barrier被发送到slave接口上来保证它们编程完成。

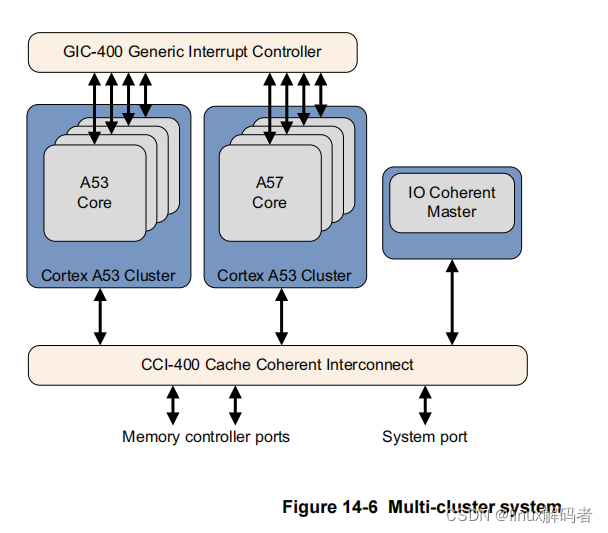

CoreLink CCI-400 Cache一致性接口是AMBA 4 ACE实现的一个并支持2个ACE cluster,它使能了最大8个core看到相同的内存视图并运行SMP操作系统,比如,big.LITTLE比如Cortex-A57和Cortex-A53处理器,如下图:

它也有3个ACE-lite一致性接口可以使用,通过DMA控制器或GPU。

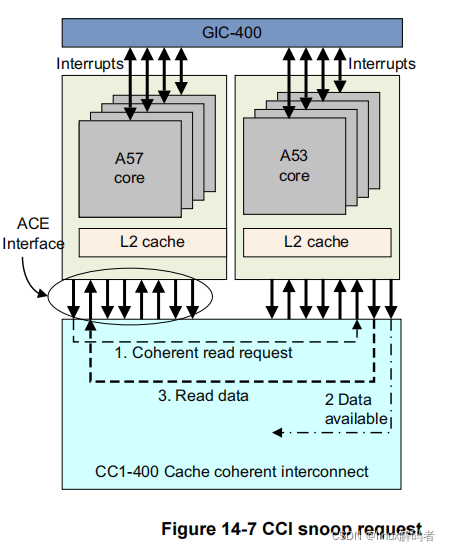

下图显示了一致性数据从Cortex-A53cluster读取到Cortex-A57 cluster。

- Cortex-A53 cluster发出一个一致性读取请求;

- CCI-400将请求传递给Cortex-A53处理器并snoop到Cortex-A57cluster cache;

- 当请求接受到时,Cortex-A57 cluster检查它的数据cache有效性并回复要求的信息;

- 如果要求的数据在cache中,CCI-400将Cortex-A57cluster的数据移动到Cortex-A53 cluster,这导致了在Cortex-A53 cluster中的cache line填充。

CCI-400和ACE协议使能了Cortex-A57和Cortex-A53 cluster的完全一致性,使不需要外部内存事务而使能数据共享。

ARM CoreLink内部互联和内存控制系统IP解决了一些挑战,挑战包括有效的在Cortex-a系列的处理器之间移动和存储数据,高性能media处理器,和动态内存用于优化系统性能和SOC片上功耗。CoreLink系统IP使SOC设计者可以最大化系统内存带宽的利用并减少静态和动态时延。

4.1 计算子系统和移动应用

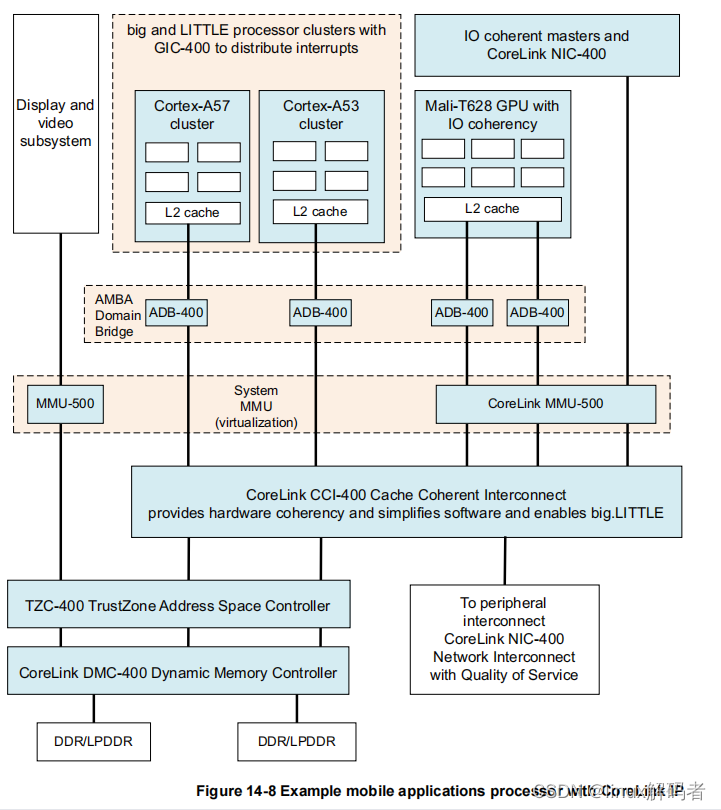

下列图显示了一个带Cortex-A57和Cortex-A53系列的处理器的移动应用的例子,CoreLink MMU-500系统MMU和CoreLink 400系统IP。

在系统中,ARM Cortex-A57和Cortex-A53处理器提供了big.LITTLEcluster的联合并连接到CCI-400 AMBA 4 ACE提供完整的硬件一致性。ARM Mali-T628 GPU和IO一致性master通过AMBA 4 ACElite接口连接到CCI-400。

ARM为维护跨cluster一致性提供了不同的内联选项:

CoreLink CCI-400 cache一致性内联:这可以支持2个多核cluster并使用AMBA 4和AMBA一致性扩展或ACE。ACE使用MOESI状态机用于跨cluster一致性。

CoreLink CCN-504 cache一致性网络:这可以支持4个多核cluster并包含集成L3 cache和2个channel 72bit DDR。

ARM CoreLink CCN-504 cache一致性网络提供系统带宽和延时。CCN系列的内部互联是通过AMAB 5 CHI设计的,虽然有一些支持AMAB 4 ACE。CCN-504提供了AMBA 4 ACE,对多个Cortex-A系列处理器提供了完全的一致性。这个特征是高带宽应用的基础,包括游戏服务器和要求单处理器和多处理器的一致性的网络。

与ARM CoreLink 网络互联和内存控制IP兼容,CCN增加性能和功耗。

CoreLink CCN-508 cache一致性网络:这可以支持8core cluster,32core和包括集成L3 cache和4维护72bit DDR通道。

CoreLink MMU-500系统MMU:这提供了系统的地址转换。

CoreLink TZC-400 TruZone 地址空间控制器:这对内存或外设发出安全检查并允许内存区域被标记为sercure。

CoreLink DMC-400 动态内存控制:这提供了动态内存调度和接口给外部DDR2/3或LPDDR2内存。

CoreLink NIC-400 网络内联:这高可配置并使你创建高性能和优化,AMBA兼容网络组件。对于CoreLink NIC-400网络组件的可能配置可以从一个简单bridge组件转化为复杂的包含128master和64 slave的互联,比如AHB to AXI协议转换桥。

907

907

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?