最近新完成了一个有关CMOS的成像电路,传感器采用比利时CMOSIS公司出的CMV4000图像传感器。CMOSIS是由Cypress公司分离出来的大多数科研人员组成的,公司成立于2008年1月份,总部位于比利时的安特卫普。CMOSIS进行专业图像传感器的设计及生产,致力于医疗、机器视觉、运动分析、空间、生物计量及国防应用提供解决方案。

该公司的标准货架产品列表如下:

| Product | Resolution | Shutter Type | Pixel Size | Optical Format | Frame Rate | Output Interface | Applications |

| 0,3MP - 648(H) x 488(V) | Pipelined global shutter with true CDS | 7.4 x 7.4 μm2 | 1/3'' | 300 fps (10 bit) | 4 LVDS outputs @ 300 Mbps - 10-bit CMOS output @ 50 Mhz (150 fps) | ||

| 2MP - 2048 (H) x 1088 (V) | Pipelined global shutter with true CDS | 5.5 x 5.5 μm2 | 2/3'' | 340 fps (10 bit) | 16 LVDS outputs @ 480 Mbps | ||

| 4MP - 2048(H) x 2048 (V) | Pipelined global shutter with true CDS | 5.5 x 5.5 μm2 | 1'' | 180 fps (10 bit) | 16 LVDS outputs @ 480 Mbps | ||

| 12MP - 4096(H) x 3072(V) | Pipelined global shutter with true CDS | 5.5 x 5.5 μm2 | APS-like | 150 fps (10 bit) | 150 fps (10 bit) - 90 fps (12 bit) | ||

| 20MP - 5120(H) x 3840(V) | Pipelined global shutter with true CDS | 6,4 x 6,4 μm2 | 35mm | 30 fps (12 bit) | 16 LVDS channels @ 480 Mbps | ||

| 70MP - 10000 (H) x 7096 (V) | Electronic rolling shutter with true CDS correction | 3.1 x 3.1 μm2 | 35mm | 3 fps | 8 analog channels |

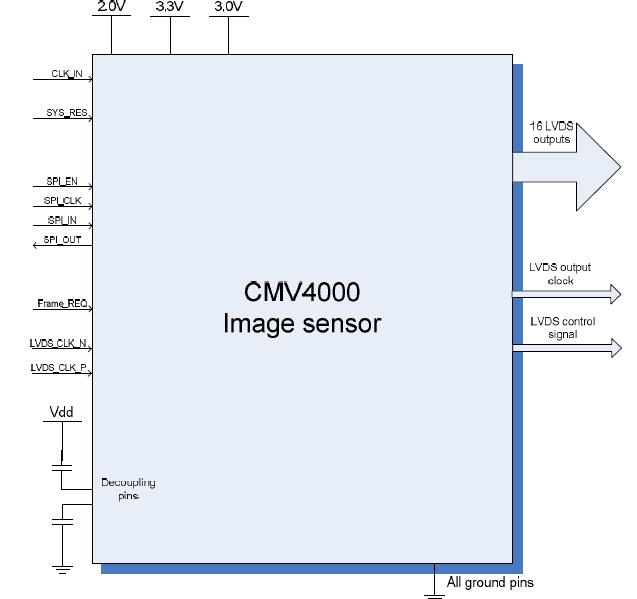

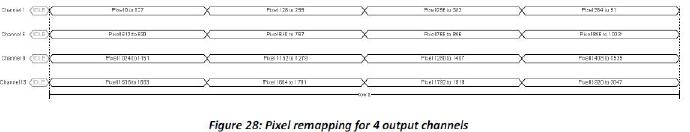

我的设计针对CMV4000芯片,分辨率为2048x2048,采用12bitsADC和12bitsLVDS模式,4output方式。CMV4000主时钟采用20MHz,数据率为240Mbps。

FPGA使用ALTERA公司的EP2C8Q208,该芯片有4个bank,将一个bank设置为LVDS工作方式,其他3个bank为LVTTL IO。CMV4000的4个输出通道直接连接到FPGA芯片引脚。FPGA产生CMV4000工作所需的时钟信号和控制信号,还有SPI配置信号。

其中包括:CMV_CLK CMV4000主时钟,20MHz

CMV_RESN CMV4000复位信号

F_REQ 图像请求信号

T_INT1/2 外部曝光控制信号

SPI_EN SPI使能信号

SPI_CLK SPI时钟

SPI_IN SPI数据输入

SPI_OUT SPI数据输出

LVDS_CMV_CLKN/P CMV4000LVDS时钟输入

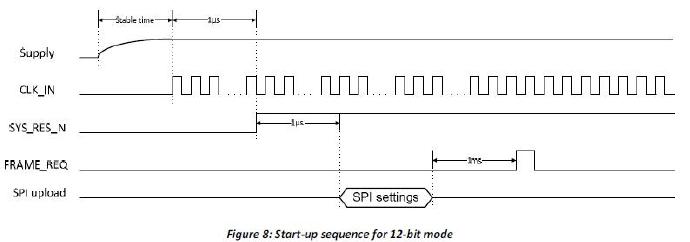

手册中给出了CMV4000的上电时序,必须严格按照CMV4000的上电时序来做。

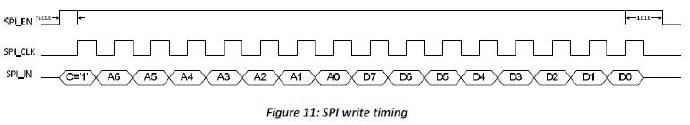

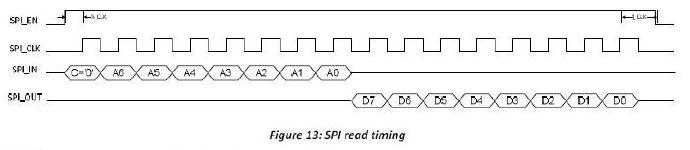

按照大多数的cmos图像传感器工作特点,CMOS在上电后需要对内部工作寄存器进行初始化,才用VHDL语言编写SPI物理层接口程序,和CMV4000初始化配置程序,配置CMOS的工作方式、设置曝光时间、增益、通道设置等参数。

MV4000上电配置结束后,FPGA发送图像请求,随即开始接收来自LVDS接口的串行数据,程序设置位对齐检测模块,当正确接收到字节/字数据之后,启动有效数据接收模块,在行场有效信号的同步下,正确接收图像数据。

硬件上设置了两片2048x8bits的SRAM芯片,用于存储图像数据。由于整帧图像大小为2048x2048,所以需要将图像分为上下两部分分别存储在两片SRAM中。

另外由于采用4通道模式,四个通道的像元数据同时到达,所以必须在12个像素位周期内存储完4个同时到达的四个像素数据。

所以,存入SRAM1中的字节依次为,第一行第一个像素,第一行第512个像素,第一行第1024个像素,第一行第1536个像素,然后是第一行第二个像素,第一行第513个像素,第一行第1025个像素....

第二行的数据依次类推...

所以在SRAM读出的过程中,如果是依次读出SRAM中的数据,则数据传输到PC机之后,采集软件需要根据SRAM的存储次序,将图像数据重新排序回来,还原为原始的正常的图像。

这里,硬件设计采用单通道LVDS接口,将图像数据传输到PC机的LVDS采集卡,上位机软件进行读取。该LVDS接口采用10MHz速度,所以传输一帧图像的速度较慢,大概为3s左右。

硬件电路如下图所示:

下面是上位机采集软件采集的完整的图像,图像大小为2048x2048.

为了调试方便,初始化过程中,曝光时间设置约为10ms,而在该系统的测试环境中,10ms的曝光时间太少了,传感器对于图像的电荷累计不足,而且在存储和读出SRAM过程中,均选取12bits图像中的低8位数据,所以上面的图像看起来,整体偏暗,且部分区域已经有了翻转的现象。但是整个数据采集和传输流程是没有问题的。

接下来就是根据实际的应用环境,适当的设置曝光时间、增益等参数,选择图像的高位信息进行图像处理,以达到后端数据处理单元所需的最终效果。

进一步提高fps:

目前CMV4000采用的设计思路是4通道输出,12bits模式,数据率为240MHz。按照手册中的典型值:

4通道输出,12bits模式,数据率480MHz,帧率37.5fps。

按照如上计算,理论上,我们采用240MHz的数据率,帧率应该是18.75fps。每帧耗时53.333ms。

如果数据率仍然使用240MHz,但是数据宽度改为10bits模式,则一个像素数据将减少2个数据时钟,即在10个数据时钟,即可输出一个像素数据。即,每个像素节省了2*1/240MHz=8.333ns。

按此计算,一帧数据2048*2048个像素总共节省时间为:8.333ns*2048*2048=34.951ms。

用当前设计的每帧耗时,减去可以节省下来的时间,就是10bits模式时,每帧图像的耗费时间:

T=53.333ms-34.951ms=18.382ms。

则在240MHz数据率,10bits模式下,理论帧率为:1/18.382=54.4fps。

当然,这个值只是理论计算值,具体帧率还要根据实际测量得到。可通过测量FVAL信号宽度和周期计算得知。

电脑模拟的星点图:

1635

1635

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?