1.实验目的

(1)熟悉并使用Multisim仿真软件。

(2)熟悉多思计算机组成原理网络虚拟实验系统的使用方法。

(3)掌握全加器的逻辑结构和电路实现方法。

2.实验要求

(1)做好实验预习,复习全加器的原理,掌握实验元器件的功能特性。

(2)按照实验内容与步骤的要求,独立思考,认真仔细地完成实验。

(3)写出实验报告。第二次实验之前交第一次实验。

3.实验原理

在数字电路和计算机组成中,半加器(Half Adder)和全加器(Full Adder)是两种基本的逻辑电路,用于实现二进制加法运算。它们的存在是为了满足不同场景下的加法需求,并通过模块化设计优化电路的复杂性和资源利用。

(1)半加器

概念: 半加器是实现两个一位二进制数相加的逻辑电路,它只考虑两个加数本身,不考虑来自低位的进位。

产生原因: 在数字电路发展初期,需要构建一种基础的加法单元来实现简单的加法运算。半加器就是为了满足这种最基本的一位数加法需求而设计的,它是构建更复杂加法器的基础模块,其逻辑相对简单,易于理解和实现,为后续全加器等复杂加法电路的设计提供了基础。

应用场景: 在一些对运算精度要求不高,只需要进行简单的一位数加法运算的电路中,半加器可以直接发挥作用。例如,在某些简单的数字控制系统中,可能只需要对一位二进制数进行加法操作来实现特定的控制逻辑。

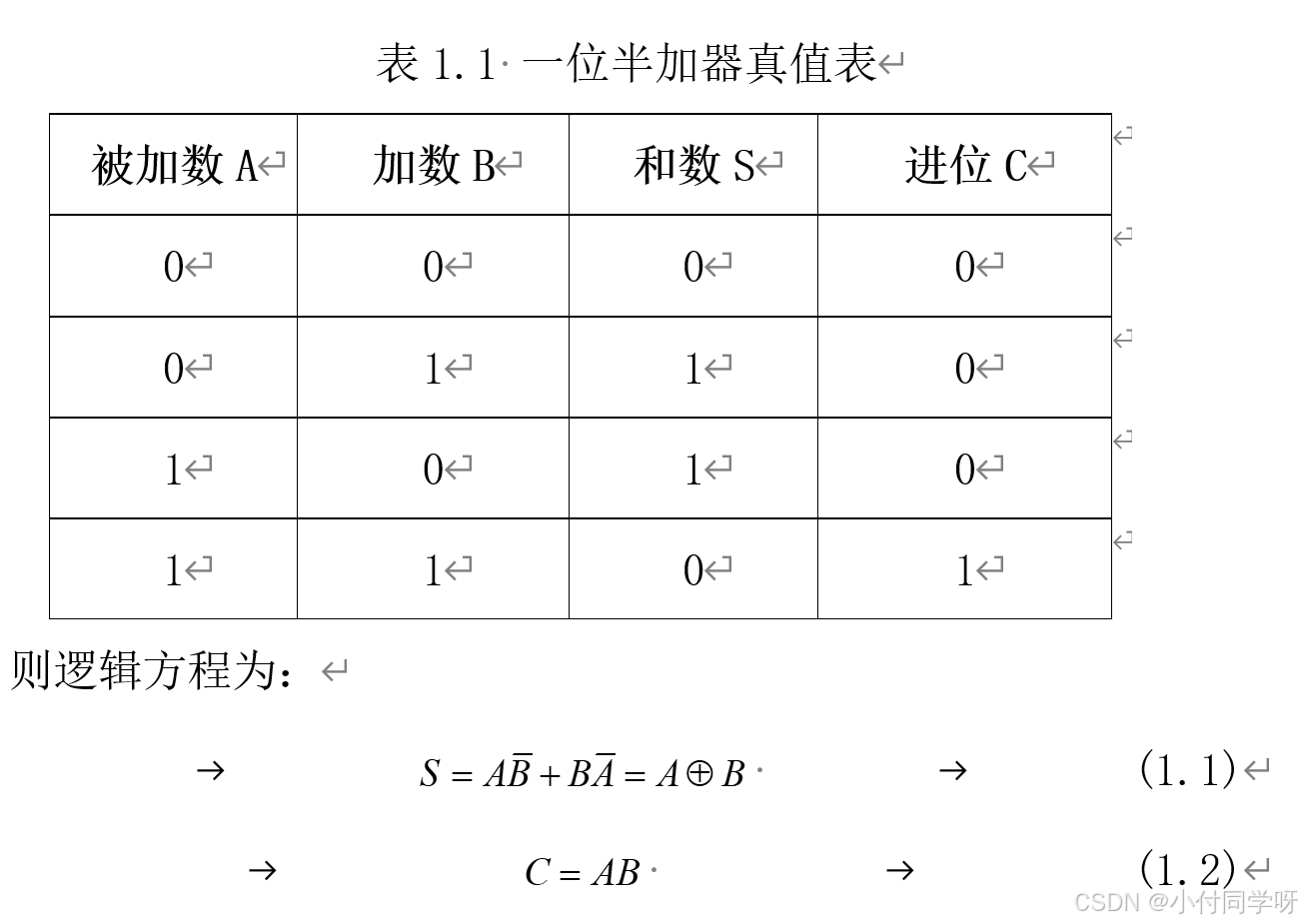

1位二进制半加器器有2个输入量:两个二进制数字A1、B1,没有来自低位的进位。如表1.1所示,为一位半加法器真值表。

表1.1 一位半加器真值表

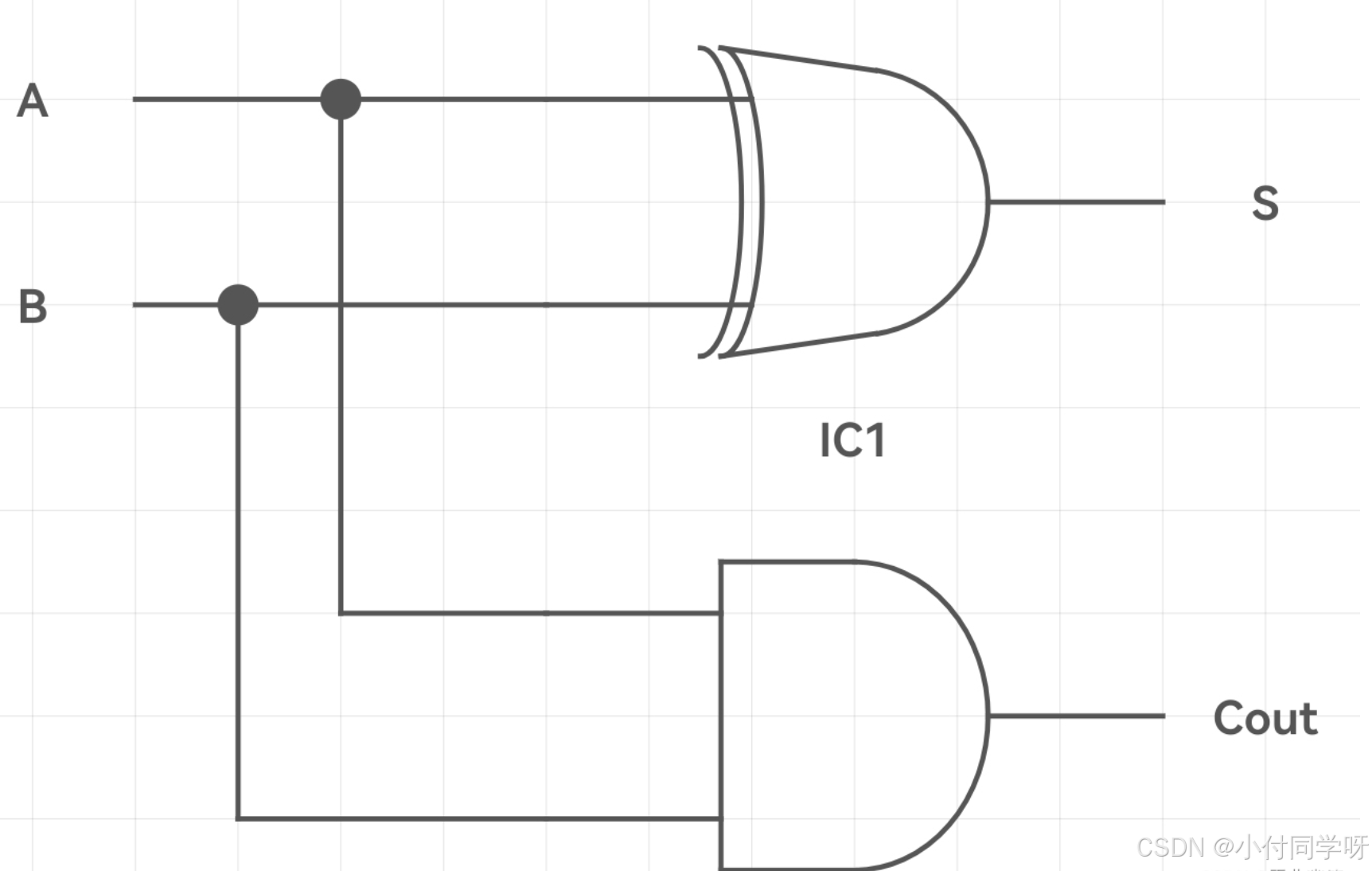

根据半加器的真值表,我们可以很轻松地画出逻辑门电路。

(2)全加器

概念: 全加器是在半加器的基础上,不仅考虑两个本位加数,还考虑来自低位的进位的一位二进制加法器。它有三个输入端口,分别为两个本位加数和来自低位的进位,以及两个输出端口,输出本位和与向高位的进位。

产生原因: 满足多位加法需求:在实际的数字运算中,经常需要对多位二进制数进行加法运算。半加器无法处理低位的进位,而全加器能够将低位的进位考虑进来,从而实现多位二进制数的逐位相加,是实现多位加法器的关键模块。提高运算完整性:为了使加法运算在各种情况下都能准确进行,需要一个能综合考虑所有进位情况的加法单元。全加器能够完整地处理一位加法运算中的所有输入情况,包括本位相加和来自低位的进位,保证了加法运算的准确性和完整性。

应用场景: 在计算机的算术逻辑单元(ALU)中,全加器是实现整数加法运算的核心部件。它可以级联起来构成多位加法器,实现对多位二进制整数的加法运算,是计算机进行数据处理和运算的基础。在数字信号处理、计数器等数字电路中,全加器也被广泛用于实现加法功能。

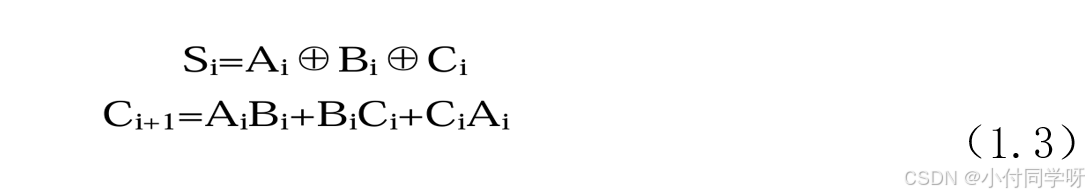

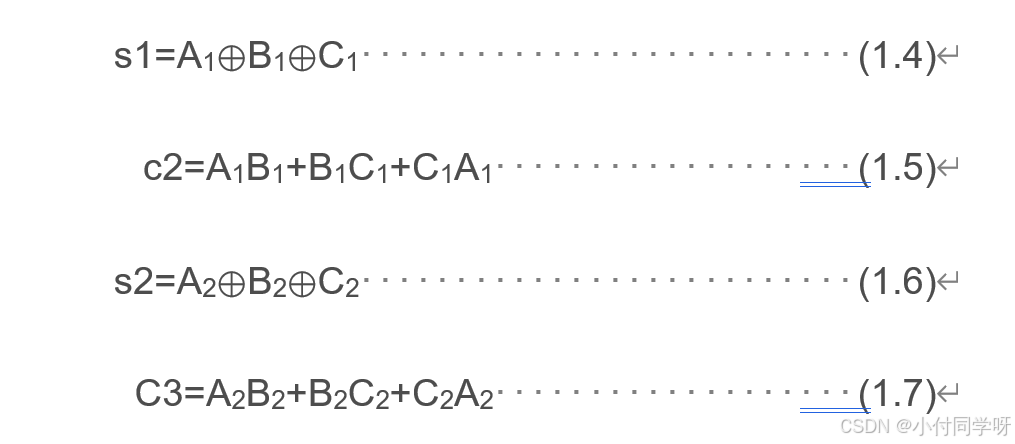

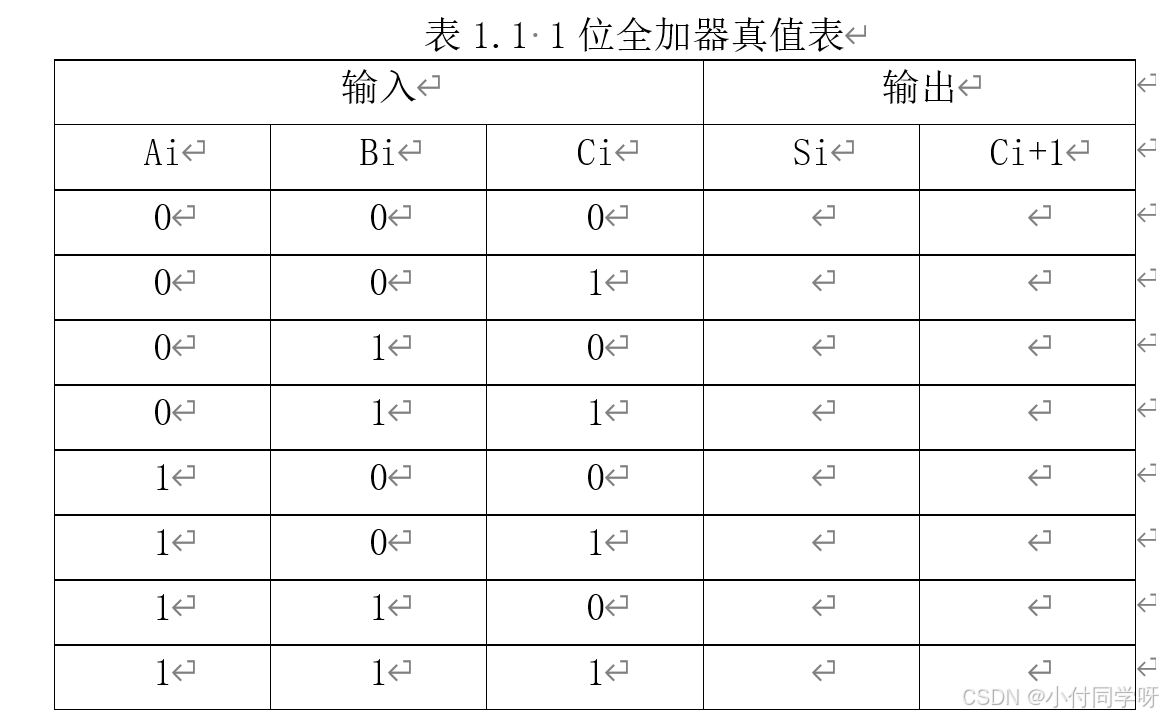

1位二进制加法器有三个输入量:两个二进制数字Ai、Bi和一个低位的进位信号Ci, 这三个值相加产生一个和输出Si以及一个向高位的进位输出Ci+1,这种加法单元称为全加器,其逻辑方程如下:

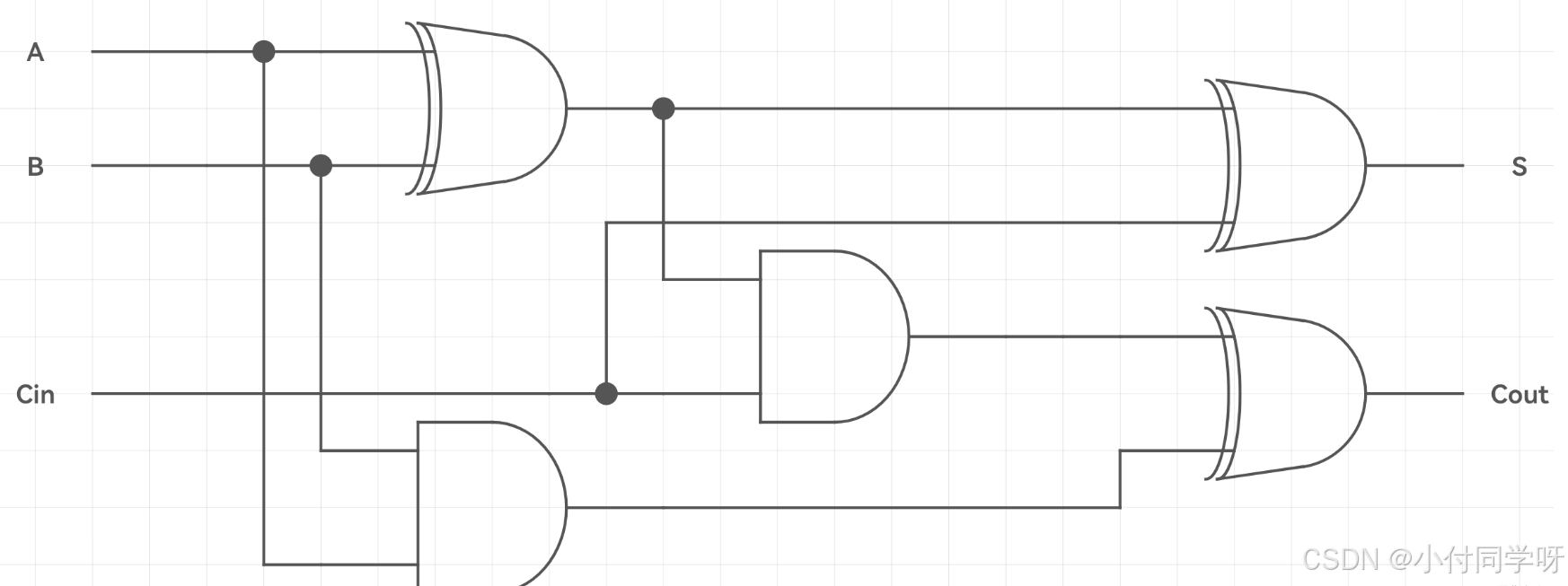

在计算加法时,相同位上的数相加后,还要加上从低位进上来的数。因此,下一步就是将半加器中的S 和Cin在经过一个半加器。

处理进位:最后一步就是处理连续的两个半加器所产生的两个进位。只要任意一个Cout 输出1,最终结果就是该位一定向高位产生一个进位。因此只需要用一个或门将两个Cout 相连。实际上,细心观察不难发现,不可能出现两个Cout同时输出1的情况出现。因此,将或门替换为异或门也可以取得同样的效果。

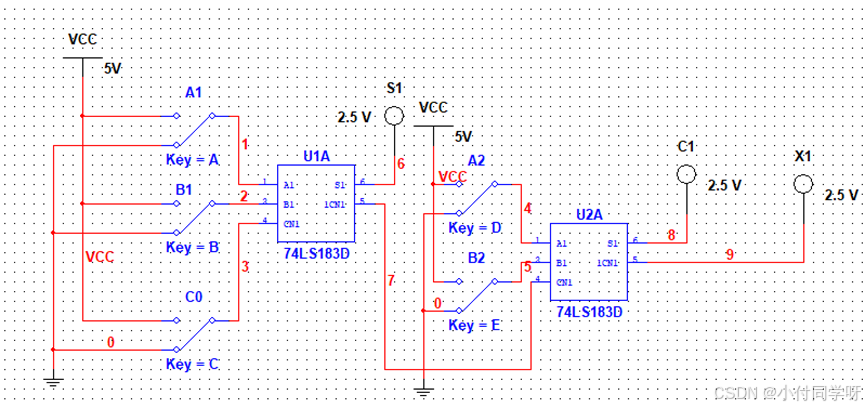

2位二进制加法器有五个输入量:两位二进制数字A2A1、B2B1和一个低位的进位信号C1, 这五个值相加产生一个和输出S2S1以及一个向高位的进位输出C3,其逻辑方程如下:

4.实验内容及步骤

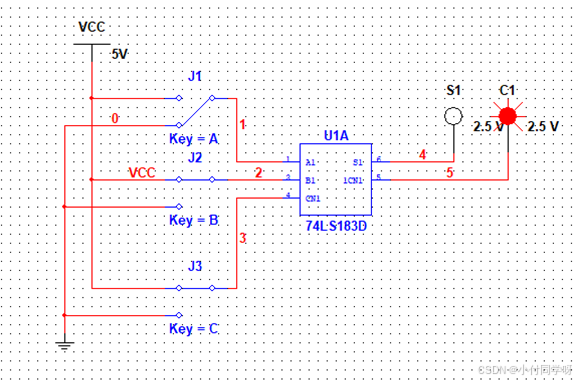

(1)使用Multisim实现全加器

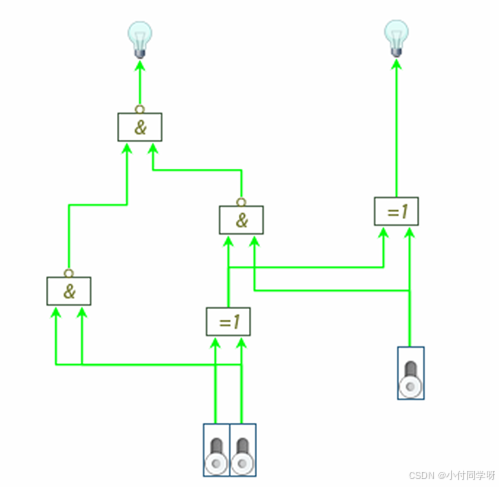

实验电路

将实验结果填写在表1.1中。

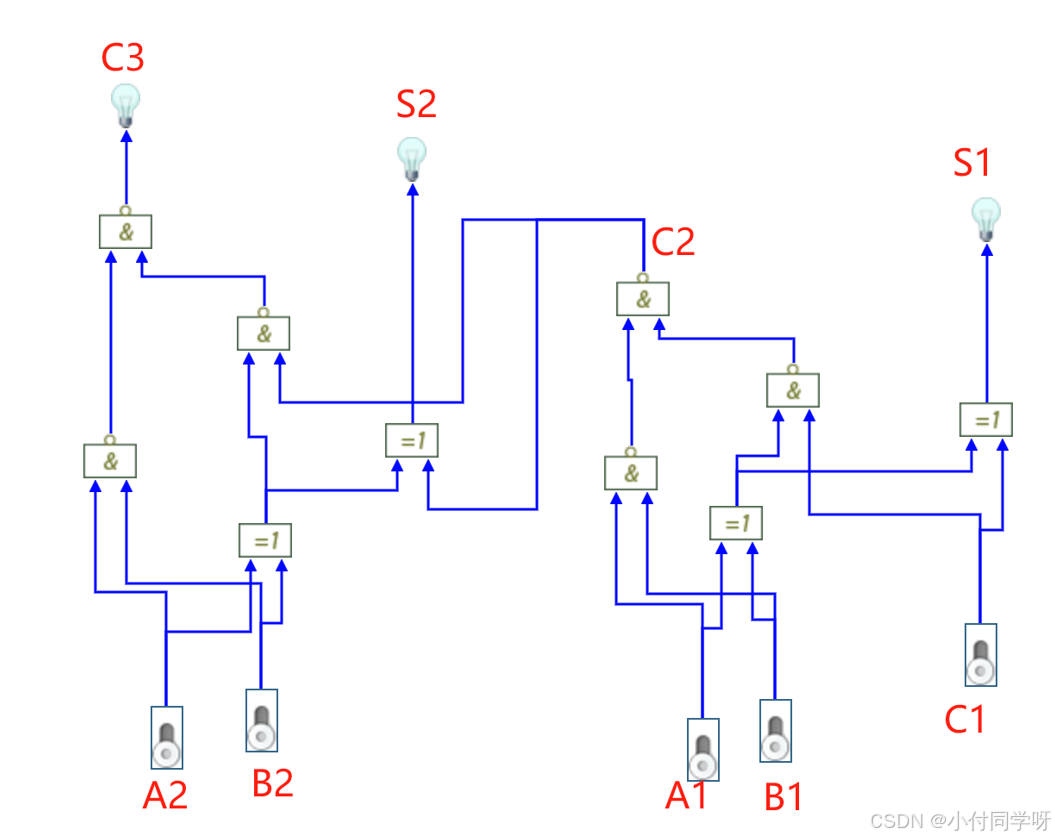

2位全加器电路

(2)使用多思软件实现全加器电路

DS-VLAB是一款计算机组成原理网络虚拟实验软件,该软件从功能上对数字器件进行仿真,可进行综合性、设计性实验,专为高等院校计算机及相关专业本科生计算机组成原理实验教学设计开发。多思官网:http://www.dsvlab.cn

1)运行虚拟实验系统。

从左边的实验设备列表选取所需组件拖到工作区中,按照图所示搭建实验电路。

2)打开电源开关

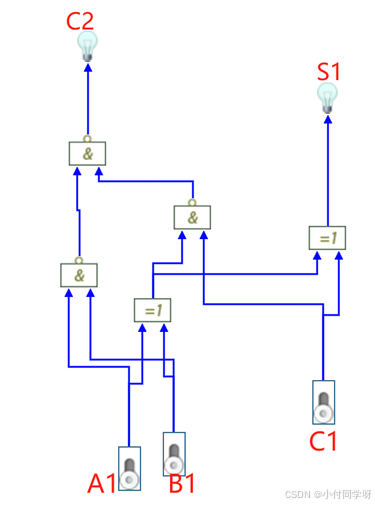

1位全加器实验电路

2位全加器实验电路

2656

2656

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?