jk触发器可选jkff,7473,7473o,74112。我选的74112。

注意:按照我的设计,要拨码之后流水灯才会流动。

生成自定义器件后,若原来的电路图发生改变,需要重新生成自定义器件(好像还要先把原来的自定义器件删掉才行)。

加入分频器后波形仿真不了,直接下载就行。

课本:数字逻辑设计基础第二版 何健新 高等教育出版社

电路设计参考p179,185,212,214,221,222。

实验要求

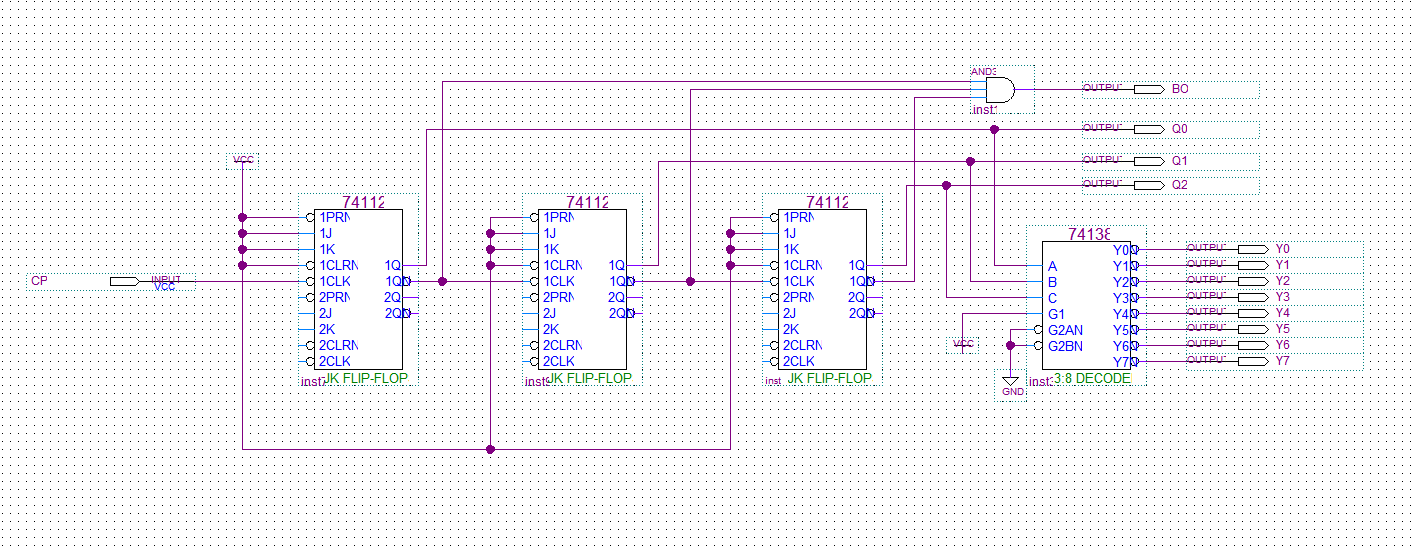

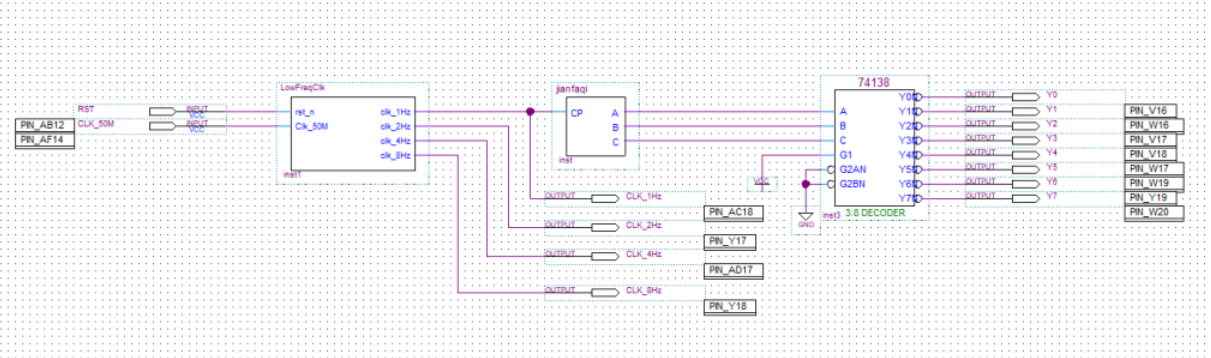

- 设计计数译码型8位流水灯的逻辑电路。要求采用JK或者D触发器构成SSI异步3位二进制计数器和74138实现。

- 使用VHDL语言描述做一个分频器,利用实验板50MHZ系统时钟,采用分频的方案产生1HZ、2HZ、4HZ、8HZ的低频时钟信号,并用示波器显示其中低频信号。

- 调用50M分频信号模块,将1Hz信号作为流水灯电路的CP信号输入,设计一个自动流水灯。

电路设计

对于74138译码器:

简介:74138是一种3线至8线的二进制译码器。它具有3个数据输入、8个数据输出和3个芯片选择输入端子。当芯片有效(片选)时,输出端子中有效的一位就是输入值的译码值。例如,当输入为001时,Y1输出为0,其余输出全为1。

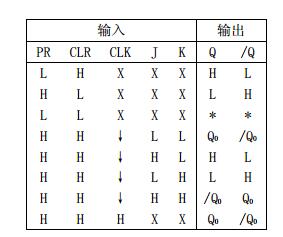

对于74112双jk触发器:

简介: 74112是双jk触发器。该器件由2个下降沿有效的时钟输入端(CLK1,CLK2),四个数据输入端,4个输出端,2个低电平有效的直接复位端(CLR1,CLR2)(置0端)和两个低电平有效的直接置位端(PR1,PR2)(置1端)构成。

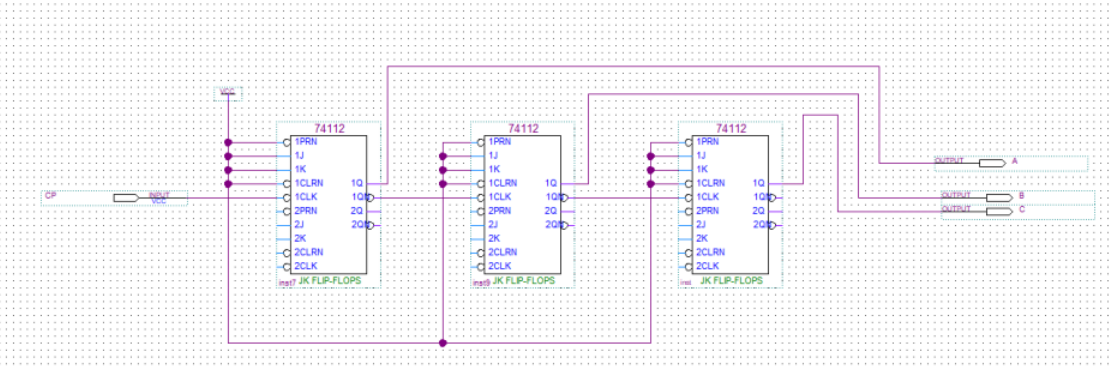

计数器译码型8位流水灯原理分析: 为了保证电路简洁清晰,我使用了三个74112构成SSI异步3位2进制减法计数器。置位端,复位端,JK都接1,上一个74112的输出1QN作为下一个74112的1CLK输入。这样,最低输出端翻转发生在CP的下降沿,其余每个输出端状态的翻转正好位于它相邻低位的上升沿时刻。

电路设计如下:

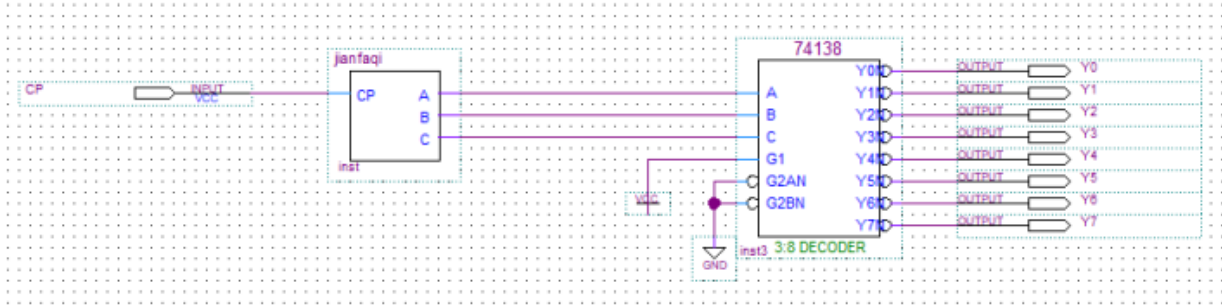

将上图74112部分拆分到新文件,编译后生成自定义器件jianfaqi。

jianfaqi

原来电路图改成这样

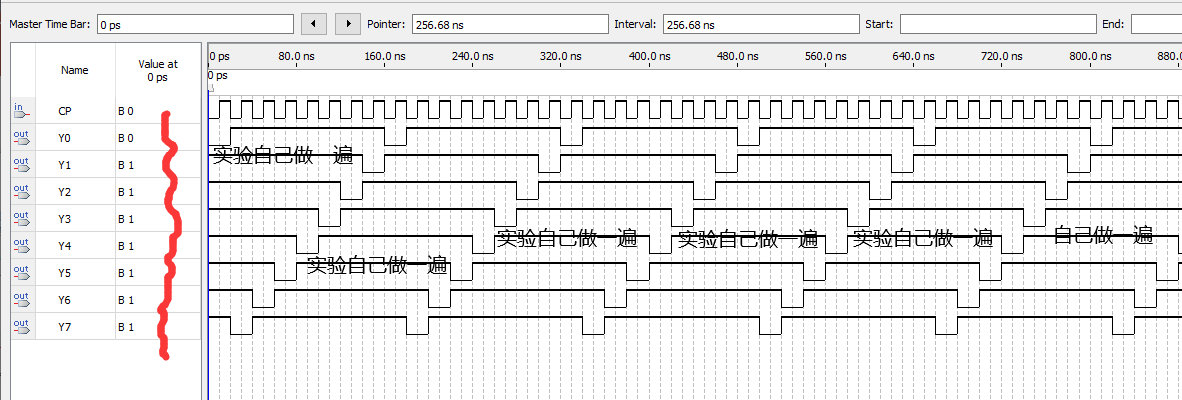

波形仿真

然后新建vhdl文件,输入以下分频器代码,保存为LowFreqClk。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY LowFreqClk IS

PORT(rst_n : IN STD_LOGIC;

Clk_50M : IN STD_LOGIC;

clk_1Hz : buffer STD_LOGIC;

clk_2Hz : buffer STD_LOGIC;

clk_4Hz : buffer STD_LOGIC;

clk_8Hz : buffer STD_LOGIC);

END LowFreqClk;

ARCHITECTURE Behv OF LowFreqClk IS

BEGIN

PROCESS(Clk_50M,rst_n)

VARIABLE Count:INTEGER ;

BEGIN

IF rst_n = '0' then

Count := 0 ;

clk_8Hz <= '0';

ELSIF Clk_50M'EVENT AND Clk_50M='1' THEN

IF Count >= 3124999 THEN

clk_8Hz <=not clk_8Hz;

Count := 0 ;

ELSE

Count := Count + 1;

END IF;

END IF;

END PROCESS ;

PROCESS(clk_8Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_4Hz <= '0';

ELSIF Clk_8Hz'EVENT AND Clk_8Hz='1' THEN

clk_4Hz <=not clk_4Hz;

END IF;

END PROCESS ;

PROCESS(clk_4Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_2Hz <= '0';

ELSIF Clk_4Hz'EVENT AND Clk_4Hz='1' THEN

clk_2Hz <=not clk_2Hz;

END IF;

END PROCESS ;

PROCESS(clk_2Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_1Hz <= '0';

ELSIF Clk_2Hz'EVENT AND Clk_2Hz='1' THEN

clk_1Hz <=not clk_1Hz;

END IF;

END PROCESS ;

END Behv;

编译通过后file->create->create symbol files for current file。

然后修改原理图同下。

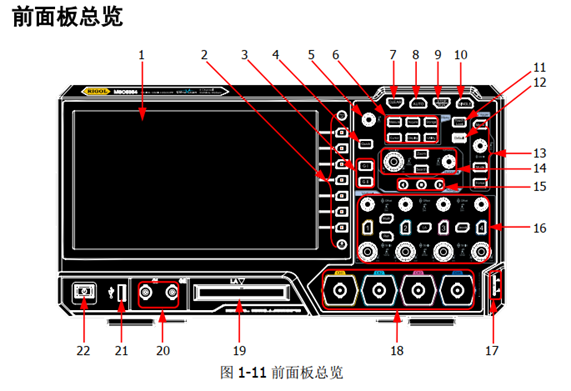

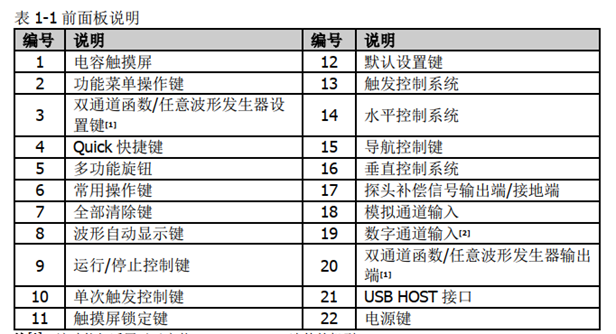

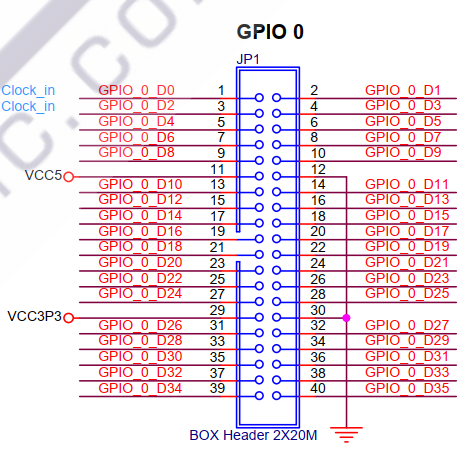

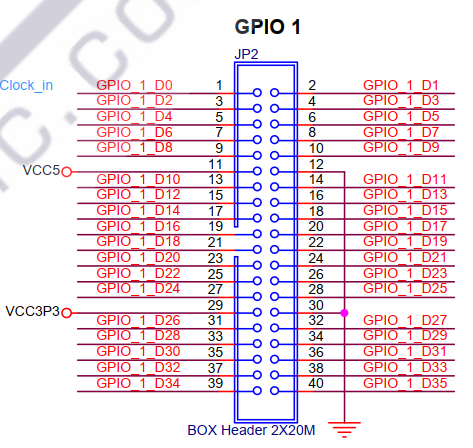

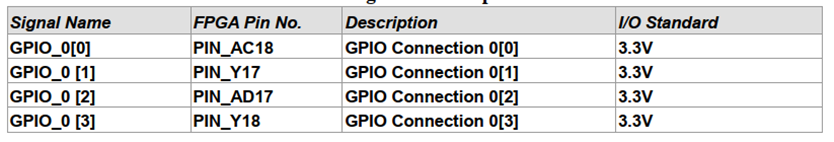

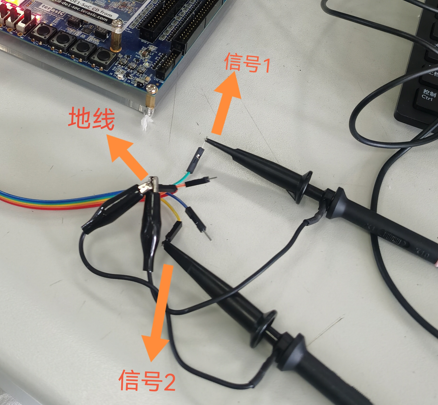

时钟波形测试:FPGA开发板波形输出管脚的引出采用杜邦线连接,然后示波器探头接入到示波器,这里我们只做两个通道的显示(4个频率中任选2个),示波器的探头接地端接入到JP1的12脚(GND),探针夹在时钟输出端。4通道波形展示,4个通道分别用不同的额颜色显示,其中CH1黄色、CH2青色、CH3紫色、CH4蓝色。

附录

拨码开关等见第一篇附录。

74112功能表

MSO5000示波器

5csema5f31c6n的GPIO扩展。

本文介绍了如何使用JK触发器74112和74138构建8位计数译码流水灯电路,通过VHDL实现分频器,将50MHz时钟转换为1HZ、2HZ、4HZ、8HZ的低频信号,以满足实验要求。涉及到了电路设计、自定义器件生成和波形仿真测试等内容。

本文介绍了如何使用JK触发器74112和74138构建8位计数译码流水灯电路,通过VHDL实现分频器,将50MHz时钟转换为1HZ、2HZ、4HZ、8HZ的低频信号,以满足实验要求。涉及到了电路设计、自定义器件生成和波形仿真测试等内容。

4433

4433

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?