some just want anything, but everything means nothing, if I ain't got you yeah.

我波形仿真cnt4忘给输出了,需要单独仿真,注意一下。

实验要求

- 熟悉双向移位寄存器74LS194的应用,设计右移模12扭环形计数器。

- 熟悉加计数器74LS160的应用和设计,设计一个计数状态为1-24的加计数器电路。

- 采用vhdl完成模4计数器设计。

- 完成对应器件的波形仿真,设计交通信号灯控制电路,下载到实验板上。

电路设计

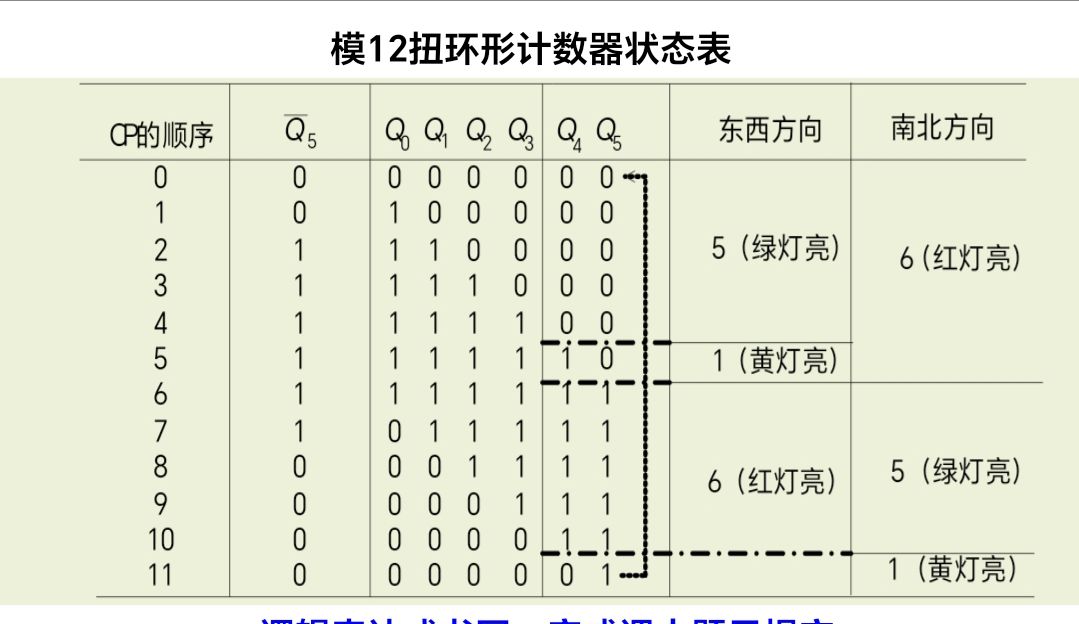

右移模12扭环形计数器设计:

简介: 两个74194的M1=0,M0=1,使用同一个CP信号,将左侧74194的Q3接右侧74194的DSR,使其扩展成8位右移移位寄存器,左侧DSR=Q’1N,满足2n进制要求第n位输出通过非门接到DSR端的要求。CRN端接同一个CRN清零信号。

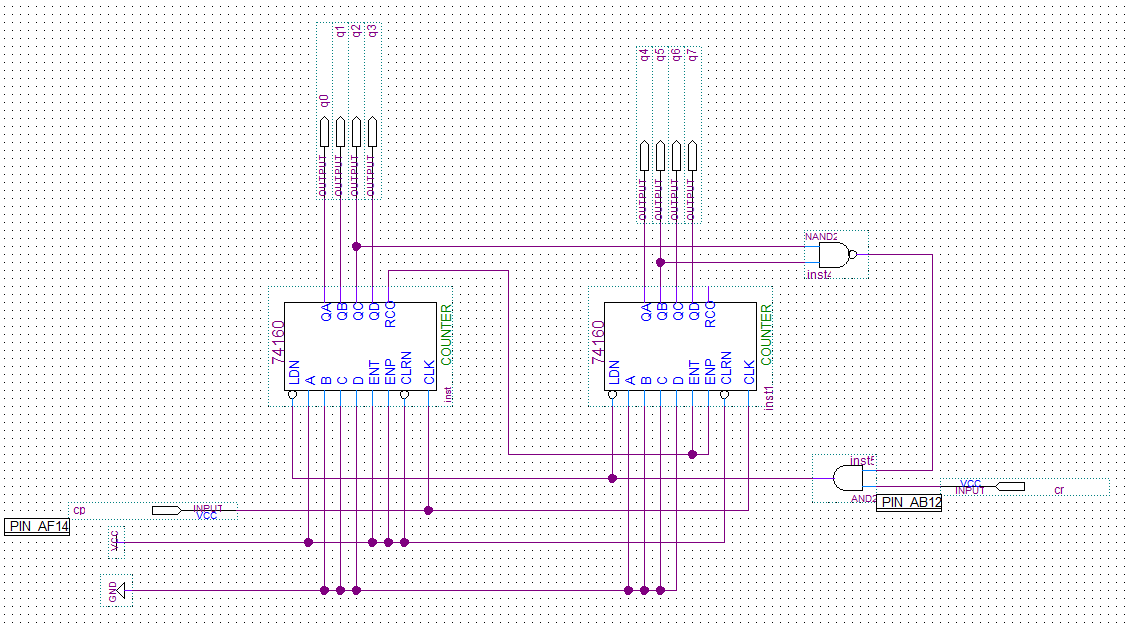

1-24的加计数器电路设计(count24):

简介:初态1,末态24,有初态得用反馈置数法。右侧74160表示十位数,左侧74160表示个位数, D3’D2’D1’D0’D3D2D1D0=0000 0001表示初态,Q3’Q2’Q1’Q0’Q3Q2Q1Q0=0010 0100表示末态,末态为1的输出接到与非门,再返回给两个74160的LDN端。左侧低位的ENT(CTT),ENP(CTP)接1,右侧的ENT,ENP接左侧的RCC(CO进位),两者的CRN(CLRN)接1,CLK接同一个CP输入。若要实现同步置数,需要保证时钟有时钟信号输入。

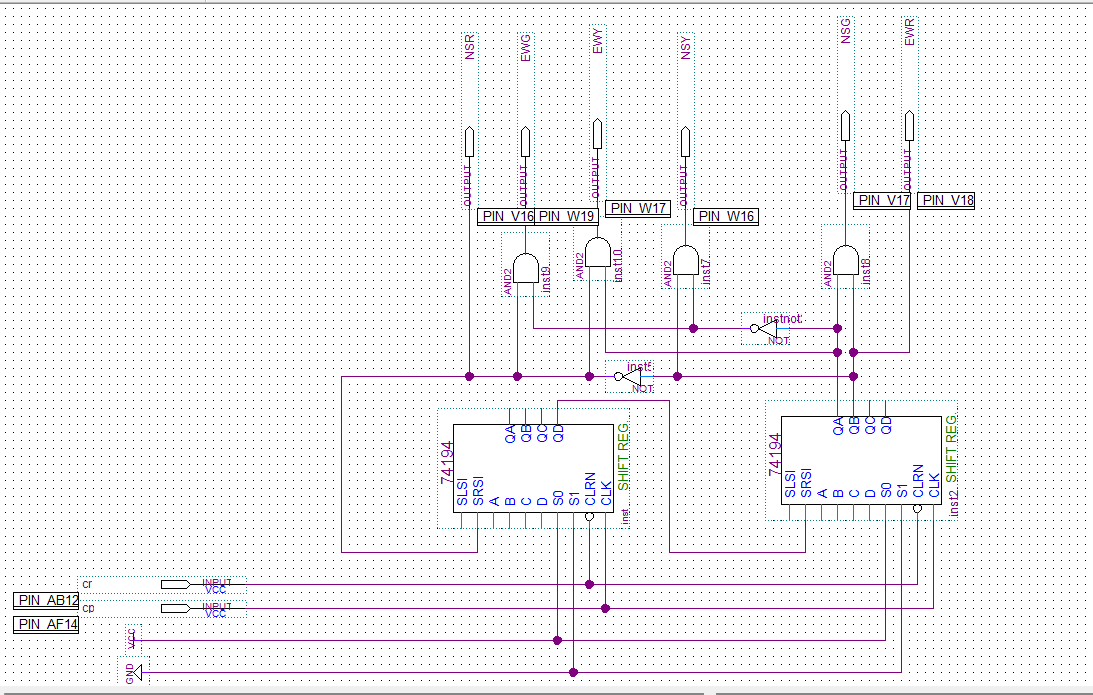

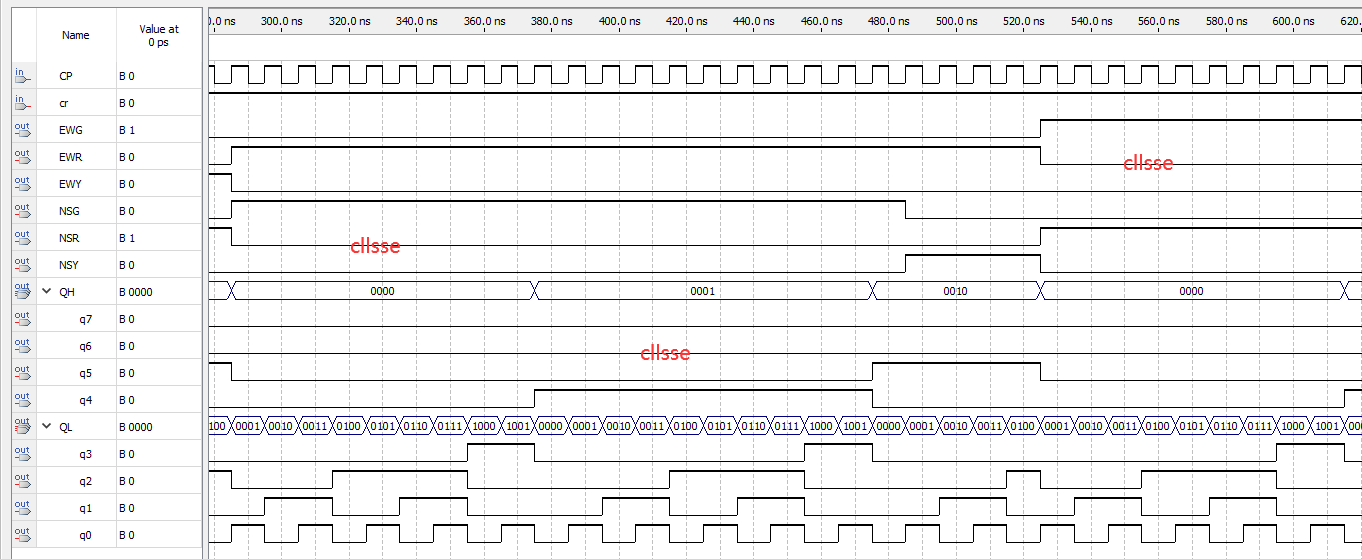

交通灯控制电路设计(cr12):

简介:在本实验中,需要使用LowFreqClk和cnt4调整CP周期到4s。根据实验所给真值表,得出逻辑表达式:东西方向EWG=/Q4/Q5,EWY=Q4/Q5,EWR=Q5;南北方向NSG=Q4Q5,NSY=/Q4Q5,NSR=/Q5(使用/Q4表示Q4非)。按照逻辑表达式设计门电路即可。

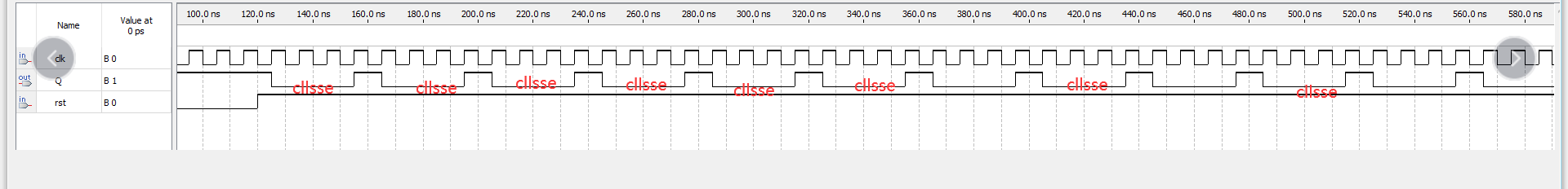

模4计数器设计(cnt4):

简介:rst为低电平有效的置数端,该器件每遇到一个上升沿都会使count+1并输出0,直到count为3时清零并输出1。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY LowFreqClk IS

PORT(rst_n : IN STD_LOGIC;

Clk_50M : IN STD_LOGIC;

clk_1Hz : buffer STD_LOGIC;

clk_2Hz : buffer STD_LOGIC;

clk_4Hz : buffer STD_LOGIC;

clk_8Hz : buffer STD_LOGIC);

END LowFreqClk;

ARCHITECTURE Behv OF LowFreqClk IS

BEGIN

PROCESS(Clk_50M,rst_n)

VARIABLE Count:INTEGER ;

BEGIN

IF rst_n = '0' then

Count := 0 ;

clk_8Hz <= '0';

ELSIF Clk_50M'EVENT AND Clk_50M='1' THEN

IF Count >= 3124999 THEN

clk_8Hz <=not clk_8Hz;

Count := 0 ;

ELSE

Count := Count + 1;

END IF;

END IF;

END PROCESS ;

PROCESS(clk_8Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_4Hz <= '0';

ELSIF Clk_8Hz'EVENT AND Clk_8Hz='1' THEN

clk_4Hz <=not clk_4Hz;

END IF;

END PROCESS ;

PROCESS(clk_4Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_2Hz <= '0';

ELSIF Clk_4Hz'EVENT AND Clk_4Hz='1' THEN

clk_2Hz <=not clk_2Hz;

END IF;

END PROCESS ;

PROCESS(clk_2Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_1Hz <= '0';

ELSIF Clk_2Hz'EVENT AND Clk_2Hz='1' THEN

clk_1Hz <=not clk_1Hz;

END IF;

END PROCESS ;

END Behv; library ieee ;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cnt4 is

port (clk:in std_logic;

rst: in std_logic;

Q: out std_logic);

end cnt4;

architecture behv of cnt4 is

begin

process (clk,rst)

variable count: integer range 0 to 3;

begin

if rst='0'then

Q<='1';

count:=0;

elsif clk'event and clk='1' then

if count<3 then

Q<='0';

count:=count+1;

else

Q<='1';

count:=0;

end if;

end if;

end process;

end behv;

count24

cr12

波形仿真电路图

cnt4单独仿真

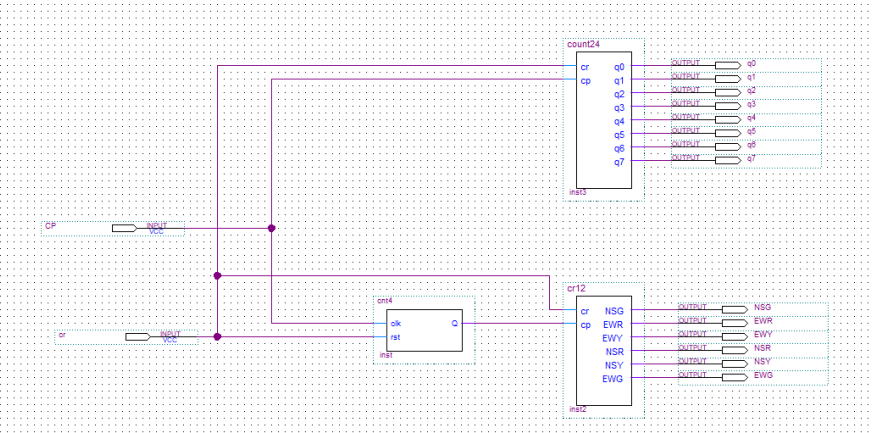

修改原理图并进行引脚分配同下,LowFreqClk单独有一个置数端,保证count24始终有时钟信号,以完成同步置数。(CP分配AF14引脚)

最终电路图

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?