超宽带无线通信技术是目前无线通信领域先进的通信技术之一,它利用极宽频带的超窄脉冲进行无线通信,在无载波脉冲体制雷达中被广泛应用,多年来一直被限定为军用技术。近年来,随着电子技术的飞速发展,在无线通信用户急增,频谱资源越来越稀缺,通信容量越来越大以及传输速率越来越来高的形势下,人们对超宽带技术的认识也更加清楚,它逐步转入民用阶段,用于实现高性能、低成本的无线通信系统。在20世纪60年代,时域电磁学研究工作广泛开展,人们在对微波网络由时域脉冲响应所反映的瞬时特性的研究过程中逐渐发现了超宽带技术。1962年,惠普公司开发出取样示波器,纳秒级脉冲的产生方法才得以发展,当时普遍采用雪崩晶体管或隧道二极管产生脉宽为纳秒级的脉冲信号,提供可供分析用的冲激激励信号,这使得人们能够正确地观察和测量微波网络的冲激响应。能产生几百毫伏窄脉冲的高速器件有隧道二极管和ECL集成电路,能产生几十伏到几百伏的高速器件有雪崩晶体三极管、阶越恢复二极管和俘越二极管。但是这些方法设计的窄脉冲发生器脉宽固定,不能调节脉宽,给应用带来不便。为满足不同应用场合对脉宽的需要,本文设计了基于CPLD和LCPECL的可调窄脉冲发生器,给实际应用带来了灵活性而且节约了成本。

1 窄脉冲的技术要求及产生方案

由于超宽带技术广泛应用于雷达系统,因此其应用环境就决定了窄脉冲的技术要求。脉冲源性能指标的衡量主要是幅度和脉宽这两个指标,一般要求幅度要大,这样探测距离才远;脉宽要窄,这样分辨率才高。因此,窄脉冲产生电路的性能与所使用器件的速度有很大关系。

目前,产生超宽带窄脉冲的方法主要有模拟和数字两种方法。模拟的方法主要是采用高速的阶跃二极管、隧道二极管、雪崩三级管或者微带线合成的方法产生纳秒级、皮秒级的窄脉冲。但由于受管子杂散的影响而导致脉冲不够理想,加上微带电路不好调试的原因,数字方法应运而生。在数字集成电路中,ECL门电路是速度最快的一种,其优点是开关速度高、负载能力强、内部噪声低,缺点是噪声容限小、功耗大、需负电源以及输出电平受温度影响大。由ECL发展而来的LVPECL门电路克服了ECL的缺点,采用低电压正电源、差分输入输出传输的特点,使其在产生窄脉冲电路方面具有很大优势。同时考虑到适应不同应用场合对脉冲发生器脉宽的要求,脉宽可调是本设计的一大亮点。因此,本文采用CPLD和LCPECL门电路器件来设计可调窄脉冲发生器。

本方案包括LVPECL窄脉冲产生电路和CPLD控制电路两部分,利用CPLD提供10 MHz的激励信号和对延时芯片进行写延时控制字来产生所需脉宽的窄脉冲信号。系统结构框图如图1所示。

2 CPLD+LVPECL 可调窄脉冲的原理及硬件电路设计

2.1 LVPECL 窄脉冲产生电路原理

窄脉冲产生器主要采用LVPECL 延时芯片和与门芯片实现,产生原理框图如图2 所示。首先把时钟信号分成两路,其中一路不经延时器直接到达高速比较器,另一路经过延时器和反相器再进入高速比较器,经过高速比较器后的两路时钟信号进入 LVPECL 与门, 输出的窄脉冲波形如图3 所示

2.2 LVPECL窄脉冲硬件电路设计

经分析比较,LVPECL窄脉冲硬件电路选择的器件如下:时钟分配器起到电平转换和时钟分配的作用,采用Maxim公司的MAX9323;可编程延时器件采用ON Semiconductor公司的MC100EP195;高速比较器选择ADI公司的ADCMP567;与门选择ON Semiconductor公司的MC100EP05作为亚纳秒脉冲产生器。LVPECL窄脉冲硬件电路通过两路实现:一路采用两片MC100EP195 级联产生固定延时;另一路采用两片MC100EP195级联产生20 ns范围内的可编程延时,即可产生20 ns内脉宽可调的窄脉冲信号。

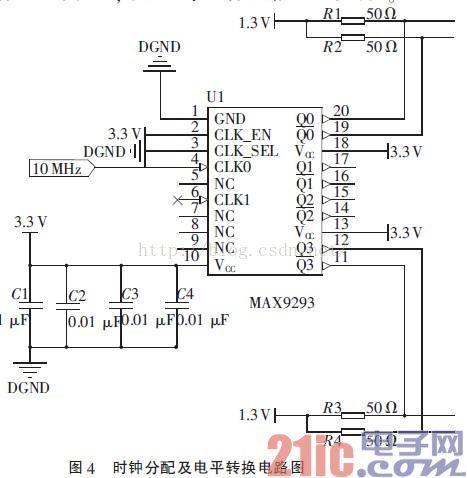

(1)时钟分配及电平转换电路

时钟分配及电平转换电路如图4所示。由于CPLD控制电路产生的10 MHz方波时钟信号是LVCMOS电平,本脉冲电路采用LVPECL电平,因此需先将LVCMOS电平转换为LVPECL电平,又由于本电路有两路信号,因此需进行时钟分配得到两路时钟。Maxim公司的MAX9323的主要功能和特性为低偏移、低抖动,2个LVCMOS输入时钟信号中的1个被分配到4个差分LVPECL输出。1个单逻辑控制信号CLK_SEL选择2个输入中的1个。器件工作在3.0 V~3.6 V范围内,如果采用3.3 V供电,则最多仅消耗25 mA的供电电流。此电路中,CLK_SEL被设置为接地,选择CLK0时钟信号输入,CLK_EN被设置高电平使能4路差分LVPECL 输出,本电路中只用到2路。根据LVPECL电平驱动要求,其输出端应通过50 Ω上拉电阻拉到VCC-2 V,即拉到1.3 V。此外,为确保电源稳定,采用多个电容旁路对电源去耦。

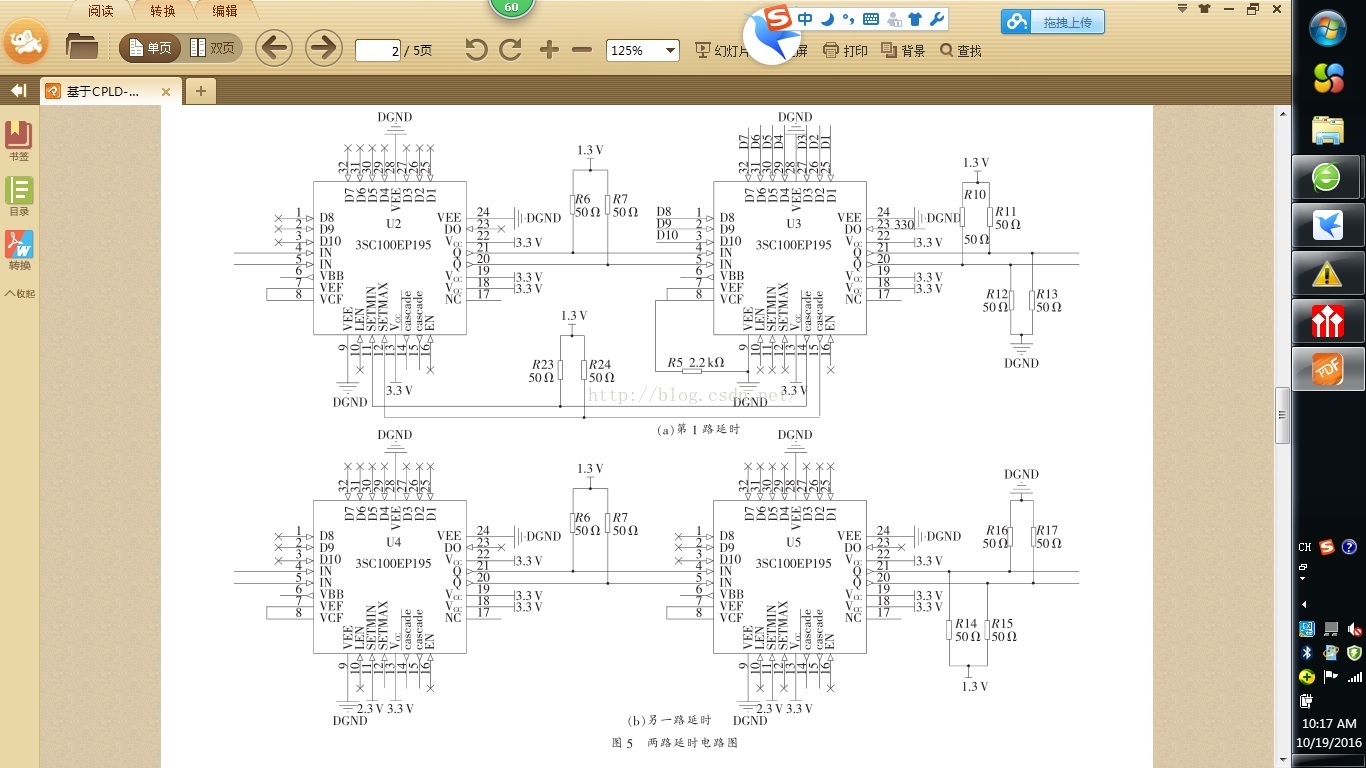

(2)可编程延时电路

可编程延时器是窄脉冲产生电路最为关键的芯片,ON Semiconductor公司的MC100EP195 10 bit可编程延时线,最小延时步进为10 ps,可产生10 ns范围内的可编程延时。它采用差分LVPECL输入输出,并且LEN具有锁存D[9:0]10 bit编程数据的功能,同时D[10]、SETMIN、SETMAX、CASCADE、CASCADE可构成级联系统来扩展延时范围。本电路中用到两路信号,第1路两片级联,第1片的SETMIN、SETMAX分别与第2片的CASCADE、CASCADE相连,如图5(a)所示。D[10]是级联信号 CASCADE的控制引脚,当D[10]为低电平时,CASCADE产生低电平,CASCADE产生高电平,使得片1的SETMIN高电平将产生最小延时,片2的延时由D[9:0]确定;当D[10]为高电平时,CASCADE产生高电平,CASCADE产生低电平,使得片1的SETMAX高电平将产生最大延时,片2的延时由D[9:0]确定,这样可以将可编程延时范围扩展到20 ns。但由于芯片本身有2.2 ns的固有传输时延,两片级联即有4.4 ns的固有传输时延。本脉冲发生器是将两路时钟信号进行比较,为了抵消第一路延时芯片的固有传输时延,另一路采用同样型号的两片芯片直接相连,并且将两片延时芯片SETMIN都设置为高电平产生最小延时,如图5(b)所示,这样就能够抵消芯片产生固有传输时延,使得两路时钟信号的延时差只受延时数据控制,能够得到极窄脉冲。根据LVPECL电平驱动要求,其输出端应通过50 ?赘上拉电阻拉到VCC-2V,即拉到1.3V。

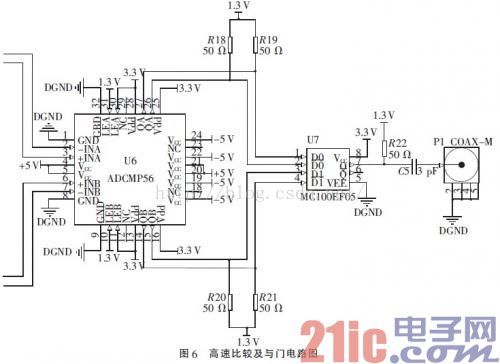

(3)高速比较及与门电路

高速比较及与门电路主要由高速比较器、LVPECL与门和RC微分电路3部部分组成,如图6所示。由于时钟信号经过一段传输距离后,信号的边沿会产生恶化和畸变,为了保证时钟信号边沿的陡峭,高速比较器ADCMP567对经过延时后的两路时钟信号进行整形,使得与门的输出不会有干扰脉冲的出现。ADCMP567是双通道高速比较器,具有比较模式和锁存模式两种工作模式。本电路中的两个通道都使用比较模式,使得输出信号能实时反映输入信号比较的结果,这通过将LEA和LEB接高电平VCC(3.3 V),将LEA和LEB接VCC-2.0 V(1.3 V)实现。将输出的两路LVPECL信号送入与门芯片进行“与”运算即可得到窄脉冲,不同的延时差能产生不同脉宽的窄脉冲。最后,通过RC微分电路就可以得到一阶高斯窄脉冲。不同脉宽的脉冲信号经过微分后得到的一阶高斯窄脉冲的正脉冲部分和负脉冲部分在拐点处延时不同,会导致波形的不连续性和失真,这与 RC微分电路充放电时间常数t有关,t应该满足和脉冲宽度tw相当,这样就能保证波形的连续性,减小失真。因此可以采用可调电容,以满足不同脉宽的需要,得到波形良好的一阶高斯脉冲。

2.3 CPLD控制电路

CPLD控制电路要提供多种功能:为本振PLL模块提供SPI串行接口;为窄脉冲发生器提供10 bit并行接口;产生两路10 MHz的方波信号,一路为窄脉冲发生器提供激励信号,另一路为接收端的A/D采样提供同步时钟;提供按键控制电路以及与PC串口进行串行通信。CPLD芯片采用Altera公司MAX-II系列的EPM240T100C3,该芯片支持ISP编程和JTAG调试,外围电路简单可靠。通过对外部50 MHz有源晶振产生的时钟进行5分频,得到10 MHz的方波信号用于激励窄脉冲。同时,扫描键盘判断是否有外部按键输入,如果有,则根据不同的按键选择不同的延时控制字,将其通过10 bit并行接口送入可编程延时芯片MC100EP195以产生不同的延时信号,这样便能产生不同脉宽的窄脉冲信号。图7为CPLD控制总体框图。

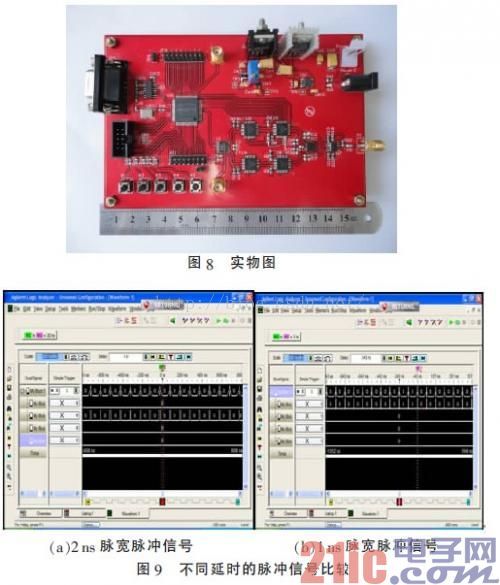

3 CPLD+LVPECL可调窄脉冲的测试

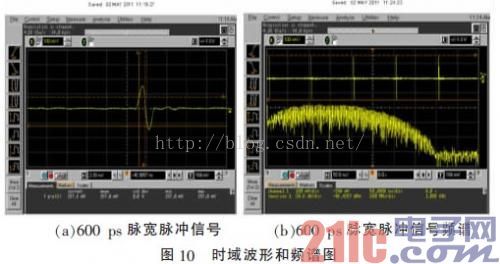

根据以上方案和电路,制作了图8所示的可调窄脉冲发生器。使用Agilent公司16903A逻辑分析仪测试LVPECL与门电路后的不同延时的脉冲信号如图9所示。

从图10(a)中可以看出,此脉冲波形的峰峰值幅度约为390 mV,脉冲宽带约为635 ps;从图10(b)的频谱图可知,信号10 dB带宽约为1.3 GHz,中心频率为800 MHz左右,频谱能量最高点对应的功率为-43 dBm。为了达到所需功率,可以接功率放大器进行放大满足发射功率的需要。

针对用模拟的方法或数字固定延时的方法产生超宽带窄脉冲脉宽不可调的缺点,本方案采用CPLD对可编程延时芯片写延时控制字来产生不同脉宽的窄脉冲信号。本系统可实现500 ps~20 ns范围内脉宽可调、幅度约为400 mV的脉冲信号。基于CPLD+LVPECL门电路的可调窄脉冲产生器为独立系统,能够满足不同应用场合的需求

介绍了一种基于CPLD和LVPECL门电路的可调窄脉冲发生器设计,该发生器可在500ps~20ns范围内产生脉宽可调、幅度约400mV的窄脉冲信号,适用于多种应用场景。

介绍了一种基于CPLD和LVPECL门电路的可调窄脉冲发生器设计,该发生器可在500ps~20ns范围内产生脉宽可调、幅度约400mV的窄脉冲信号,适用于多种应用场景。

366

366

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?