上图所示就是一个电晶体,控制线可以决定右侧电路是否通行(即有电无电)

先让上侧的electrode通电,如果control wire通电,则右侧放行,上侧electrode的电会流往下侧的electrode;

如果control wire不通电,则右侧不放行,下侧的electrode无电;

即control wire可以控制右侧下方线路的有电无电(即0, 1)

输入输出图:

当然这个模型只是个开始,可以控制有电无电,但为后续的发展奠定了决定性的基础。

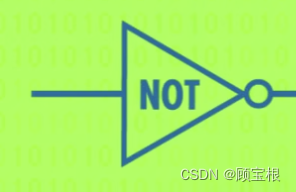

第二个模型:not gate 非门,即输入输出相反

右侧current线一直有电,如果input线通电,右侧放行,current的电流直接跑接地的ground线,所以output线上无电;

input如果不通电,让右侧不放行使current线的电流不会流往通地的ground线,而流往output线,output线上有电;

总结输入输出为如下:

将该模型包装一下,非门的表示方法如下:

建立非门这个模型后,少不了,与门(and gate),或门(or gate),以及异或门(xor gate);

and gate:

与门的模型是这样的,current通电,output上是否有电,取决于,transistorA和transistorB是否有电,是否放行,使current的电流往output

所以,只有当,两个电晶体下端的input都通电(即 都true),output才会true,其余通通false

总结输入输出如下:

经过包装,与门的表示方法如下:

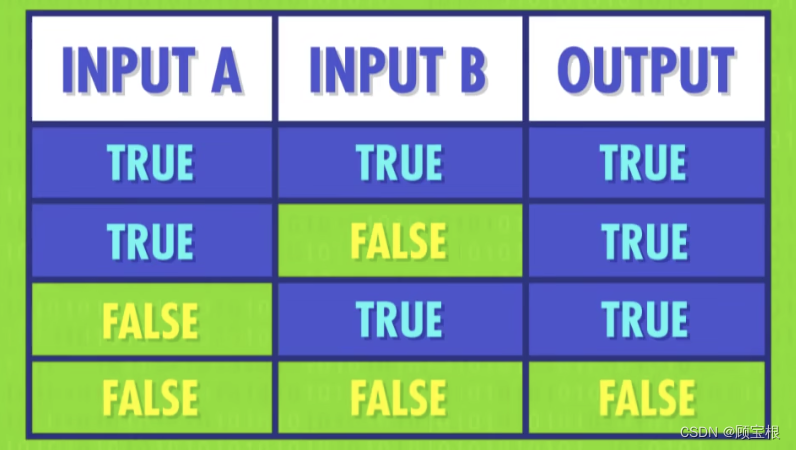

or gate:

或门的模型是:current通电,晶体管a或者b其一通电都能使output通电

输入输出图如下:

或门经过包装后,表示方法为:

xor:

xor gate 异或门则稍微复杂,它和or门只有在 两个输入都为true时的结果不同,故在or门的基础上进行修改,加了and gate和not gate

输入输出图和or门的输入输出的只区别在两个输入都为true时,or门输出是true,xor门输出是false

抽象包装后,xor门的表示方法如下:

现在手上的工具多了,相比最初只有晶体管只能控制有电没电,现在造出了四个很关键的逻辑门!

half adder “半加器” :

计算机里只有0和1,可以理解为晶体管的是否通电即代表了两种情况,即0和1,一位0或1即为1bit

那么,一位bit的相加如何完成,可以通过half adder

考虑到进位的情况,sum表示结果的低位,carry表示进位

可以尝试验证,

如果 0 + 0, sum得0,carry得0,结果为0正确;

如果 0 + 1, sum得1,carry得0,结果为1正确;

如果 1 + 0, sum得1,carry得0,结果为1正确;

如果 1 + 1, sum得0,carry得1,结果为10正确;

ok,现在通过half adder这个模型已经可以完成一位bit的相加了!

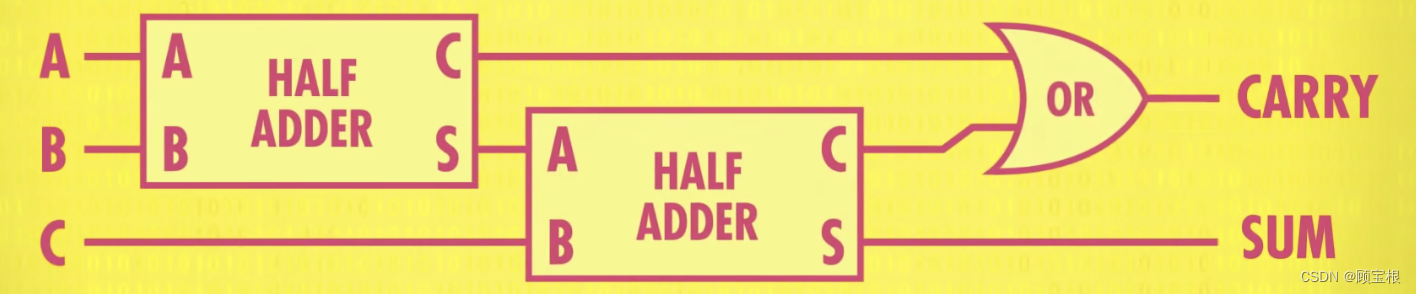

full adder: “全加器”

考虑到进位,所以全加器得由三个数字分两个半加器相加,最大的情况是1+1+1,也只进1位,所以,or门判断carry(进位)就行,只要存在进位,那就是进1位;

第一个半加器由a,b两个底数相加,得到进位carry和低位sum,sum再和上一位相加得的进位carry相加,得到最终的sum,以及第二个可能得carry,两个carry经过or门就可以判断这一位的相加有没有产生进位。

造完了half adder 和 full adder,就可以造一个大的,8-bit ripple carry adder,8位进位加法器!

从低位开始相加,第一位采用半加器,因为第一次相加不存在进位c,

而后续的相加都要考虑进位,当然要考虑最高位的相加是否产生进位,即overflow,溢出的情况

当然加入更多的adder可以进行更多位的相加

其他功能也是由最基本的逻辑门组合起来,这些功能的组合就形成了ALU

an arithmetic unit and a logic unit

another level of abstraction! 又一层次的抽象出 ALU,如图

operation code 即指令代码,如1000代表加法,1100代表减法

上侧是两个输入的八位bit的数,将进行指令代码所代表的处理

输出在下方,右侧是一些标识,overflow是代表是否溢出,zero表示是否为0,negative表示结果是否为负数

这就是一个ALU了,离CPU近了一步~

要理解CPU,那一定先要了解内存,即memory

顾名思义,memory是一种存储,也分为random access memory 和 persistent memory

前者是通电有,断电无的RAM,后者是持续性的存储,应该为硬盘之类

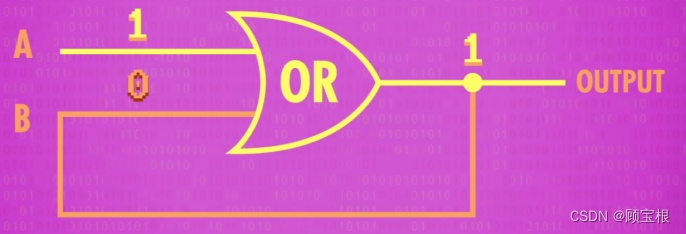

先尝试着存储一个bit

如图在or门上加一条回路,一旦A输出过1之后,再改变A的输入,将不会改变output了,即存储了1

这个模型则可以存储0,将上述两个模型结合,得到and-or latch 锁存器,可以存储1或者0

但这个模型需要两根输入线,一根set(上侧) 一根reset(下侧)

set输入线输入1,则output1(reset不动为0);

在输出为1的情况下,reset输入1,则直接让output变回0;

这个模型即可存储1或者0了,且可以set和reset

this is called a "latch" because it "latches onto" a particular value and stays that way.

The action of putting data into memory is called wriiting,

whereas getting the data out is called reading.

把数据放入内存的行为称为写

把数据从内存里拿出的行为叫做读

但是这个结构需要两根不同的线,可以继续优化,最好一根线就可以控制数据的输入

优化后:

再封装抽象得:

这下真的有了一个很屌的工具 latch,可以存储一位bit了!! 离memory内存已经很近了!!

* a group of latches operating like this is called a register,

which holds a single number, and the number of bits in a register is called its widith

一组latches(锁存器)像这样运行,即组合成了寄存器,即皇帝(cpu)身边负责端水送茶递奏章的小太监!

一个寄存器中可存储的位数即为它的宽度

写入线可以共用一根,但数据输入和输出线每个latch都需要,所以这种结构其实很费线

比如256-bit的寄存器,则需要1根写入线,256根数据输入线,256根输出线,总513根线

继续优化!采用矩阵的方法来定位锁存器,采用横纵坐标的方式来激活一个锁存器的读写操作

如图,横纵两条线连起一个and门,只有这两根线都通电,读写操作才可以进行,也就是通过横纵两线定位到了这个即将被操作的锁存器来存储1位bit

而同一时间只会操作一个锁存器,所以可读线,可写线,包括数据线都可以共用一根!

用256-bit的memory打比方纵观全局,还涉及到多路复用器这种工具,如下图:

这样,对于256-bit memory,线就由500多根优化到了 16+16(定位线)+3(可读线,可写线,数据输入线) = 35根

而行地址和列地址都可以分别用4个bit来定位,所以一组8位bit就可以定位16*16中的一个坐标

所以可以再连8根定位坐标的线,那这个家伙已经很完整了,已经是一个小型的memory了

将其抽象包装,得到:

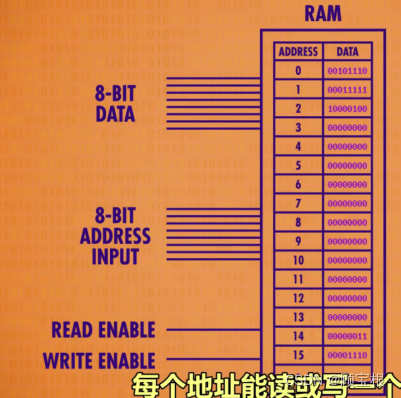

OK,再总结一下,对于这个家伙,8位地址可以找到256个lacth(锁存器)中的任意一个进行操作,允许写入线和读取线控制了其能否被操作,data线将数据写入!

放心,还会继续组合,继续抽象!

将上述已经造出来的256-bit memory 进行组合,将8个这样的memory组合得到:

8根地址定位线共用,读写线也共用,等于说,在这个组合中,一个8-bits的数据分别在每个memory存放一个bit,即在这8个memory中分别存放了一个bit,且因为地址线共用,存放的具体坐标是一样的!

即,这个大家伙可以存放 256 个 8-bits的数据!

ok,给它抽象包装简化一下,得到:

ohhhhhhh~ 得到了RAM,这个RAM有256个地址,每个地址可存放一个8-bits data!

慢慢的由晶体管到逻辑门到加法器到ALU进而到了存储器,锁存器,寄存器,memory,到现在一步步组合起来的RAM,感叹计算机之路上诸位大佬神仙的神来之笔!

3982

3982

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?