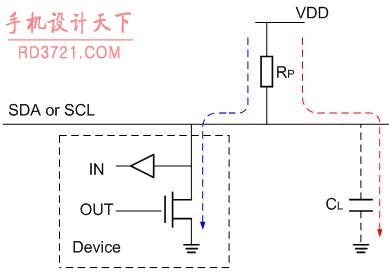

1.信号线上拉电阻

虽然某些芯片引脚内部具有上拉功能,但其一般是弱上拉,容易受到外部干扰,所以在设计I2C电路时务必添加外部上拉电阻Rp,并根据实际使用情况更改阻值。

当Rp阻值过小时,VDD灌入端口的电流过大(一般IO口的驱动能力在2mA~4mA量级,VDD为3V时灌入电流不得超过3mA),MOS管不完全导通,由饱和状态变为放大状态,输出的低电平增大(I2C协议规定端口低电平最高允许值为0.4V);

由于I2C端口一般工作在开漏模式下,无法直接输出高电平,而是电源通过Rp对线上负载电容Cl进行充电将端口拉高,当Rp阻值过大时,时间常数Rp*Cl增大,上升时间增加,可能导致输出的方波变成三角波。

Rp=(VDD - 0.4V) / 0.3mA——VDD:I2C电源电压(通常为5V或3.3V)

通常取值范围1k-10k,常用1.2k、2.2k、4.7k。

注意:

a.SCL和SDA两条线上的上拉电阻阻值相等并上拉到同一电源上。

b.上拉电阻靠近OD输出端:当主从设备都为OD模式时,上拉电阻放在信号线中间位置;当主设备为软件模拟I2C通讯,从设备为OD模式时,上拉电阻放在靠近从设备位置。

2.信号线负载电容

| 通信速率(kbps) | 负载电容上限(pf) |

| 100 | 400 |

| 400 | 200 |

3.信号线串联电阻(通常取值100~200欧)

a. 阻抗匹配,减少信号反射

b.在恶劣环境中,有效抑制总线上的干扰脉冲。

参考:https://blog.csdn.net/zyboy2000/article/details/5789005

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?