1 结构

-

- 概述

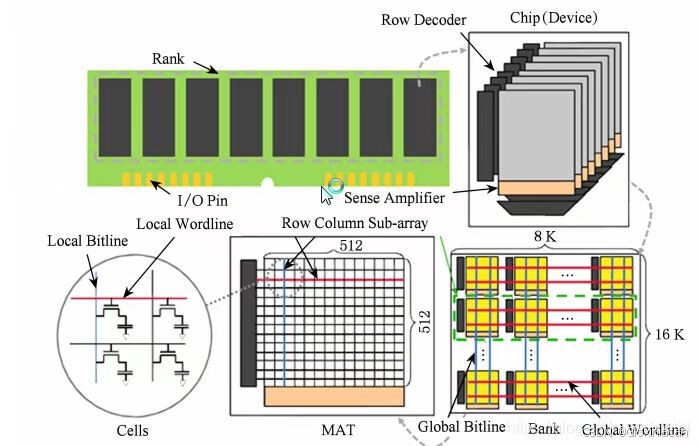

DDR是一种易失性存储器,需要定期刷新以保留数据,下电后则数据丢失。从系统层面,DDR的结构为:channelàDIMMàrankàbank group(BG) àbankàMAT àcell,如下图所示。

图 DDR结构层次图

Channel是内存控制器(memory controller)与内存模块之间的独立数据路径。一个MC可以支持一个或多个channel,一个channel可以支持一个或多个内存模块。DIMM(dual inline memory modual,双列直插内存模块)是内存模块的一种,其上可排布1或2个rank。Rank由一组chip/device组成。每个chip包含多个bank,为便于区分,将这些bank分为数组bank group(BG)。每个bank包含多个MAT(memory array tile)。每个MAT由一定行列的cell组成。在DDR4中,一个MAT有65536行,1024列。同一bank不同MAT的cell行列地址相同。

Cell是DDR的基本单元,是1T1C结构,即一个访问晶体管和一个存储电容。用电容存储的电荷量区分状态0和状态1,通过访问晶体管来控制电容器的充放电。通常情况下,认为电容存储电荷表示逻辑1,没有电荷表示逻辑0,我们将其称为“正逻辑”。但实际上,有的厂家会对部分阵列采用电容存储电荷表示逻辑0,没有电荷表示逻辑1的“负逻辑”;甚至正负逻辑交错排布。

-

- 演进过程

- 访问晶体管

- 演进过程

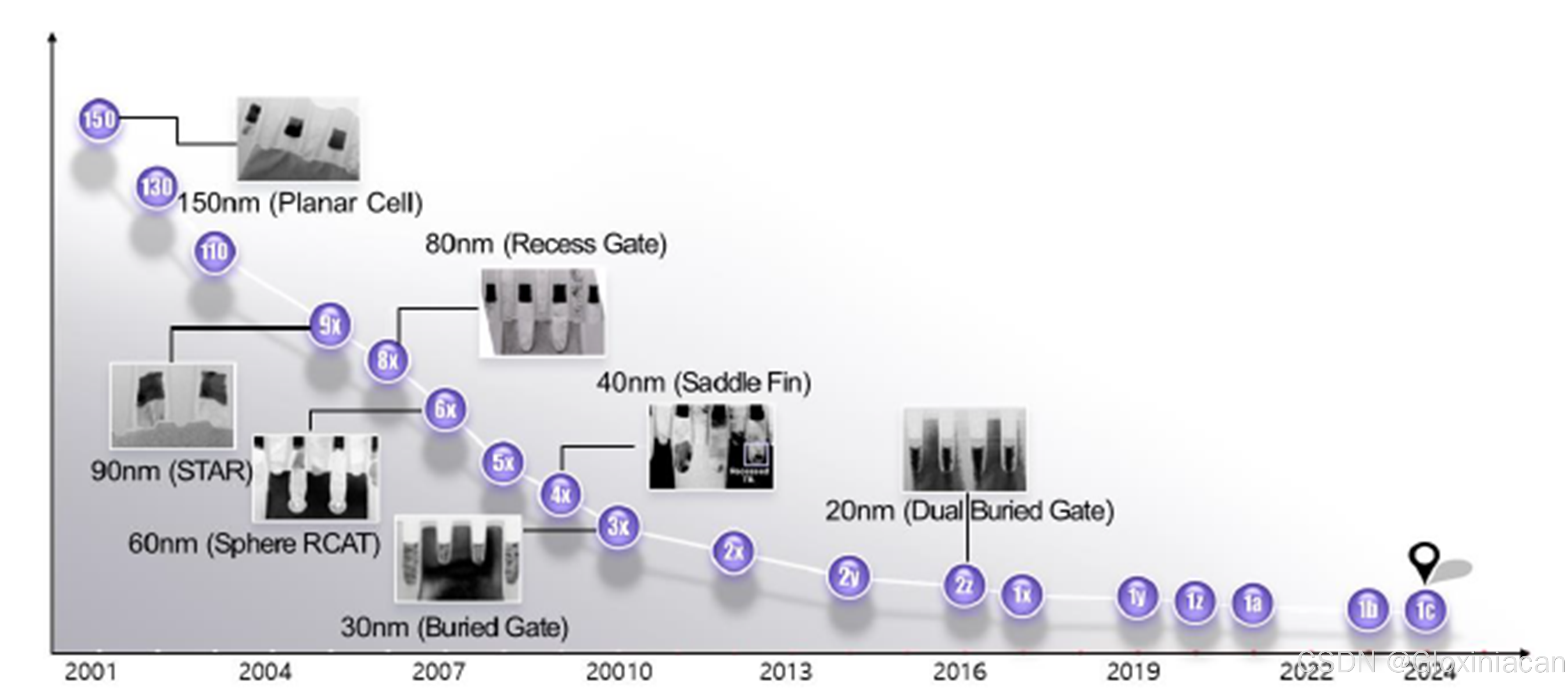

1990年代后期,访问晶体管采用传统平面型结构。由于尾部晶体管的漏电流是导致DRAM retention特性恶化的主要因素,即GIDL电流,因此后续工作围绕减小GIDL电流进行。在100nm节点,由于短沟道效应和高电场,平面型晶体管的GIDL效应难以控制,故提出STAR阶梯型结构。由于STAR结构对套刻精度的高要求,以及工艺节点微缩带来的短沟道效应,提出RCAT结构(recess channel array transistor)。RCAT结构通过弧形栅极延长了沟道长度,同时降低了沟道掺杂浓度。但随节点微缩,沟道曲率快速增加,栅极对沟道控制力减弱,DIBL和体效应严重,RCAT结构进一步演化为S-RCAT结构。S-RCAT结构缓解了曲率问题,但不可避免的间隙和球间距的快速缩小使其最终被鞍鳍晶体管(saddle fin)取代。Saddle Fin结构有效降低了DIBL和体效应,一直沿用至10nm节点,是目前的主流。

图 近25年DRAM技术节点和工艺演进

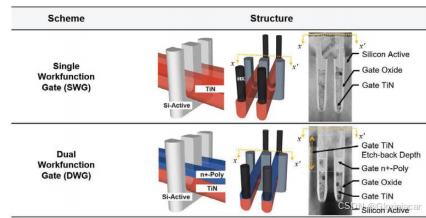

Buried gate(BG):弧形栅极较大的结/栅极重叠区导致GIDL现象,因此引入埋入式栅极(BG)。但这种结构会导致操作电流的突然下降,故SWG结构演变为DWG结构,如下图所示。DWG控制了GIDL的同时保证了足够的操作电流,沿用至今。

图 栅极演进

-

-

- 感应裕量

-

过去25年来,存储电容体积的减小导致其容量减小了90%,但器件retention特性基本不变。这一方面归功于BG结构对GIDL电流的良好控制,一方面是对感应裕量的优化,后者包括对存储电容、感应放大器(sense amplifier, SA)等的优化。

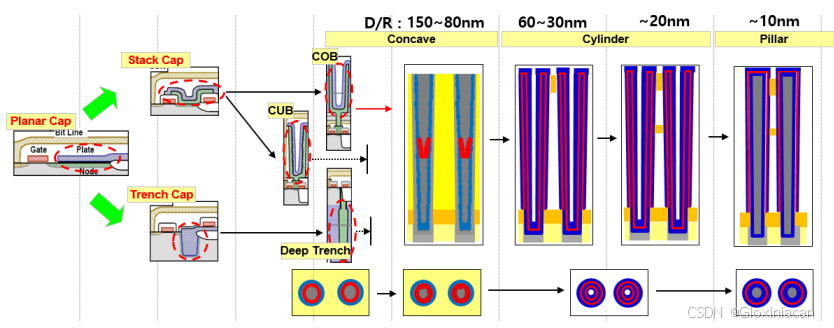

存储电容:

存储电容的演进可以分材料和结构两方面。在发展趋势上,采用high-k材料和大表面积是存储电容的演进方向。由于节点微缩,其结构从传统平面型经历堆叠型、沟槽型,再演变为类似3D NAND的柱形电容,如下图所示。显然cylinder型电容具有更大的表面积,但由于内部填充困难,因此最终被pillar型取代。和NAND一样,高纵横比是其进一步发展的挑战。

图 存储电容结构演进

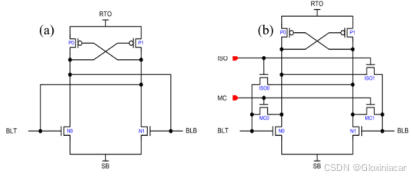

感应放大器:(仅在SK hynix的文章中见过,可能是其独有结构)

将原本的4T SA优化为8T MCSA(mismatch cancellation SA),大幅减小了DRAM单元对不匹配的偏移量。

图 SA结构优化

-

-

- Bitline结构

-

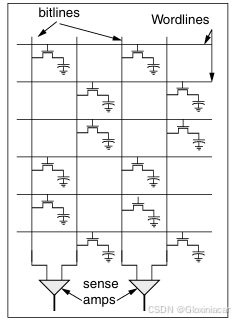

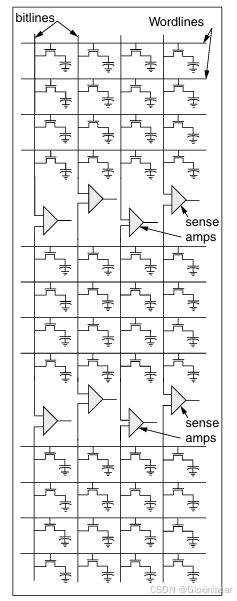

DRAM SA的两端需要连接两个互补cell。最初这两个cell是来自同一MAT的相邻cell,即folded BL结构。这样的单元对抗噪性较好,但cell间不够紧凑(8F2,feature size,表征单个cell的area)。位节省面积,后续采用open BL结构,即同一SA的两个cell来自同一bank不同MAT。Open BL抗噪性略差,但结构紧凑,可以实现6F2的密度,是目前主流结构。

图 folded BL

图 open BL

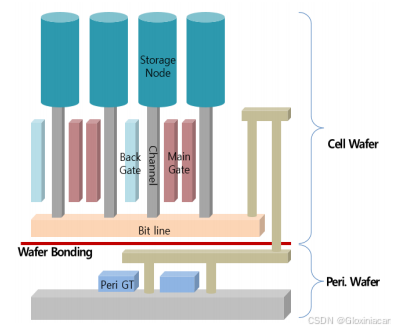

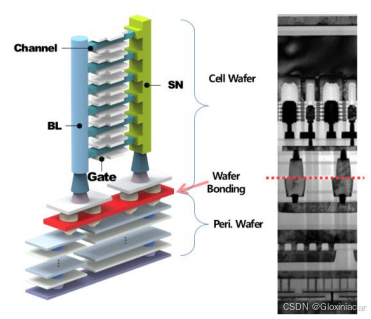

DRAM未来演进方向:正在探索各种6F2向4F2单元密度演进的方案。如采用VGT结构(vertical gate transistor),channel以垂直方式直接位于BL上;3D DRAM,目前百家争鸣,方案众多,下图给出其中一种。

图 VGT结构

图 3D DRAM

- 读写

2.1 cell级读写

1. Precharge: EQ加压VCC使对呀均衡电路Te1 Te2 Te3导通,将BL/BL’稳定到Vref=VDD/2。

2. Access:将WL加压到VDD,导通Ta,存储电容和BL之间的压差引起BL电压的轻微波动。

3. Amplify:SAN、SAP分别加压0、VDD。由于存储电容值远小于BL寄生电容值(通常在10倍以上),因此需要感应放大电路。通过SA电路,BL电压将被稳定到逻辑0或逻辑1。

4. Read:CSL使能,Tc1、Tc2导通,从而读出数据。

5. Write recovery:数据读出后,BL电压会向存储电容充/放电,以恢复被破坏性读出的数据。如果是写操作,则使能WE信号,write driver输入的数据会覆盖BL原有信号,从而实现数据写入。

图 cell读写结构

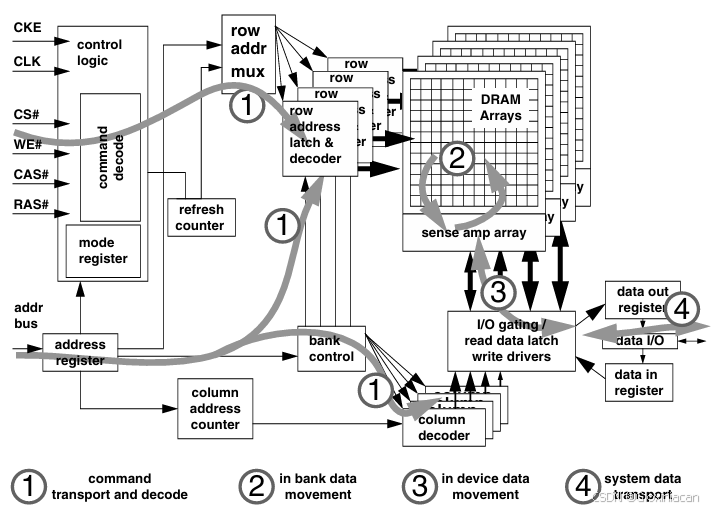

2.2 系统级读写

1. command transport and decode:DDR controller(DDRC)通过command bus和address bus将命令传输到DRAM。DRAM对命令进行解析,其中地址相关的命令经行列译码器处理,得到具体地址。

2. in bank data movement:DRAM选中特定的row,将数据读出到SA,或将数据经SA写入cells。

3. in device data and movement:特定列的数据通过I/O电路缓存到read latch,或将数据通过I/O电路和write driver更新到特定列的SA。

4. system data transport:将读出的数据传输到data bus,或将待写入的数据经DDRC传输到data bus。

图 系统级读写过程

参考来源:

[1] Yoo M, Lee S, Son A, et al. DRAM Technology & Design Optimization for Sub-10nm and Beyond[C]//2024 IEEE International Electron Devices Meeting (IEDM). IEEE, 2024: 1-4.

[2] Memory Systems - Cache, DRAM, Disk

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?