提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

Xilinx FPGA资源解析与使用系列——Transceiver(十一)transceiver与用户数据的接口

接口协议

前面的文章基本都在讲transceiver里面的内部结构,这篇文章主要讲transceiver与用户逻辑数据的接口,也就是要如何使用transceiver发过来的数据。

与用户逻辑的接口与传输过程中使用的编码有关,有两种编码方式:

1、8B/10B

2、64B/66B

以及

3、NONE

就是直接传输裸的数据,当然这个数据需要提前做好随机序列化,也就是大部分工作通过自己写逻辑完成

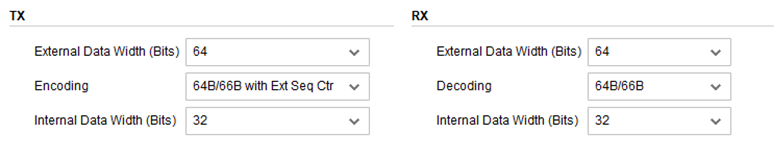

在IP核中有如下选项相关

在实际使用场景中:

JESD204B使用的是8B/10B编码

JESD204C、某些CPRI协议使用的是64B/66B编码。

尽管在IP选项卡中Encoding的选项卡存在

1、 NON

本文详细介绍了Xilinx FPGA Transceiver与用户逻辑数据接口,重点讨论了64B/66B编码方式。内容包括8B/10B和64B/66B编码的使用场景,以及TX和RX Gearbox的不同操作模式。特别强调了64B/66B with Ext Seq Ctr模式下的接口信号如TXDATA、TXHEADER和TXSEQUENCE,并解释了块同步和头部检测在RX Gearbox中的重要性。

本文详细介绍了Xilinx FPGA Transceiver与用户逻辑数据接口,重点讨论了64B/66B编码方式。内容包括8B/10B和64B/66B编码的使用场景,以及TX和RX Gearbox的不同操作模式。特别强调了64B/66B with Ext Seq Ctr模式下的接口信号如TXDATA、TXHEADER和TXSEQUENCE,并解释了块同步和头部检测在RX Gearbox中的重要性。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?