数据接口

串行时钟频率可高达 50MHz,使 DAC7565 与高速 DSP 兼容。在串行时钟的第 24 个下降沿,最后一个数据位被输入移位寄存器并且移位寄存器锁定。进一步的时钟不会改变移位寄存器的数据。24 位被锁定到移位寄存器后,8 个 MSB 用作控制位,后面的 12 个 LSB 用作数据。在接收到第 24 个时钟下降沿后,DAC7565 解码 8 个控制位和 12 个数据位以执行所需的功能,而无需等待 /SYNC 上升沿。

24 位序列完成前的 /SYNC 上升沿复位 SPI 接口;不会发生数据传输。在收到 SCLK 的第 24 个下降沿后,/SYNC 线可能保持低电平或拉高。无论哪种情况,必须满足从第 24 个 SCLK 下降沿到下一个 /SYNC 下降沿的最小延迟时间,才能正确开始下一个周期。为确保器件的最低功耗,应注意电平尽可能靠近每个轨道。请参阅图 36、图 57 和图 79(电源电流与逻辑输入电压)的典型特性部分。

IOVDD

IOVDD 引脚为 DAC7565 的数字输入结构供电。对于单电源操作,它可以连接到 AVDD。对于双电源操作,IOVDD 引脚提供了与各种 CMOS 逻辑系列的接口灵活性,并且应该连接到系统的逻辑电源。 DAC7565 的模拟电路和内部逻辑使用 AVDD 作为电源电压。外部逻辑高输入通过电平转换器转换为 AVDD。这些电平转换器使用 IOVDD 电压作为参考,将输入的逻辑高电平转换为 AVDD。无论 AVDD 电压如何,IOVDD 都能确保在 2.7V 至 5.5V 范围内工作,从而确保与各种逻辑系列的兼容性。虽然规定低至 2.7V,但 IOVDD 在低至 1.8V 的情况下工作,时序和温度性能下降。为获得最低功耗,逻辑 VIH 电平应尽可能接近 IOVDD,逻辑 VIL 电平应尽可能接近 GND 电压。

异步复位( / 代表低电平)

在 /RST 引脚被拉低后,DAC7565 输出立即异步设置为零电平电压或中间电平电压(取决于 RSTSEL)。/RST 信号复位所有内部寄存器,因此,其行为类似于上电复位。 /RST 引脚必须在写入序列开始之前恢复为高电平。如果 RSTSEL 引脚为高电平,则 /RST 信号变为低电平会将所有输出重置为中量程。如果 /RSTSEL 引脚为低电平,则 /RST 信号变为低电平会将所有输出重置为零电平。RSTSEL 应在上电时设置。

输入寄存器

DB18 和 DB17 选择的 DAC 对应的数据缓冲器和 DAC 寄存器随着 SR 数据的内容(或断电)更新。

DB18 和 DB17 选择的通道用 SR 数据更新;同时,所有其他通道都使用数据缓冲区中先前存储的数据(或断电)进行更新。

SYNC 中断

在正常的写入序列中,/SYNC 线在 SCLK 的至少 24 个下降沿保持低电平,并且寻址的 DAC 寄存器在第 24 个下降沿更新。但是,如果 /SYNC 在第 24 个下降沿之前被拉高,则它充当写序列的中断;移位寄存器复位并且写序列被丢弃。数据缓冲区内容、DAC 寄存器内容都不会更新,操作模式也不会发生变化(如图 95 所示)。

上电复位电路

DAC7565 包含一个上电复位电路,可在上电期间控制输出电压。根据 RSTSEL 信号,上电时,DAC 寄存器被复位,输出电压设置为零电平 (RSTSEL = 0) 或中间电平 (RSTSEL = 1);它们保持这种状态,直到对相应的 DAC 通道发出有效的写入序列和加载命令。上电复位适用于需要在设备上电过程中了解每个 DAC 输出状态的应用。

在将电源施加到设备之前,不应将任何设备引脚拉高。默认情况下,内部参考上电并保持这种状态,直到执行有效的参考更改命令。

使能引脚

对于正常操作,使能引脚必须驱动为逻辑低电平。如果使能引脚被驱动为高电平,则 DAC7565 停止侦听串行端口。但是,SCLK、/SYNC 和 DIN 不能保持悬空,而必须处于某个逻辑电平。此功能对于共享相同串行端口的应用程序很有用。

掉电模式

DAC7565 有两组独立的断电命令。一组用于 DAC 通道,另一组用于内部参考。更多

有关关闭参考的信息,请参阅启用/禁用内部参考部分。

DAC 掉电命令

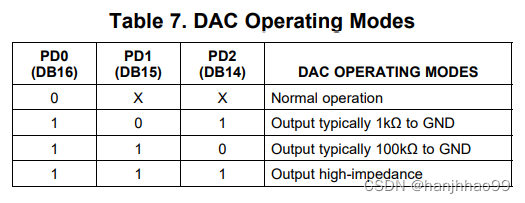

DAC7565 使用四种操作模式。通过设置移位寄存器中的三个位(PD2、PD1 和 PD0)来访问这些模式。表 7 显示了如何使用数据位 PD0 (DB16)、PD1 (DB15) 和 PD2 (DB14) 控制操作模式。

DAC7565 将掉电情况视为数据;所有操作模式在掉电时仍然有效。可以向系统中的所有 DAC7565 广播掉电情况;还可以在更新其他通道上的数据的同时关闭一个通道。

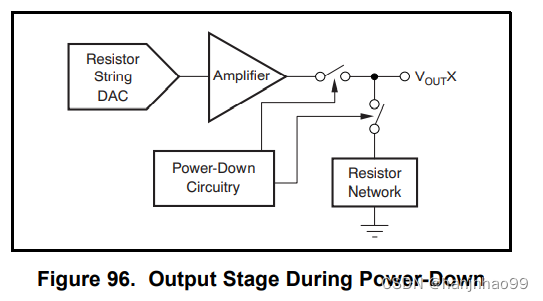

当 PD0 位设置为“0”时,器件正常工作,其典型电流消耗为 1mA,5.5V,输入代码 = 2048。参考电流包含在所有四个 DAC 的操作中。然而,对于三种断电模式,电源电流在 5.5V 时降至 1.3μA(在 3.6V 时为 0.5μA)。不仅电源电流下降,而且输出级也在内部从放大器的输出切换到已知值的电阻网络。

这种切换的优点是器件的输出阻抗在其处于断电模式时是已知的。如表 7 所述,共有三种不同的断电选项。 VOUT 可通过一个 1kΩ 电阻、一个 100kΩ 电阻或开路 (High-Z) 在内部连接到 GND。输出级如图 96 所示。换句话说,DB16、DB15 和 DB14 = '111' 表示所选通道的高阻抗输出阻抗的断电条件。 “101”表示输出阻抗为 1kΩ 的断电条件,“110”表示输出阻抗为 100kΩ 的断电条件。

执行掉电模式时,所有模拟通道电路都将关闭。但是,掉电时 DAC 寄存器的内容不受影响。 VDD = 5V 时退出掉电所需的时间通常为 2.5μs,VDD = 3V 时为 5μs。有关详细信息,请参阅典型特征。

内部参考电压

DAC7565 的内部基准不需要外部负载电容来保持稳定性,因为它可以在任何容性负载下保持稳定。但是,为了提高噪声性能,建议将 150nF 或更大的外部负载电容连接到 VREFH/VREFOUT 输出。 图 97 显示了 DAC7565 内部基准运行所需的典型连接。 还建议在 AVDD 输入端使用电源旁路电容。

供电

内部基准具有极低压差电压。 在空载条件下,它可以在仅高于参考输出电压 5mV 的电源下运行。 对于负载条件,请参阅负载调节部分。 内部基准电压随电源电压变化(线路调节、直流 PSRR)的稳定性也非常出色。 在 2.7V 至 5.5V 的规定电源电压范围内,VREH/VREFOUT 的变化小于 10uV/V;请参阅 Typical 特性。

1418

1418

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?