目录

1.课题概述

基于FPGA的AES加解密系统verilog实现,包含testbench和开发板硬件测试。输入待加密数据,密钥,输出加密数据,然后通过解密模块输出解密后的原数据。

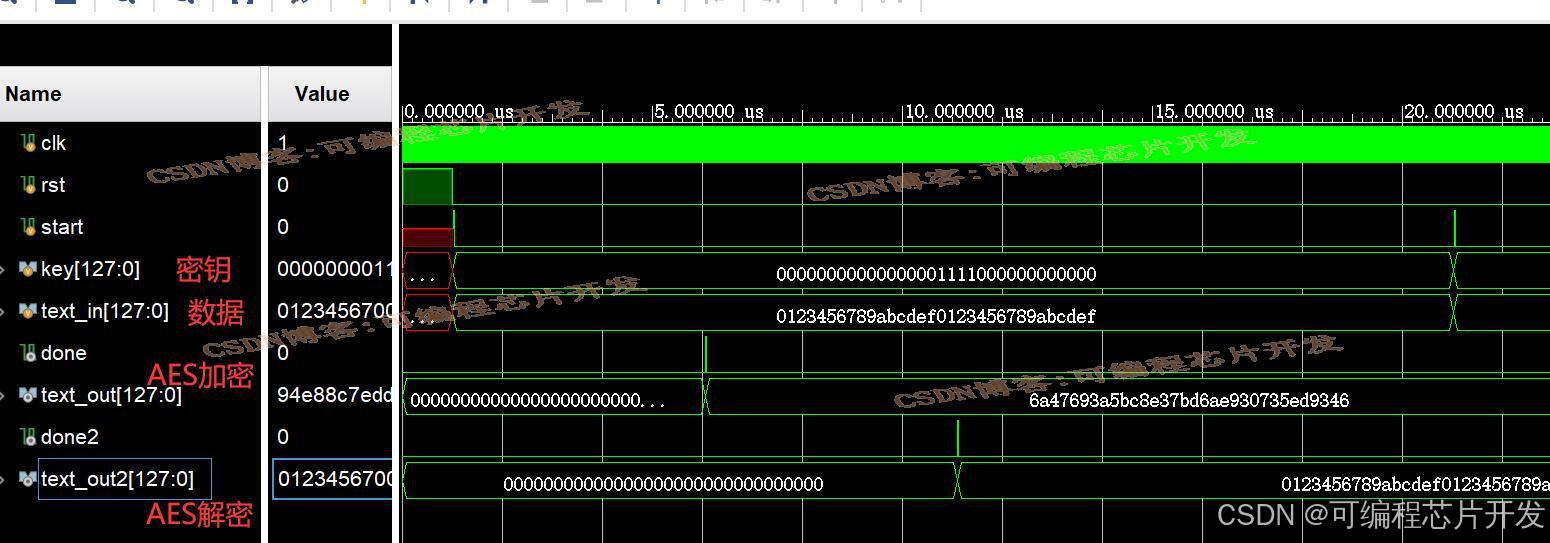

2.系统测试效果

仿真测试

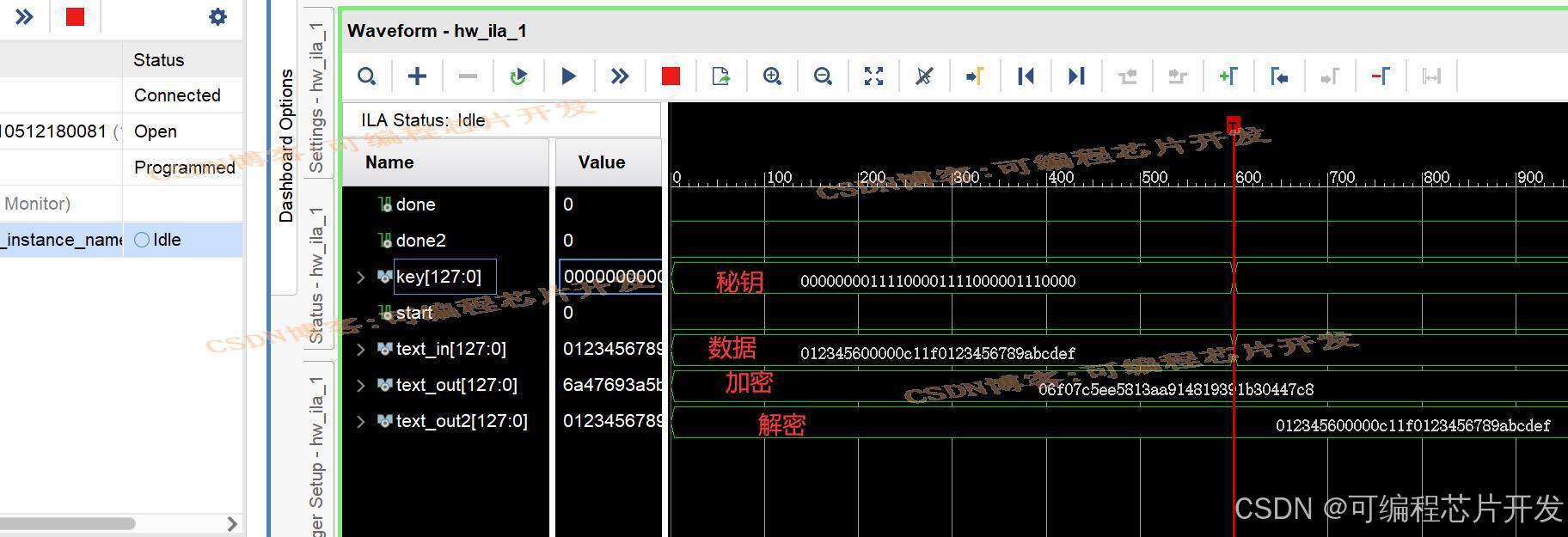

硬件测试

在实际测试过程中,如果你的开发板和我的不一样,可以参考本博客置顶文章进行硬件配置修改:

FPGA系统开发板调试过程不同芯片的移植步骤介绍_紫光fpga移植软核的步骤-CSDN博客

通过这个链接的步骤,可以实现不同开发板上的系统调试。

3.核心程序与模型

版本:vivado2022.2

`timescale 1ns / 1ps

module tops_hw(

input i_clk,

input i_rst,

output led

);

reg[15:0]cnt;

always @(posedge i_clk or negedge i_rst)

begin

if(~i_rst)

begin

cnt<=16'd0;

end else

begin

if(cnt==16'd60000)

cnt<=16'd1;

else

cnt<=cnt+16'd1;

end

end

reg start;

reg[127:0]key;

reg[127:0]text_in;

always @(posedge i_clk or negedge i_rst)

begin

if(~i_rst)

begin

start <=1'd0;

key <=128'd0;

text_in <=128'd0;

end else

begin

if(cnt==16'd1 | cnt==16'd20001 | cnt==16'd40001)

start <=1'd1;

else

start <=1'd0;

if(cnt==16'd1)

begin

text_in <= 128'h0123_4567_89ab_cdef_0123_4567_89ab_cdef;

key <= 128'h0000_0000_0000_0000_1111_0000_0000_0000;

end

if(cnt==16'd20001)

begin

text_in <= 128'h0123_4567_0000_cdef_0123_4567_89ab_cdef;

key <= 128'h0000_0000_1111_0000_1111_0000_0000_0000;

end

if(cnt==16'd40001)

begin

text_in <= 128'h0123_4560_0000_c11f_0123_4567_89ab_cdef;

key <= 128'h0000_0000_1111_0000_1111_0000_0111_0000;

end

end

end

wire done;

wire [127:0] text_out;

wire done2;

wire [127:0] text_out2;

aes_tops aes_tops_jiam(

.Clock (i_clk),

.Reset (~i_rst),

.loads (start),

.enc_dec (1'b0),

.din (text_in),

.FEK (key),

.Ready (),

.dout (),

.Ready_Valid (done),

.douts_Valid (text_out)

);

aes_tops aes_tops_jiem(

.Clock (i_clk),

.Reset (~i_rst),

.loads (done),

.enc_dec (1'b1),

.din (text_out),

.FEK (key),

.Ready (),

.dout (),

.Ready_Valid (done2),

.douts_Valid (text_out2)

);

assign led= done2;

ila_0 your_instance_name (

.clk(i_clk), // input wire clk

.probe0({

start,text_in,key,

done,text_out,

done2,text_out2

}) // input wire [519:0] probe0

);

endmodule

00X6_002m4.系统原理简介

AES是一种分组密码算法,它将明文数据分成固定大小的分组(通常为 128 位),并使用一个密钥对这些分组进行加密。AES支持的密钥长度有128位、192位和256位,不同的密钥长度对应不同的加密轮数,分别为10轮、12轮和14轮。

AES加密过程主要包括初始轮、多轮迭代和最终轮。每一轮迭代都包含四个基本操作:字节替换(SubBytes)、行移位(ShiftRows)、列混合(MixColumns)和轮密钥加(AddRoundKey)。

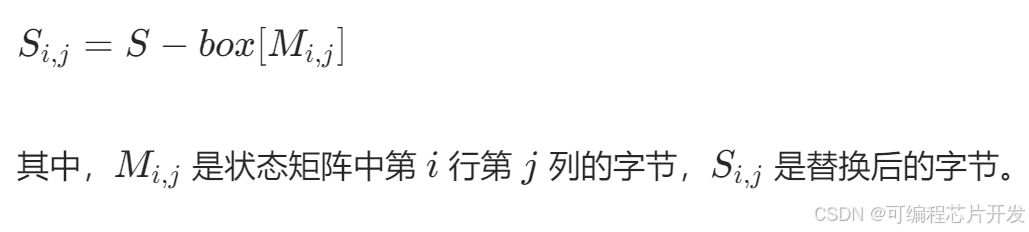

4.1 字节替换(SubBytes)

字节替换操作是一个非线性替换操作,它将状态矩阵中的每个字节通过一个固定的S盒进行替换。S 盒是一个16×16的字节替换表,它是通过有限域GF (2^8)上的逆运算和仿射变换得到的。数学公式为:

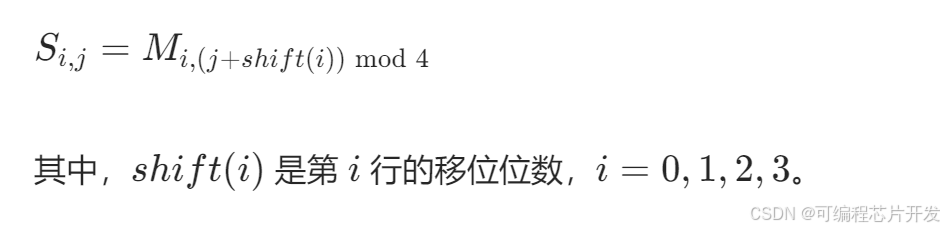

4.2 行移位(ShiftRows)

行移位操作将状态矩阵的每一行循环左移不同的位数。第一行保持不变,第二行左移1个字节,第三行左移2个字节,第四行左移3个字节。数学公式为:

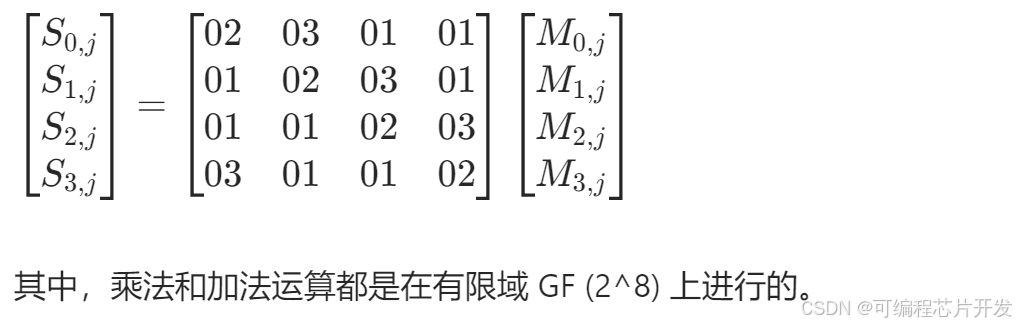

4.3 列混合(MixColumns)

列混合操作是一个线性变换,它将状态矩阵的每一列与一个固定的矩阵进行矩阵乘法运算。这个固定矩阵是在有限域GF (2^8)上定义的。数学公式为:

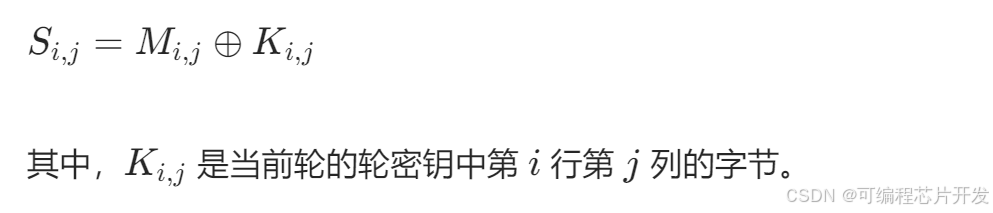

4.4 轮密钥加(AddRoundKey)

轮密钥加操作将状态矩阵与当前轮的轮密钥进行逐位异或运算。数学公式为:

AES解密过程是加密过程的逆过程,它包括初始轮、多轮迭代和最终轮。每一轮迭代包含逆字节替换(InvSubBytes)、逆行移位(InvShiftRows)、逆列混合(InvMixColumns)和轮密钥加(AddRoundKey)。

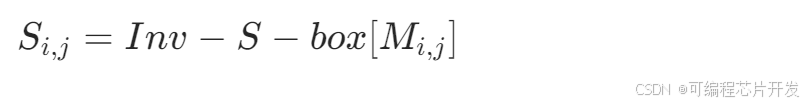

4.5 逆字节替换(InvSubBytes)

逆字节替换操作是字节替换操作的逆操作,它使用逆S盒进行替换。数学公式为:

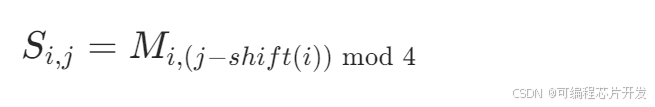

4.6 逆行移位(InvShiftRows)

逆行移位操作是行移位操作的逆操作,它将状态矩阵的每一行循环右移不同的位数。数学公式为:

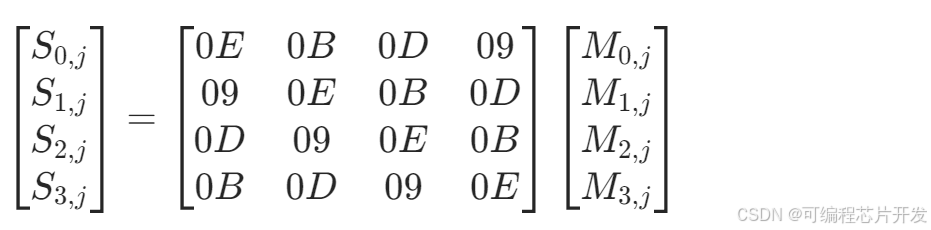

4.7 逆列混合(InvMixColumns)

逆列混合操作是列混合操作的逆操作,它将状态矩阵的每一列与一个固定的逆矩阵进行矩阵乘法运算。数学公式为:

4.8 轮密钥加(AddRoundKey)

轮密钥加操作与加密过程中的轮密钥加操作相同,都是逐位异或运算。

5.完整工程文件

v

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?