续【AD9361 数字接口CMOS &LVDS&SPI】B 并行数据之CMOS

数据总线空闲和周转周期 (CMOS)

P0_D[11:0]和P1_D[11:0]总线信号通常由BBP或AD9361有源驱动。在任何空闲期间,两个组件都会忽略数据总线值。但是,这两个端口必须具有有效的逻辑电平,即使它们未使用也是如此。

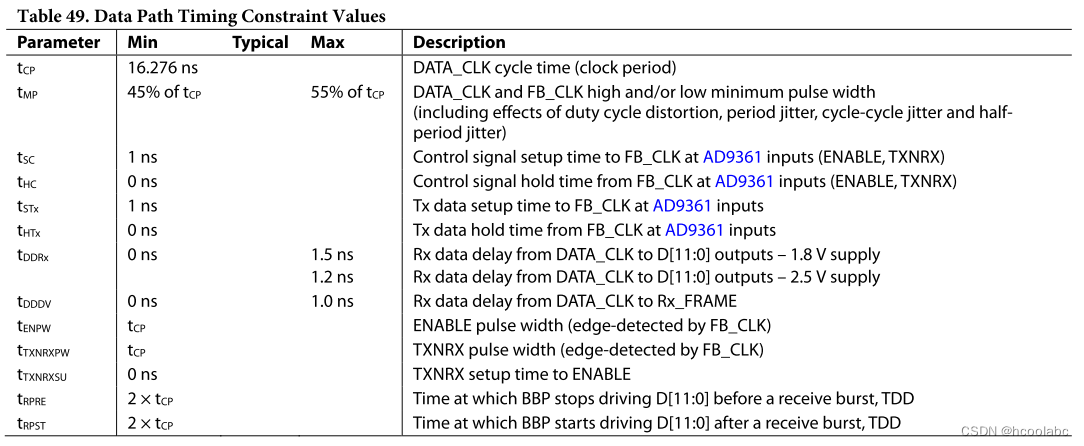

数据路径时序参数 (CMOS)

下表的时序参数用于在AD9361与BBP接口时提供指导。

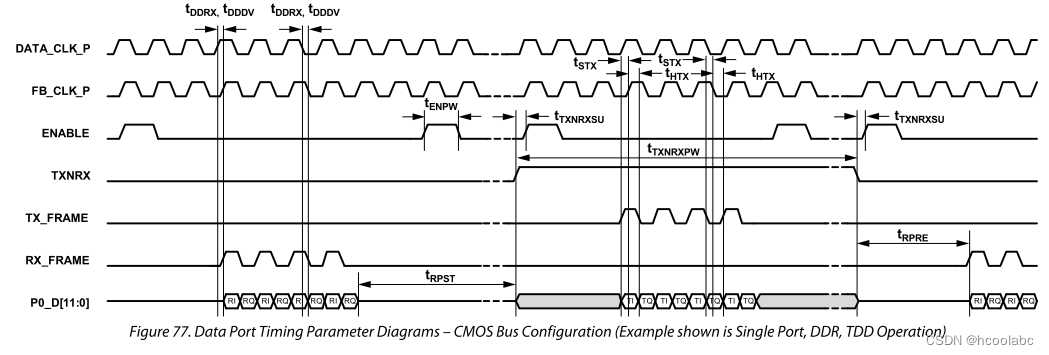

下图显示了数据时钟和硬件控制输入之间的关系。

图 77 显示了所有其他参数之间的关系。

参考源文件 :《UG-570 AD9361 Reference Manual 》

参考源文件 :《UG-671 AD9361 Register Map Reference Manual》

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?