【AD9361 数字接口CMOS &LVDS&SPI】D部分 接续

【AD9361 数字接口CMOS &LVDS&SPI】A 并行数据CMOS

串行外设接口(SPI)

SPI总线为AD9361的所有数字控制提供机制。每个SPI寄存器的宽度为8位,每个寄存器包含控制位、状态监视器或其他控制器件所有功能的设置。以下介绍此接口的细节。

SPI功能层

可以通过在SPI配置寄存器中设置位值来配置SPI总线。该寄存器是对称的;即 D6 等效于 D1,D5 等同于 D2(D4 和 D3 未使用)。该器件在上电时的默认模式为MSB优先寻址,但由于这种对称性,可以接受对SPI配置寄存器的LSB优先写入。对称位是或在一起的,因此设置一个位会在对中设置两个位。当 D5 和 D2 保持低电平时,位顺序为 MSB 优先,而当置高电平时,位顺序交换为 LSB 优先。正确配置后,所有后续寄存器写入都必须遵循所选格式。

默认情况下,总线配置为 4 线接口。如果 D6 和 D1置为高电平,则 SPI 总线配置为 3 线接口。

D7 和 D0 在置高时将所有寄存器异步复位为默认值,并且必须先清除这些位,然后才能更改其他寄存器。

以下将介绍每个SPI总线信号。

[1] SPI_ENB

SPI_ENB是从BBP驱动到AD9361的总线使能信号。SPI_ENB在第一个SPI_CLK上升沿之前被驱动为低电平,通常在最后一个SPI_CLK下降沿之后再次被驱动为高电平。AD9361在SPI_ENB为高电平时忽略时钟和数据信号。如果AD9361是SPI总线上唯一的器件,则可以SPI_ENB连接为低电平。

当该输入为高电平时,SPI_DO 和 SPI_DI 引脚转换至高阻抗状态。如果在任何通信周期内被驱动为高电平,则该周期将暂停,直到SPI_ENB重新激活为低电平。

[2] SPI_CLK

SPI_CLK是由BBP驱动到AD9361的接口参考时钟。它仅在SPI_ENB低时处于活动状态。最大SPI_CLK频率为 50 MHz。

[3] SPI_DI、SPI_DO和SPI_DIO

配置为4线式总线时,SPI利用两个数据信号:SPI_DI和SPI_DO。 SPI_DI是从BBP驱动到AD9361的数据输入线,SPI_DO是从AD9361到BBP的数据输出。

配置为 3 线总线时,SP_DI 用作接收和发送串行数据的双向数据信号。在3线配置中,该信号在本节中称为SP_DIO,以区分这两种配置。

数据信号在SPI_CLK的上升沿发射,并由BBP和AD9361在SPI_CLK的下降沿进行采样。SPI_DI(或SPI_DIO)在所有事务期间将控制字段从BBP传送到AD9361,并在写入事务期间将写入数据字段传送到AD9361。SPI_DO(或SPI_DIO)在读取事务期间将返回的读取数据字段从AD9361传送到BBP。

AD9361在这些引脚上不提供任何弱的上拉或下拉。当SPI_DO处于非活动状态时,它以高阻抗状态浮动。如果SPI_DO上始终需要有效的逻辑状态,则应在PCB上添加一个外部弱上拉/下拉。

SPI数据传输协议

AD9361 SPI是一款灵活的同步串行通信总线,可与许多工业标准微控制器和微处理器无缝接口。串行 I/O 与大多数同步传输格式兼容,包括摩托罗拉 SPI 和英特尔® SSR 协议。AD9361的控制场宽度限制为16位,允许多字节IO操作。AD9361不能用于控制总线上的其他器件,它只能作为从器件工作。

通讯周期分为两个阶段。阶段1是控制周期,即将控制字写入AD9361。控制字为AD9361串行端口控制器提供有关数据场传输周期的信息,即通信周期的第2阶段。阶段 1 控制字段定义即将进行的数据传输是读取还是写入。它还定义了正在访问的寄存器地址。

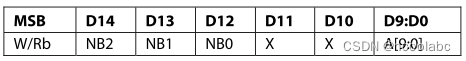

第 1 阶段指令格式

16 位控制字段包含以下信息:

W/Rb 指令字的第 15 位确定在指令字节写入之后是进行读取还是写入数据传输。逻辑高电平表示写入操作;逻辑零表示读取操作。

NB2、NB1、NB0 — 指令字的位 [14:12] 指定在 IO 操作的第 2 阶段期间传输的字节数。下表详细说明了每个 NB[2:0] 组合在第 2 阶段传输的字节数。

[D11:D10] - 指令字的位 [11:10] 未使用。

[D9:D0] — Bits[9:0] 指定 IO 操作第 2 阶段期间数据传输的起始字节地址。

所有字节地址(包括起始地址和内部生成的地址)都假定为有效。也就是说,如果访问了无效地址(未定义的寄存器),IO 操作将继续进行,就好像地址空间有效一样。对于写入操作,写入的位被丢弃,读取操作会导致输出端的逻辑为零。

单字节数据传输

当 NB2、NB1 和 NB0 均为零时,选择单字节数据传输。在这种情况下,地址位后面的8位包含向AD9361寄存器写入或读取的数据。一旦传输了最后一个位,数据信号将返回到其空闲状态,SPI_ENB信号变为高电平以结束通信会话。

多字节数据传输

当 NB2、NB1 和 NB0 均为非零时,选择多字节数据传输。在此模式下传输的数据的格式和顺序取决于器件是配置为 LSB 优先还是 MSB 优先数据传输。

对于LSB模式下的多字节数据传输,用户写入一个指令字节,其中包含最低有效字节的寄存器地址。SPI内部字节地址生成器针对多字节通信周期中所需的每个字节递增。数据按从最低到最有效的顺序写入,因为字节地址也是按从最低到最有效的顺序生成的。

对于 MSB 模式下的多字节数据传输,用户编写一个指令字,其中包含最高有效字节的寄存器地址。串行端口内部字节地址生成器针对多字节通信周期所需的每个字节递减。数据按最高到最低有效顺序写入,因为字节地址是按最高到最低有效顺序生成的。

示例:MSB-First 多字节传输

要完成 4 字节写入,从 MSB 第一格式的寄存器0x02A开始,应用指令字 1_011_000000101010(二进制)。该指令指示AD9361 SPI控制器执行4字节的写传输,起始字节地址为0x02A。写入第一个数据字节后,内部字节地址生成逻辑递减为0x029,即第二个字节的目的。写入第二个字节后,内部字节地址生成逻辑递减为 0x028,即第三个字节的目的地。

写入第三个字节后,内部字节地址生成逻辑递减为 0x027,这是最后一个字节的目标。写入第四个字节后,IO 通信周期完成,SPI_CLK上接下来的 16 个下降时钟周期用于为下一个指令字提供时钟。如果不需要进一步的通信,则数据信号返回到其空闲状态,SPI_CLK变为低电平,SPI_ENB信号变为高电平以结束通信会话。

示例:LSB 优先多字节传输

要完成 4 字节写入,从寄存器0x02A开始,采用 LSB first 格式,应用 010101000000_110_1(二进制)指令字。该指令指示AD9361 SPI控制器执行4字节的写传输,起始字节地址为0x02A。写入第一个数据字节后,内部字节地址生成逻辑递增到 0x02B,这是第二个字节的目标。写入第二个字节后,内部字节地址生成逻辑递增为 0x02C,这是第三个字节的目标。

写入第三个字节后,内部字节地址生成逻辑递增为 0x02D,这是最后一个字节的目标。写入第四个字节后,IO 通信周期完成,SPI_CLK上接下来的 16 个下降时钟周期用于为下一个指令字提供时钟。如果不需要进一步的通信,则数据信号返回到其空闲状态,SPI_CLK变为低电平,SPI_ENB信号变为高电平以结束通信会话。

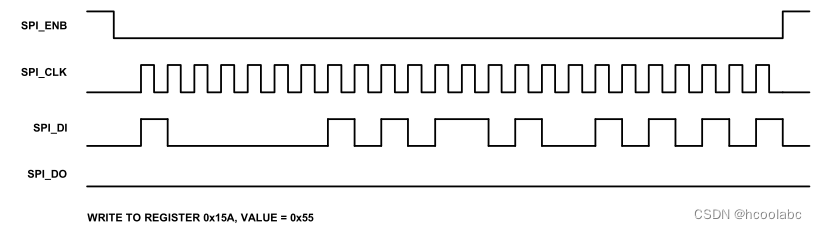

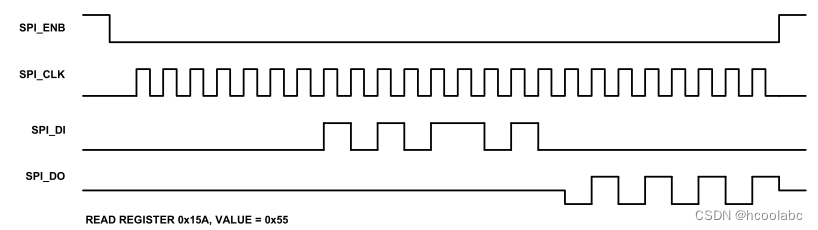

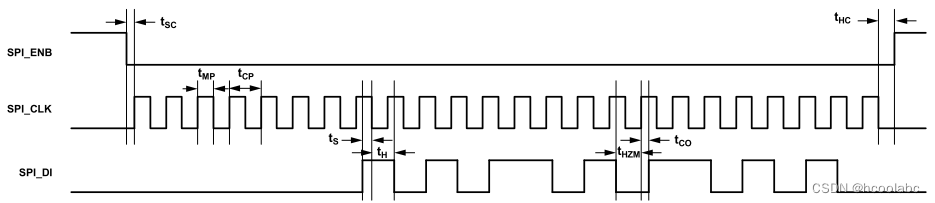

时序图

下图分别详细说明了单寄存器写操作和单寄存器读操作的SPI总线波形。在第一张图中,值 0x55 写入寄存器0x15A。在第二个值中,读取寄存器0x15A,并0x55设备返回的值。如果使用 3 线总线执行相同的操作,则A图中的 SPI_DO 线将被消除,B图 中的 SPI_DI 和 SPI_DO 线将合并在 SPI_DI 线上。

A图 写时序

B图 读时序

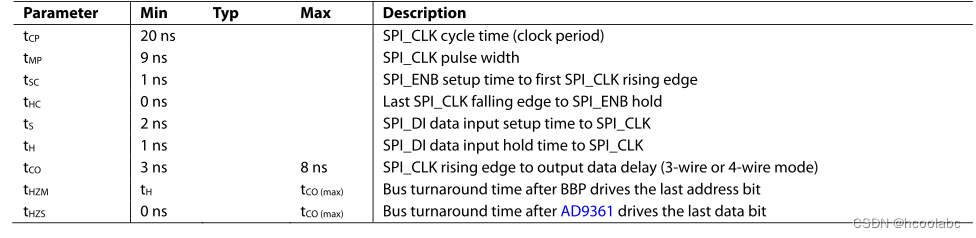

下表列出了SPI总线的时序规格。这些参数之间的关系如C图 所示。这张图

显示了标记了这些参数的 3 线 SPI 总线时序图。请注意,这是一个单次读取操作,因此总线就绪

从AD9361驱动数据后的参数未显示在图中。

C图 3线SPISPI读时序

C图 3线SPISPI读时序

参考源文件 :《UG-570 AD9361 Reference Manual 》

参考源文件 :《UG-671 AD9361 Register Map Reference Manual》

542

542

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?