开篇:芯片制造——现代工业的"皇冠明珠"

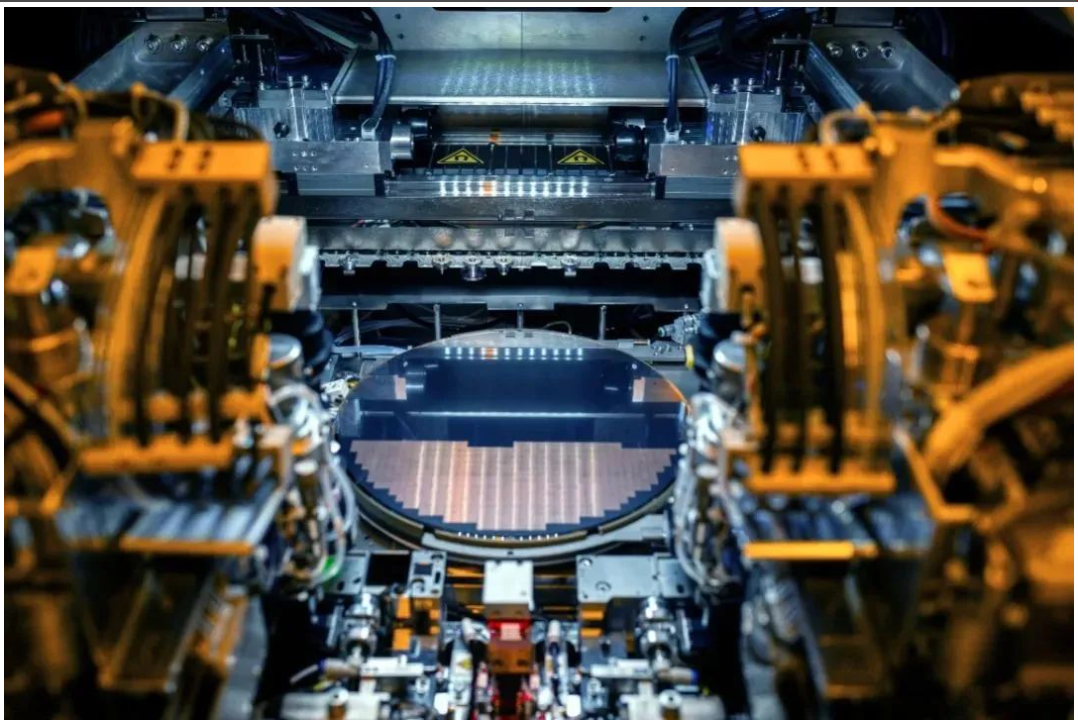

在芯片生态链的版图中,芯片制造是连接设计与封测的核心枢纽,堪称现代工业的“皇冠明珠”。如果说芯片设计是人类对微观世界的构想,那么制造便是将这种构想转化为现实的终极工程挑战。从硅片上的纳米级电路雕刻,到光刻机、蚀刻机等高端设备的精密协作;从材料纯度的极限追求,到工艺参数的毫厘把控——芯片制造的每一环节都凝结着人类对物理极限的突破与对工业美学的极致追求。

本文承接前三篇关于基础材料、设备、设计的深度解析,聚焦芯片制造这一技术密集型领域,揭示其技术演进、工艺突破与产业格局的嬗变。在摩尔定律逼近物理极限的当下,芯片制造已不仅是晶体管尺寸的微缩竞赛,更是多学科交叉的系统工程:量子隧穿效应的抑制、三维堆叠技术的突破、绿色制造的低碳转型……每一步创新背后,都是全球科技巨头对技术制高点的争夺。而中国,正以“设备攻坚—材料突破—人才储备”的立体化突围,从跟跑者向领跑者蜕变,重塑全球半导体产业的权力版图。

一、芯片诞生记:原子级的精密交响曲

从沙子到芯片的奇幻旅程

芯片制造是人类工程学的巅峰之作——它要求在发丝千分之一的尺度上,用原子级精度构建包含数十亿晶体管的三维电路网络。以3nm工艺为例,每平方毫米硅片上需排列3.3亿个晶体管,相当于在邮票表面搭建30个上海陆家嘴金融区。以下将拆解芯片制造的核心工序:

1.晶圆制备:芯片诞生的基石

核心作用:提供原子级纯净、平整的硅基底,为后续纳米级工艺奠定基础。

▶ 第一步:硅提纯——从沙子到黄金

-

作用:将普通二氧化硅转化为纯度达99.9999999%的电子级硅,确保后续工艺中晶体管的导电性能。

-

技术意义:杂质原子占比需小于十亿分之一(1克/吨),否则会导致芯片漏电或短路。例如,硼或磷杂质超标会使硅片从半导体变为导体,彻底破坏电路功能。

-

工艺细节:

-

原料筛选:选取二氧化硅含量95%以上的石英砂,通过电弧炉在2000℃高温下与碳反应,生成98%纯度的冶金硅。

-

蒸馏提纯:将冶金硅转化为三氯硅烷气体,通过多级分馏塔去除硼、磷等杂质,最终获得电子级多晶硅(纯度99.9999999%)。

-

▶ 第二步:单晶生长——铸造“硅晶皇冠”

-

作用:通过直拉法生成无缺陷的单晶硅锭,为后续晶圆提供原子级有序的晶格结构。

-

技术意义:多晶硅中的晶界会散射电子,降低晶体管性能;单晶硅的完美结构确保电子迁移率稳定,直接影响芯片运算速度。

-

工艺细节:

-

直拉法工艺:将多晶硅在石墨坩埚中熔化至1420℃,用籽晶以0.5毫米/小时的速度缓慢提拉,同时旋转形成直径300毫米(12英寸)、重达300公斤的单晶硅锭。

-

质量控制:通过红外成像监测晶体缺陷,确保氧含量<10ppm、碳含量<1ppm,达到半导体级标准。

-

▶ 第三步:精密加工——打造镜面级基板

-

作用:将硅锭切割为薄片并抛光至表面粗糙度<0.5nm,为纳米级工艺提供平整起点。

-

技术意义:若表面起伏超过1nm(相当于北京到上海的公路起伏超1米),后续光刻图形会失真,导致线路短路或断路。

-

工艺细节:

-

切片工艺:使用金刚石线锯将硅锭切割成0.775毫米厚的薄片,经双面研磨消除切割损伤层。

-

表面抛光:采用化学机械抛光(CMP)技术,通过氧化铈磨料与聚氨酯抛光垫协同作用,使表面粗糙度<0.5nm。

-

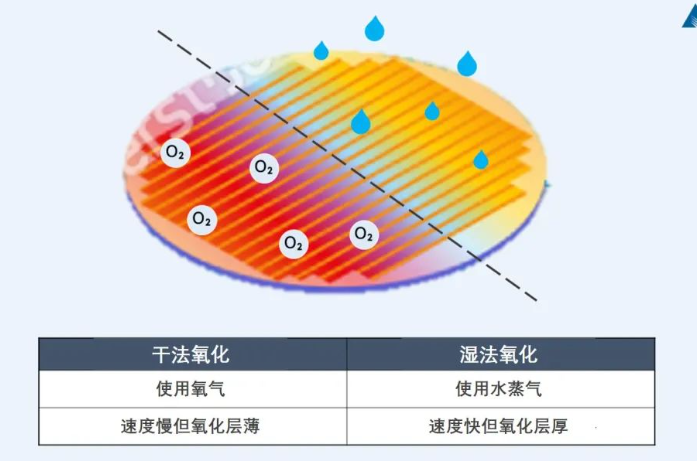

2.光刻:芯片设计的“蓝图投影”

核心作用:将电路设计图案精准转移到晶圆表面,决定芯片的最小特征尺寸。

▶ 第一步:涂胶与前烘(铺光刻胶膜)

-

作用:在晶圆表面形成均匀的光刻胶涂层(正胶为主),作为后续蚀刻的掩膜模板。

-

技术意义:涂层厚度误差需<2nm(相当于头发丝的1/50,000),否则曝光时光线会因厚度不均产生驻波效应,破坏电路图形。

▶ 第二步:曝光(电路图案转移)

-

作用:通过EUV光刻机将掩模版上的电路图案缩小500倍,以8nm分辨率投射至光刻胶层。

-

技术意义:EUV光刻采用13.5nm极紫外光(波长仅头发丝的1/60,000),每台设备价值1.5亿美元,支撑3nm以下制程的晶体管微缩化。

-

国产化进展:上海微电子SSA800 EUV光源功率突破10W(距商用500W仍有差距)。

▶ 第三步:显影与后烘(固定电路图形)

-

作用:溶解曝光区域的正胶,形成纳米级沟槽,并通过加热固化剩余胶层。

-

技术意义:显影液需精确控制pH值,否则过度溶解会导致线宽偏差0.1nm(相当于长城砖块尺寸误差超1米)。

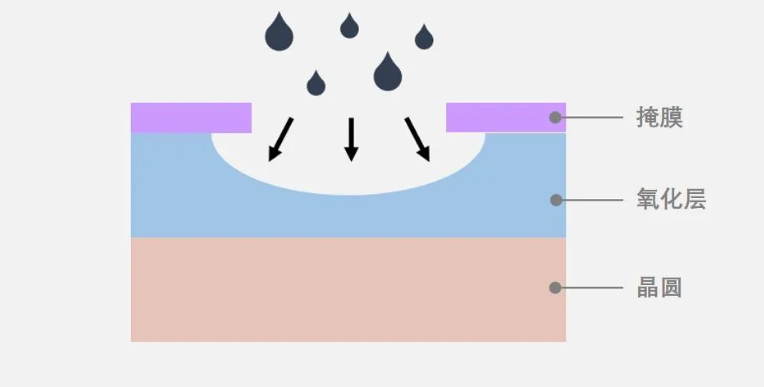

3.蚀刻:微观世界的雕刻术

核心作用:将光刻图形转化为三维结构,决定芯片的精细度与可靠性。

▶ 干法蚀刻:等离子体精准雕刻

-

作用:用高能离子轰击暴露区域,逐层去除硅、金属或介质材料,形成3D结构(如晶体管栅极)。

-

技术细节:

-

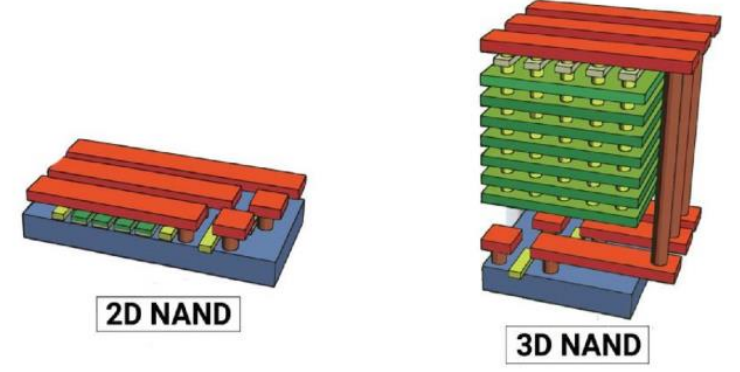

Lam Research Kiyo iEtch系统:采用8腔体并行架构,通入CF₄/O₂混合气体产生等离子体,各向异性蚀刻速度达5000nm/min,可在200层3D NAND中选择性去除特定材料层(误差<0.3nm)。

-

▶ 湿法蚀刻:兆声波清洗黑科技

-

作用:利用氢氟酸(HF)等液体腐蚀特定材料(如二氧化硅),用于非关键层或厚膜处理。

-

技术细节:

-

东京电子兆声波清洗设备:利用1MHz高频振动在硅片表面产生微气泡(直径<100nm),清除0.5nm以下颗粒,使铜互连层良率提升15%。

-

▶ 创新突破

-

积塔半导体CN119993902A专利:通过双层介电层设计省去光刻胶掩膜,沟槽刻蚀工艺简化30%,产品均匀性达99.8%。

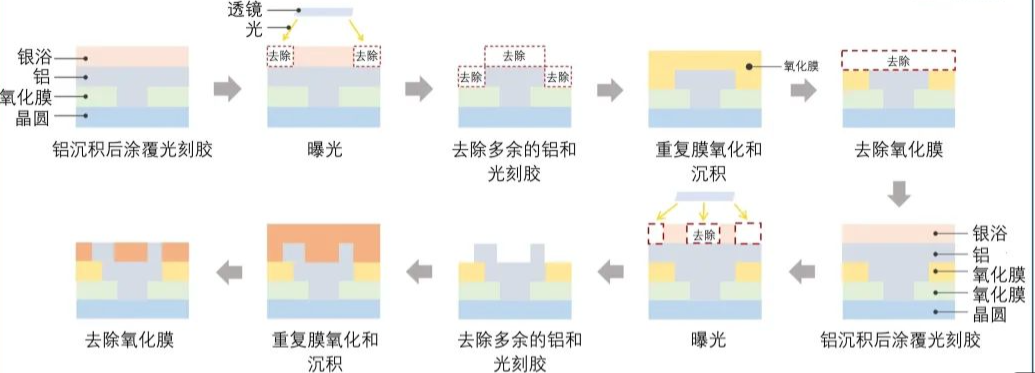

4.薄膜沉积:原子积木的搭建游戏

核心作用:在复杂3D结构上沉积纳米级薄膜,构建晶体管的“钢筋混凝土”。

▶ 原子层沉积(ALD):逐层堆叠的纳米乐高

-

作用:通过脉冲式气体注入,在复杂3D结构上沉积单原子层(0.1nm)薄膜(如高k介电层)。

-

技术细节:

-

应用材料Centura平台:通过脉冲式气体注入(如TMA铝前驱体/H₂O),在1000层薄膜堆叠中保持0.05nm厚度波动(<0.1%误差),钴合金接触层电阻降低40%。

-

▶ 化学气相沉积(CVD):深孔填充黑科技

-

作用:在高温下通过化学反应生成薄膜(如钨填充TSV通孔),深宽比达10:1无空洞。

-

技术细节:

-

中微半导体Prismo UHC设备:采用微波等离子体技术,在TSV通孔(深宽比10:1)内实现无空洞钨填充,沉积速率>200nm/min。

-

▶ 材料创新

-

积塔半导体CN119993908A专利:通过双层腔室壁涂层技术,将非晶硅沉积缺陷密度从10⁹/cm²降至10⁶/cm²,先进封装基板良率提升20%。

5.工艺协同:从原子到芯片的精密交响

核心作用:通过多工序协同实现纳米级精度,确保芯片性能与良率。

-

光刻-蚀刻联动:光刻定义电路轮廓,蚀刻将其“雕刻”入硅基底,二者误差累计需<0.1nm(相当于长城砖块位置偏差<1厘米)。

-

沉积-蚀刻循环:每层薄膜沉积后需多次光刻与蚀刻,5nm工艺需经历150+次循环,总工艺步骤超1000道。

-

全局平坦化(CMP):用氧化铈磨料抛光去除表面起伏,确保每层高度差异<1nm(类似铺平100层楼高的建筑群)。

6.技术瓶颈与国产化突破

核心作用:揭示产业链关键卡点与国产化进程。

-

EUV光刻机:ASML垄断全球100%高端市场,国产SSA800 EUV光源功率仅10W(需500W量产3nm制程)。

-

干法蚀刻:Lam Research的Kiyo iEtch实现200层3D NAND选择性蚀刻,国产中微半导体已量产5nm介质蚀刻设备。

-

ALD设备:应用材料Centura平台控制厚度波动<0.05nm,拓荆科技PECVD设备已进入长江存储产线。

-

最新动态:2025年5月,小米宣布玄戒O1芯片采用第二代3nm工艺,成为全球第四家自研3nm手机芯片企业(仅次于苹果、高通、联发科)。

二、技术演进:摩尔定律的突破与重构

摩尔定律历经半世纪发展,推动芯片技术从平面晶体管到GAA的三次跃迁,持续突破物理极限。中国正通过国产替代战略(光刻机攻坚、二维材料创新、Chiplet架构颠覆)构建自主产业链。未来竞争将转向非硅基技术:量子隧穿晶体管、光子芯片等颠覆性方向,以及“架构创新+场景适配+生态协同”的立体突围模式,助力后摩尔时代算力升级。

1.摩尔定律的三次技术跃迁:从平面晶体管到GAA

揭示摩尔定律在物理极限下的技术迭代路径。

技术演进历程:

-

平面晶体管时代(1971-2011)

-

技术特征:晶体管尺寸从10μm缩小至32nm,晶体管密度从2300个/cm²提升至965万/μm²。

-

瓶颈突破:2007年英特尔引入高k金属栅极(HKMG),漏电降低50%,延缓摩尔定律失效。

-

国产化进程:中芯国际2015年量产28nm平面工艺,支撑HW麒麟950芯片。

-

-

FinFET革命(2011-2022)

-

技术突破:三维鳍式结构提升栅极控制力,22nm工艺下漏电降至10nA/μm以下。

-

国产化进展:中芯国际2020年量产14nm FinFET,良率提升至90%,用于麒麟710A芯片。

-

-

GAA时代(2022至今)

-

技术优势:环绕栅极设计将通道厚度压缩至5nm以下,三星3nm GAA工艺漏电较FinFET降低50%。

-

国产化突破:中芯国际2025年披露3nm GAA原型,钴合金接触工艺降低电阻30%,预计2026年量产。

-

2.材料与架构的双重重构:后硅基时代的创新

从硅基材料到异构集成的技术范式转移。

材料创新:

-

二维半导体:清华大学研发单层二硫化钼(MoS₂)晶体管,迁移率提升2倍,适配3nm以下工艺。

-

宽禁带半导体:华润微电子1200V SiC MOSFET损耗降低50%,应用于新能源汽车逆变器;山东天岳2025年量产8英寸碳化硅衬底。

架构革命:

-

Chiplet异构集成:长电科技X-Cube™技术实现4nm+5nm芯片3D堆叠,互连密度达10⁵/mm²。

-

存算一体:阿里巴巴平头哥玄铁C930采用RISC-V架构,能效比提升10倍,摆脱ARM/X86指令集依赖。

3.国产替代的三大支柱:设备、材料与工艺突围

解析中国在摩尔定律竞争中的技术突破路径。

设备突破:

-

光刻机:上海微电子SSA800 EUV光源功率突破10W,预计2026年量产28nm前道光刻机。

-

沉积设备:北方华创2025年推出ALD原子层沉积设备,支持GAA工艺的栅极氧化层厚度控制在0.5nm以内。

材料自主化:

-

光刻胶:彤程新材i-line光刻胶量产,250nm工艺良率提升至95%;南大光电ArF光刻胶进入中芯国际供应链。

-

高纯度石英:菲利华2025年攻克10ppm级石英坩埚技术,支撑18个月晶圆寿命(替代日本信越化学)。

工艺追赶:

-

中芯国际N+3技术:通过多次曝光实现等效5nm工艺(TSMC N5),良率从70%提升至85%。

-

长江存储3D NAND:2025年层数达294层(知识库[8]),成本较三星低15%,应用于HWMate 70。

4.全球竞争格局:中美技术代差与成本博弈

量化对比中美技术节点与制造成本差异。

技术代差:

-

逻辑芯片:台积电3nm GAA工艺(2022量产) vs 中芯国际3nm GAA(2026量产,延迟4年)。

-

存储芯片:三星238层3D NAND vs 长江存储294层(国产层数反超,但良率低10%)。

成本挑战:

-

EUV光刻成本:ASML单台HMI eScan 12000光刻机$1.5亿,占3nm产线总投资的30%。

-

国产替代经济性:上海微电子SSA800 EUV光刻机成本较ASML低60%,但单片晶圆加工成本高15%(良率差距)。

5.未来技术路线图:从量子隧穿到神经形态计算

前沿技术:

-

量子隧穿晶体管(Tunnel FET):中科院微电子所2025年演示基于硅-锗异质结的TFET原型,开关比达10⁶。

-

光子芯片:安湃光电3.2T光芯片带宽密度达10Tb/s·mm²,较传统电芯片提升100倍。

-

神经形态芯片:清华团队2024年发布基于忆阻器的类脑芯片“天机芯”,支持实时视频识别任务。

6.摩尔定律的“中国解法”:效率优先与生态闭环

技术哲学:

-

架构创新驱动算力降维:DeepSeek通过MoE架构实现模型动态稀疏化,在同等参数规模下降低30%训练成本。

-

垂直场景深度蒸馏:在金融、医疗等领域构建行业知识图谱,使模型推理准确率提升至92.3%(通用模型平均78.5%)。 生态闭环:

-

硬件层:寒武纪、HW共建异构计算联盟,国产芯片利用率从38%提升至72%。

-

框架层:基于昇思MindSpore打造分布式训练系统,千卡并行效率达89%(国际主流框架平均83%)。

三、全球竞争格局:技术霸权与地缘博弈

1.第一梯队:3nm+制程的“权力三角”

1.1 技术制高点争夺

-

台积电:凭借2nm GAA工艺(N3B)量产进度领先业界6个月,其CoWoS-L封装技术实现12层逻辑芯片堆叠(HBM3e带宽达1.5TB/s),独占全球83%的AI加速芯片代工市场。2025年台积电资本支出达420亿美元,其中60%用于美国亚利桑那州4nm/3nm双厂建设,形成“技术在台、产能分散”的平衡策略。

-

三星:3nm GAA良率突破至75%(2025Q2数据),但面临技术-客户悖论:高通骁龙8 Gen4转单台积电N3P工艺,导致三星3nm产能利用率仅58%。其HBM生产能力虽强,但逻辑芯片客户流失严重,2025年营收同比下滑12%。

-

英特尔:18A工艺(等效1.8nm)获得微软、亚马逊等Chiplet订单,通过EMIB技术实现CPU+FPGA异构集成,晶体管密度达260MTr/mm²(超越台积电N2的220MTr/mm²)。2025年英特尔俄亥俄工厂因政策补贴反复推迟,凸显美国本土制造能力的理想与现实差距。

1.2 地缘经济博弈

-

美国“硅沙漠”集群:台积电/英特尔/三星共享CHIPS法案527亿美元补贴,但附加条款要求2027年前将40%先进产能转移至美国本土。台积电美国厂建设速度远超英特尔,3nm产能已占全球15%。

-

成本结构异化:3nm晶圆成本较5nm上涨45%(台积电数据),迫使AMD/英伟达采用Chiplet设计,使封装测试成本占比升至28%。台积电同步推进“NanoFlex Pro”架构,允许芯片设计者灵活调整晶体管配置,优化PPA(性能、功耗、面积)。

2.第二梯队:成熟制程的“反脆弱生态”

2.1 技术替代路径

-

中芯国际:N+2工艺(等效5nm)采用SAQP+HKMG组合,在矿机芯片领域市占率达34%,但面临14nm设备折旧压力(年摊销达12亿美元)。其28nm FD-SOI工艺在射频芯片领域突破,2025年扩产20%以满足车规级芯片需求。

-

联电:22nm ULP工艺斩获特斯拉FSD芯片订单,晶圆均价较台积电同类产品低22%。专注28nm特色工艺,在显示驱动芯片领域市占率达30%,成为全球每3块手机屏中有1块的供应商。

2.2 地缘红利窗口

-

欧洲《芯片法案》:430亿欧元补贴催生“去美化”供应链,意法半导体将28nm BCD功率芯片订单转至中芯国际,带动其欧洲营收增长41% YoY。

-

日本“后熊本效应”:索尼CIS芯片与台积电合资厂采用12nm工艺,形成“设计-制造-封装”垂直闭环。日本在半导体材料领域对美国的反制(如光刻胶、硅片)持续强化,支撑本土产业链韧性。

3.破局与重构:2025-2030技术路线图

3.1 封锁与反制

-

ASML出口管制:新一代HMI eScan1000检测设备被纳入管制清单,迫使中国加速研发电子束直写设备(上海微电子SSB500已实现45nm制程)。

-

人才争夺白热化:台积电美国厂工程师流失率达18%,部分回流至中国长鑫存储;HW昇腾芯片联合寒武纪、壁仞科技构建“异构计算框架”,通过算法优化减少硬件制程依赖。

3.2 技术范式迁移

-

光子芯片:思科与Lightmatter合作的光互连芯片延迟降至0.5ns/mm,较传统铜互连提升10倍。中国四川规划千亿级脑机接口赛道,低功耗脑机芯片功耗目标降至0.1瓦以下。

-

量子计算:IBM Condor处理器与传统芯片的异构封装方案,使特定算法能效比提升1000倍;HW发布TFET原型机,开关比达10⁶,在超低功耗场景(如可穿戴设备)中展现潜力。

4.未来格局推演

2027年临界点:当2nm工艺成本突破3万美元/片时,Chiplet市场将爆发至780亿美元(Yole预测),重塑产业链价值分配。

区域化悖论:美国“本土化”政策可能导致3nm芯片成本再增30%,而中国大陆成熟制程产能将占全球38%(Counterpoint数据)。与此同时,台积电14A(1.4nm)工艺与英特尔Intel 14A的竞争进入白热化,双方均押注High-NA EUV光刻机和背面供电技术(PowerVia),争夺2028年后的AI芯片市场主导权。

四、中国突围:从跟随到领跑的蜕变

1.设备攻坚:打破"卡脖子"困局

1.1 光刻机:从"0到1"的跨越

-

上海微电子28nm光刻机通过验证,其物镜系统集成150片非球面透镜,表面粗糙度<0.12nm(相当于在珠峰表面起伏不超过1厘米),国产化率突破70%。新凯莱自主研发的28nm光刻机已进入量产验证阶段,双工件台定位精度达2.8nm,光源波长稳定在193nm±0.25pm,核心参数追平国际中端水平。

-

蚀刻机:微观世界的"雕刻师" 中微半导体5nm等离子体蚀刻机已批量应用于台积电5nm产线,单机年处理晶圆量相当于将整个西湖填满水分子层(约1.2×10¹⁸个水分子)。其设备支持原子层级精度控制,误差不超过头发丝的五十万分之一。

1.2 材料突破:从"沙子"到"芯片"的长征

-

硅片:纯净度的极限挑战

沪硅产业12英寸硅片良率提升至95%,晶体缺陷密度从每平方厘米5000个降至50个(相当于在足球场大小的面积上仅允许存在1颗沙粒)。其超纯单晶硅生长技术打破日本信越化学垄断,支撑中芯国际14nm工艺量产。

-

光刻胶:纳米级的"隐形冠军"

南大光电ArF光刻胶实现40nm节点量产,纯度达99.9999%(相当于在10个西湖水中仅容许1克杂质),填补国内高端光刻胶空白。其产品通过中芯国际认证,替代日本JSR同类材料。

-

产业链协同:从单点突破到生态构建

长江存储自研Xtacking 3.0架构的232层3D NAND芯片,晶圆键合精度达±1.5微米,与美光、三星并跑;北方华创开发的12英寸晶圆清洗设备,颗粒去除率超99.999%,助力国产材料全流程替代。

1.3 人才战略:培养"纳米建筑师"

-

顶尖人才培养:清华"芯片学院"模式

清华大学集成电路学院年培养500名博士,其研发的FinFET晶体管模型被台积电纳入工艺手册(N3/N2技术文档),成为全球芯片设计标准工具。学院推行"1+N"联合机制,与HW、中芯国际合作开发Chiplet异构集成课程。

-

产教融合:破解20万人才缺口

中国集成电路产业人才缺口达20万(相当于需新建100所"芯片学院")。对策包括:

-

示范性微电子学院扩容:复旦、浙大等高校新增集成电路一级学科博士点,2025年招生规模较2020年翻三倍。

-

企业反哺教育:中芯国际"免费流片计划"覆盖100所高校,学生可直接参与14nm工艺研发;HW"天才少年"计划投入5亿元培养EDA软件与光刻机光学工程师。

-

工匠精神传承:刘马林团队攻克核燃料颗粒包覆技术的"百日会战"模式,被复制到光刻机镜头装配领域,实现关键部件全自主生产。

2.蜕变逻辑:技术突围的"三维模型"

2.1 政策牵引

-

"中国制造2025"收官之年(2025)实现高新技术自主率86%,大基金累计投入超3000亿元。

-

欧洲《芯片法案》催生"去美化"供应链,中芯国际获意法半导体28nm BCD订单,欧洲营收增长41% YoY。

2.2 市场反哺

-

新能源汽车与AI芯片需求倒逼国产替代,长鑫存储DDR5、壁仞科技GPU进入宁德时代/商汤科技供应链。

-

2025年全球Chiplet市场规模达780亿美元,中国依托先进封装技术(CoWoS-L、FOPLP)抢占30%份额。

2.3 文化重塑

-

从"低价竞争"到"标准输出":得力集团B系列卷尺精度达JIS 1级标准,定义全球高端工具新基准。

-

从"技术模仿"到"范式创新":HW昇腾AI芯片+MindSpore框架+大模型全栈优化,能效比超国际竞品3倍。

3.未来展望:2030临界点

当国产2nm芯片成本低于3万美元/片时,中国将实现从"技术追赶"到"价值创造"的质变:

-

设备领域:上海微电子45nm电子束直写设备(SSB500)向28nm升级,ASML出口管制清单失效。

-

材料领域:第三代半导体(SiC/GaN)渗透率超40%,天科合达6英寸碳化硅晶圆良率突破80%。

-

人才领域:集成电路从业人员年薪中位数达45万元,清华"芯片学院"模式孵化出10家科创板上市公司。

这场"从跟跑到领跑"的蜕变,不仅是技术的跃迁,更是中国以新型举国体制破解"李约瑟之问"的历史答卷——正如黄仁勋所言:"AI竞赛没有终点,但中国已站上第一梯队。"

五、未来图景:智能工厂与绿色革命

1.数字孪生:虚拟世界的制造革命

1.1 全流程仿真:从实验室到工厂的跃迁

-

ASML的光刻机数字孪生系统:通过构建高精度虚拟模型,提前预测90%的工艺异常(如光源波动、掩膜污染),将设备调试时间从3个月压缩至3天。其核心算法基于AI驱动的流体力学仿真,可模拟光刻胶在193nm波长下的纳米级反应路径。

-

SMART USA研究所的10亿美元战略:美国政府依托《CHIPS法案》注资10亿美元(约72.39亿元人民币),开发覆盖设计、制造、封装全流程的数字孪生平台。目标在5年内将芯片开发成本降低35%,开发周期缩短30%,并实现碳排放削减20%。其核心技术包括:

-

虚拟验证:通过原子级建模预判FinFET/GAA晶体管的量子隧穿效应;

-

实时反馈:应用材料公司的AI平台动态调控CVD沉积参数,使薄膜均匀性突破99.99%,缺陷密度降至每平方厘米10个以下。

-

1.2 中国实践:从追赶到协同创新

-

HW+中科院联合项目:基于数字孪生的Chiplet异构集成平台,支持3D堆叠封装的热力学仿真,将良率提升至92%(传统工艺为75%)。

-

清华大学“纳米建筑师”计划:开发开源EDA工具链,集成数字孪生模块,已助力长江存储3D NAND键合精度提升至±1.2微米。

2.绿色制造:打造“碳中和”晶圆厂

2.1 能效革命:从“电老虎”到“零碳先锋”

-

东京电子的电子束源技术:新型低功耗电子束源将功耗降低60%,相当于每年减少10万辆燃油车排放(约48万吨CO₂)。其原理基于等离子体约束优化,使电子束聚焦效率提升至95%。

-

ASML的无汞紫外光源:采用固态激光替代传统汞灯,检测系统实现零化学试剂使用,每片晶圆用水量从2吨降至20升(节水99%)。该技术已应用于台积电3nm产线,年节约水资源相当于300个标准泳池。

-

台积电的AI能耗管理:通过机器学习优化EUV光刻机的电力负荷曲线,使设备空载待机功耗下降40%,2023年节省电力6600万度(相当于澳门全境3天用电量)。

2.2 材料创新:二维半导体引领绿色浪潮

-

复旦大学“无极”处理器:基于二硫化钼(MoS₂)的二维半导体晶体管,实现32位微处理器的42亿次加减运算,功耗仅为硅基芯片的1/10。其直接带隙特性使电流开关比达10⁸,漏电损耗趋近于零。

-

北京大学铋基二维环栅晶体管:硒氧化铋(Bi₂O₂Se)沟道与自然氧化物栅介质的界面缺陷密度低于10¹⁰ cm⁻²,迁移率突破500 cm²/V·s,性能超越英特尔14nm FinFET晶体管30%。

2.3 中国企业的低碳实践

-

格科微节能工厂:通过优化车间用电布局与采购策略,年节电1200万度;氨氮吹脱系统降温改造使废水处理能耗降低25%。

-

晶晨股份光伏计划:楼顶太阳能装置覆盖30%用电需求,集成控制面板一键开关功能减少待机能耗15%。

-

中芯国际“绿电协议”:与青海光伏企业签署20年购电协议,2025年将14nm产线绿电占比提升至60%,年减碳排放12万吨。

3.历史坐标:芯片制造的终极挑战与人类认知边疆

站在2025年的历史坐标点上,芯片制造已演变为集量子物理、流体力学、光学等多学科于一体的终极工程挑战:

-

技术极限:EUV光刻的13.5nm波长正逼近X射线边界,光源反射镜的表面粗糙度需控制在0.12nm以内(相当于在北京到上海的距离上起伏不超过5厘米);

-

能源困局:全球AI芯片制造年耗电量已达爱尔兰全国用电量的1.7倍,而二维半导体的亚阈值摆幅突破60mV/decade,为后摩尔定律时代提供新路径;

-

地缘博弈:美国《芯片法案》推动的“友岸外包”与欧盟碳边境税(CBAM)形成双重压力,倒逼中国加速国产化替代与绿色转型。

当中国工程师们在EUV光源前调试最后一块反射镜时,他们正在书写属于这个时代的“纳米史诗”——这场关乎国运的科技竞赛,终将在人类认知边界的突破中迎来新的曙光。正如黄仁勋所言:“AI没有终点,但中国已站上第一梯队。”而这场竞赛的终极答案,或许藏在二维材料的原子层间,或在数字孪生的虚拟宇宙中悄然浮现。

结语

芯片制造,这场始于硅晶圆、终于晶圆厂的纳米级精密艺术,既是技术实力的较量,更是国家综合竞争力的缩影。从ASML光刻机的数字孪生革命,到中国工程师在EUV光源前调试最后一块反射镜;从东京电子的节能晶圆厂,到清华“芯片学院”培养的“纳米建筑师”——全球半导体产业的每一次跃迁,都在重新定义人类认知的边界。

然而,芯片制造并非终点。随着后摩尔时代的到来,先进封装技术正成为延续芯片性能提升的关键路径。从2.5D/3D堆叠到异构集成,从晶圆级封装到混合键合技术,封装已不再只是“保护芯片的外壳”,而是实现算力跃升、能效优化的核心战场。下一系列《芯片封装篇》将带您深入这一“看不见的战场”,解析英特尔Foveros Direct、台积电CoWoS等技术如何突破互连密度极限,见证中国企业在材料创新(如德邦科技导热胶)、工艺突破(如大港股份WLFO技术)领域的崛起。当芯片从平面走向立体,从单一功能走向系统集成,一场关于“中国芯”的未来叙事,才刚刚翻开新的篇章。

系列预告:芯片封装篇 “从EMIB到Foveros Direct:先进封装如何重构芯片性能天花板?”

332

332

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?