前言

在写仿真模型的过程中,为了方便,我们通常在tb里边,通过层次引用的方式,将模块的接口assign出来给interface,再将interface用config_db送给环境去处理,RTL前仿这样做没问题,但是后仿的时候存在一定的风险。

一、记录一个仿真模型在前仿和后仿中遇到的问题

风险来自两个方面:

一方面是网表里边的信号可能会被优化。 综合的时候,有可能会将模块的层次打平,这样inbound内部的信号有可能就会被优化,导致tb前仿环境里边的信号在后仿的网表中找不到。

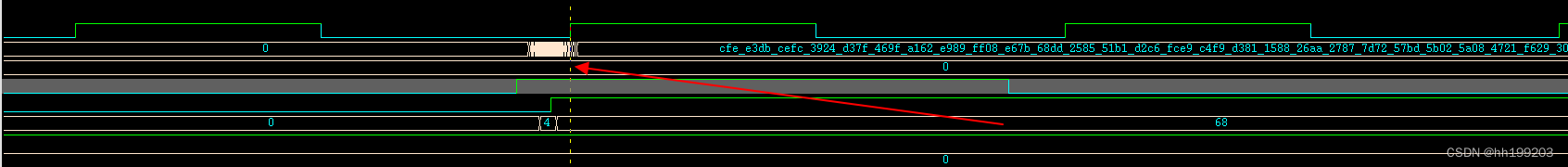

另一方面是网表接口上的时钟采到的可能不是真实的数据。 就算综合的时候保留前仿的层次结构和接口信号,但是由于网表中每一个器件都存在延时,导致接口时钟,跟真正DFF踩数据信号的时钟,不是同一个,这就造成接口时钟有可能采样到不稳定的接口数据,从而导致前仿没问题,而后仿则仿真模型报错。

9020

9020

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?