目录

1.算法仿真效果

本作品是之前作品的改进和扩展:

基于FPGA的BPSK+costas环实现,包含testbench,分析不同信噪比对costas环性能影响_解调bpsk的fpga实现costas环-CSDN博客

在上述作品的基础上做了如下的改进:

第一、增加了误码统计模块,可以分析不同SNR下,costas环的误码率性能指标

第二、调整了costas环的环路滤波器参数,使得低SNR信噪比下,系统依旧可以锁定频偏

仿真操作步骤可参考程序配套的操作视频。

vivado2019.2仿真结果如下(完整代码运行后无水印):

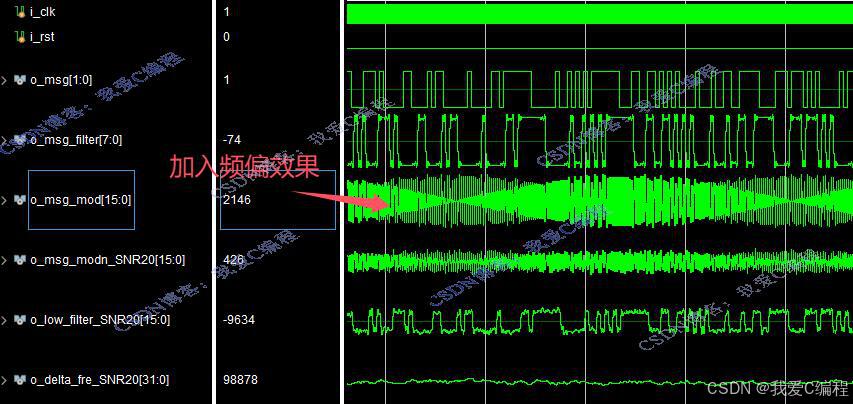

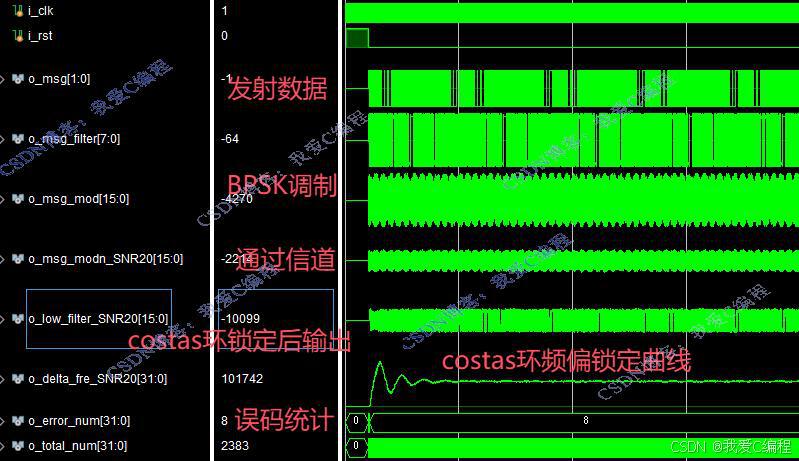

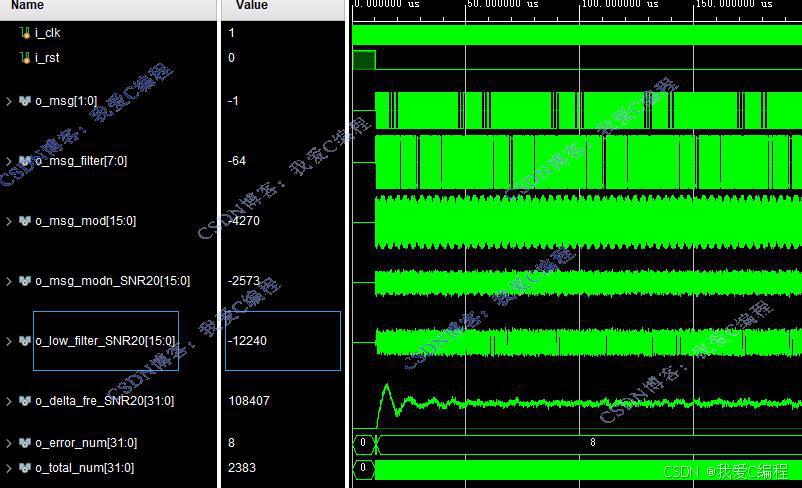

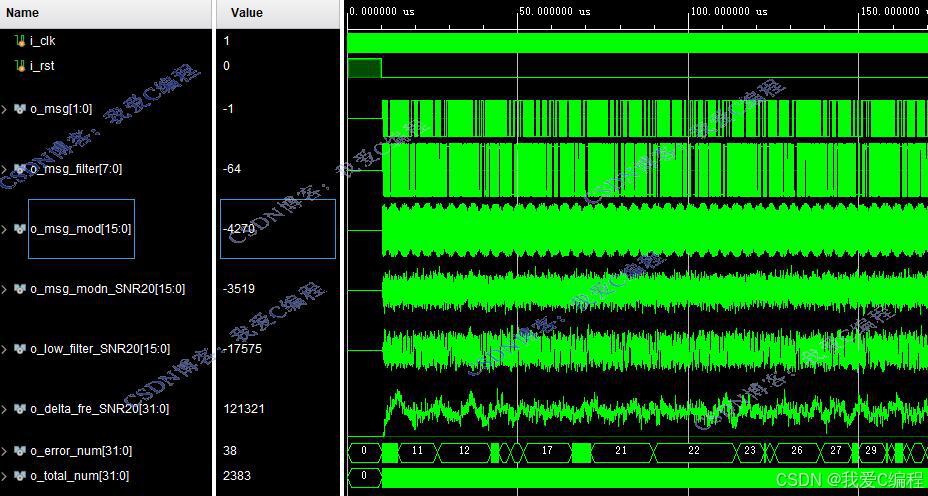

加入频偏:

设置SNR=30db

(无误码,上图中误码个数8为costas锁定过程中带来的)

设置SNR=15db

(无误码,上图中误码个数8为costas锁定过程中带来的)

设置SNR=5db

(误码2400个测试符号,错误30个,其中8个误码为costas锁定过程中带来的)

2.算法涉及理论知识概要

Costas环是一种用于载波同步的常见方法,特别是在调制解调中,它被广泛用于解调相位调制信号,如二进制调相(BPSK)或四进制调相(QPSK)信号。它的目的是估计和追踪接收信号的相位偏移,以便正确解调数据。

其基本结构如下图所示:

Costas环结构:

如上图所示Costas环包括两个主要部分:一个偏移90度的本地振荡器(Local Oscillator,LO)和一个相移解调器。这两个部分协同工作来估计信号的相位偏移。

Costas环包括以下主要组件:

本地振荡器(Local Oscillator,LO): LO产生一个本地参考信号,其频率与接收信号的载波频率相同。这个本地参考信号通常包括正弦和余弦两路信号,相位相差90度。这两路信号将与接收信号相位进行比较。

相位解调器(Phase Detector): 相位解调器用于测量接收信号和本地振荡器之间的相位差。它的输出是一个带有相位信息的信号。

环路滤波器(Loop Filter): 环路滤波器对相位差信息进行滤波和处理,以生成一个控制电压。这个电压将用于调整本地振荡器的频率和相位,以最小化相位差。

本地振荡器控制单元: 这个单元接收来自环路滤波器的控制电压,并相应地调整本地振荡器的频率和相位。

输出: Costas环的输出是本地振荡器的相位信息,该信息已经被调整,以与接收信号的相位保持同步。这个输出可以用于解调接收信号。

Costas环原理:

Costas环的原理是利用接收信号和LO之间的相位差异来估计信号的相位偏移。当信号的相位偏移接近0或180度时,乘积信号的幅值最大,而当相位偏移接近90或270度时,乘积信号的幅值最小。因此,通过测量乘积信号的幅值,可以估计相位偏移。

设调制信号为m ( t ) ,m ( t ) 中无直流分量,则抑制载波的双边带信号为:

和接收信号相乘后,得到的信号为

滤波之后得到:

乘法鉴相器输出得到

当频偏较小时,上述公式近似为:

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/12/22 20:48:51

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

reg i_clk;

reg i_rst;

wire signed[1:0]o_msg;

wire signed[7:0]o_msg_filter;

wire signed[15:0]o_msg_mod;

wire signed[15:0]o_msg_modn_SNR20;

wire signed[15:0]o_low_filter_SNR20;

wire signed[31:0]o_delta_fre_SNR20;

signal signal_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_bits (o_msg)

);

tops_costas tops_costas1(

.i_clk (i_clk),

.i_rst (i_rst),

.i_SNR (5),

.i_msg (o_msg),

.o_msg_filter (o_msg_filter),

.o_msg_mod (o_msg_mod),

.o_msg_modn (o_msg_modn_SNR20),

.o_low_filter (o_low_filter_SNR20),

.o_delta_fre (o_delta_fre_SNR20)

);

wire [31:0]o_error_num;

wire [31:0]o_total_num;

Error_Chech Error_Chech_us(

.i_clk (i_clk),

.i_rst (i_rst),

.i_trans (o_msg),

.i_rec (o_low_filter_SNR20),

.o_error_num (o_error_num),

.o_total_num (o_total_num)

);

initial begin

// Initialize Inputs

i_clk = 1;

i_rst = 1;

// Wait 100 ns for global reset to finish

#10250

i_rst = 0;

// Add stimulus here

end

always #5 i_clk=~i_clk;

endmodule

0sj_074m4.完整算法代码文件获得

V

3823

3823

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?