个人知乎文章搬运,欢迎关注h700 - 知乎电子科技大学 硕士研究生 回答数 0,获得 2 次赞同![]() https://www.zhihu.com/people/h700-87知乎文章链接(verilog)一步步带你手写异步FIFO - 知乎FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,没有外部读写地址线,使用起来非常简单,只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以…

https://www.zhihu.com/people/h700-87知乎文章链接(verilog)一步步带你手写异步FIFO - 知乎FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,没有外部读写地址线,使用起来非常简单,只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以…![]() https://zhuanlan.zhihu.com/p/545512508

https://zhuanlan.zhihu.com/p/545512508

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,没有外部读写地址线,使用起来非常简单,只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。也正是由于这个特性,使得FIFO可以用作跨时钟域数据传输和数据位宽变换。

本篇文章分析异步FIFO的实现原理并用verilog手写实现异步FIFO。

一、双端口RAM

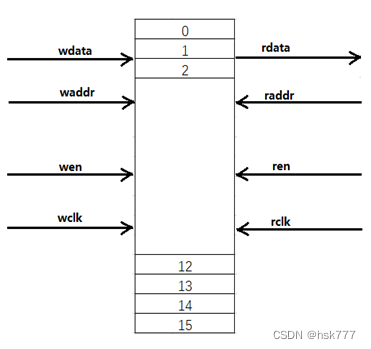

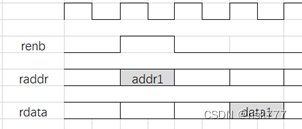

FIFO中用来存储数据的器件为双口RAM,我们首先搭建一个Dual Ram(双口RAM)。我们以一个深度为16,数据位宽为8的Dual Ram为例,框图和时序如下。

Dual Ram读端和写端采用两个时钟,可以实现读写时钟为异步时钟,也可以实现读写同时进行的功能。代码实现如下:

声明端口与内部信号

module Dual_Ram#(parameter ADDR_WIDTH=4 ,DATA_WIDTH=8)( input wclk,input rclk, input wr_en,input rd_en, input [AD

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3379

3379

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?