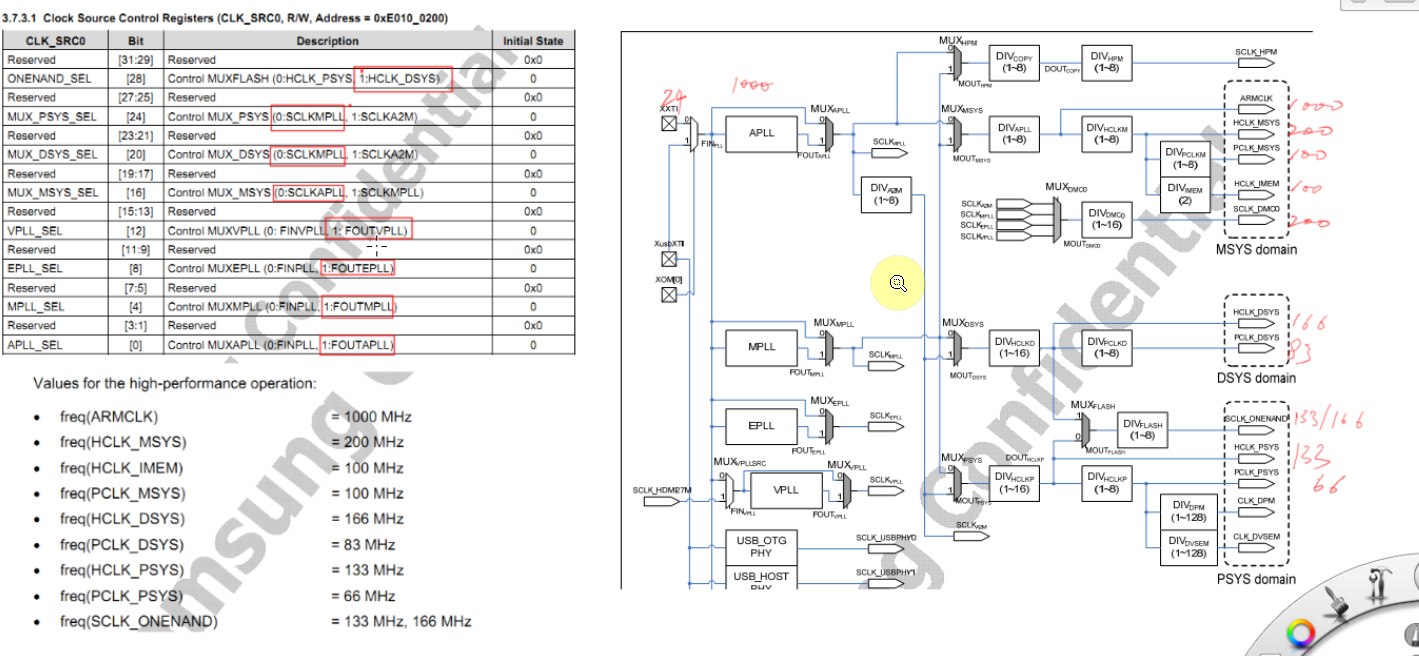

一、 理解时钟系统的在通信时的作用

1) 目标时钟的三要素

a) 时钟源频率(24MHz)

i. 时钟源一般来自于上一级时钟系统,(或者PLL倍频输出,外部时钟源直接提供)

b) MUX(多路分选器)

i. 可以为时钟选择不同的时钟源

c) DIVIder分频器

i. 可以通过DIV分频器分频之后,再给下一级

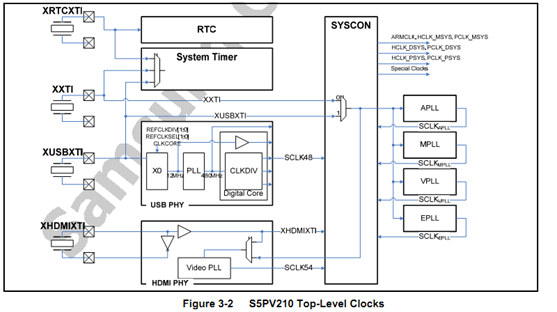

2) PLL倍频

APLL(为主频提供倍频时钟) -----------> MSYS

MPLL/EPLL(为多媒体(video)提供倍频时钟) ------------> DSYS

UPLL(为外部设备提供倍频时钟) ---------------> PSYS二、 系统时钟配置的一般步骤

1) 设置系统锁相环电路(PLL)的锁定时间

xxxx_LOCK = 一个周期时间 * 频率

APLL_LOCK = 30 * 24 = 720us;

MPLL_LOCK = 200 * 24 = 4800us;

EPLL_LOCK = 375 * 24 = 9000us;

VPLL_OCK = 100 * 24 = 2400us;

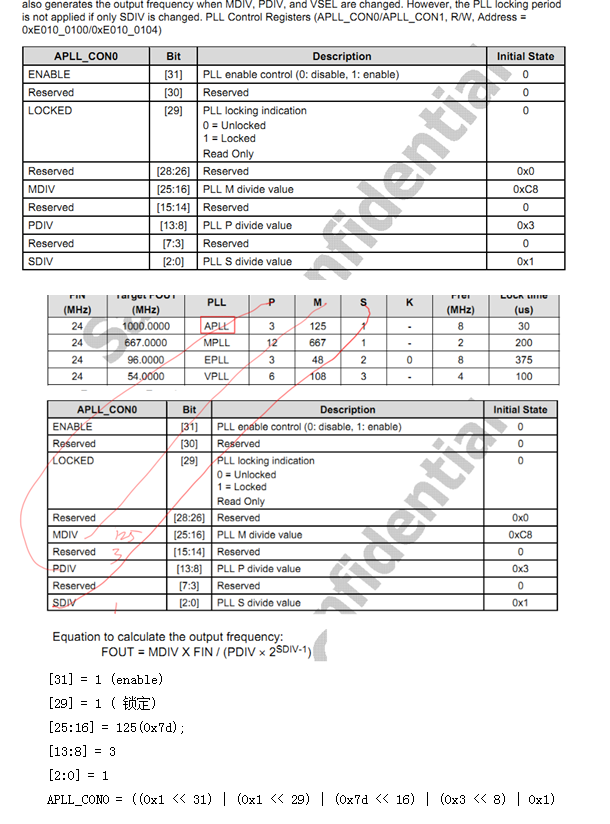

2) 配置配平器(PLL) a) 配置

[31] = 1 (enable)

[29] = 1 ( 锁定)

[25:16] = 125(0x7d);

[13:8] = 3

[2:0] = 1

APLL_CON0 = ((0x1 << 31) | (0x1 << 29) | (0x7d << 16) | (0x3 << 8) | 0x1)

b) 配置MPLL_CON

MPLL_CON = (0x1 << 31)|(0x1 << 29) | (0x29b << 16) | (0xc << 8) | (0x1 << 0)

3) 选择时钟源

CLK_SRC0 = 10001111;

4) 配置MDIV,PDIV,SDIV的分频系数CLK_DIV0 = (0x1 << 28) | (0x4 << 24) | (0x1 << 20) | (0x3 << 16) | (0x1 << 12) | (0x4 << 8)

| (0x4 << 4) | (0x0 <<< 0);

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?