第四章 处理器体系结构

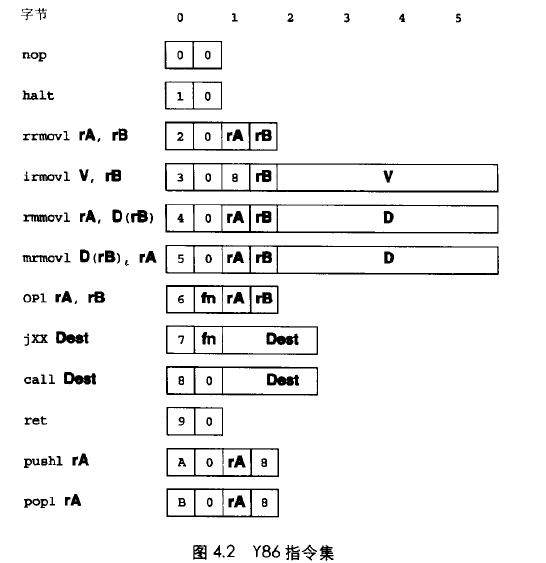

一个处理器支持的指令和指令的字节级编码称为它的ISA(instruction-set architecture,指令体系结构)。

ISA 在编译器编写者和处理器设计人员之间提供了一个概念抽象层。

描述硬件系统控制部分的简单语言,HCL(Hardware Control Language,硬件控制语言)

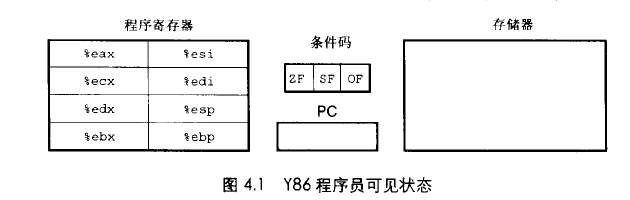

4.1 Y86指令集体系结构

指令集的一个重要性质是字节编码必须有惟一的解释。

4.2 逻辑设计和硬件控制语言HCL

4.2.1 逻辑门

逻辑门总是active。一旦一个门的输入变化可,在很短的时间内,输出就会相应的变化。

4.2.2 组合电路和HCL布尔表达式

计算块(computational block)即组合电路,很多逻辑门组合成的网。组成这个网的两个规定:

两个或多个逻辑门的输出不能接在一起,否则可能会线上信号矛盾,导致不合法的电压或电路故障。

这个网必须是无环的。

多路复用器

4.2.3 字级的组合电路和HCL整数表达式

设计对数据字(data words)操作的电路。

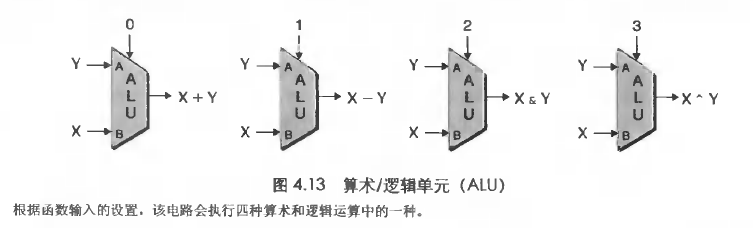

算术/逻辑单元(ALU)是一种重要的组合电路。

4.2.4 集合关系(Set Membership)

4.2.5 存储器和时钟控制

时序电路(sequential circuit)。

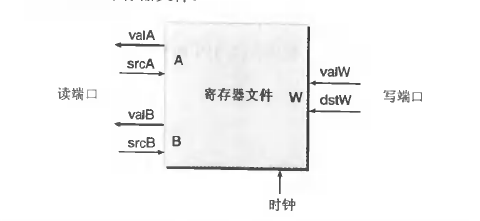

两类存储设备:时钟寄存器。随机访问存储器。

典型的寄存器文件

4.3 Y86的顺序实现

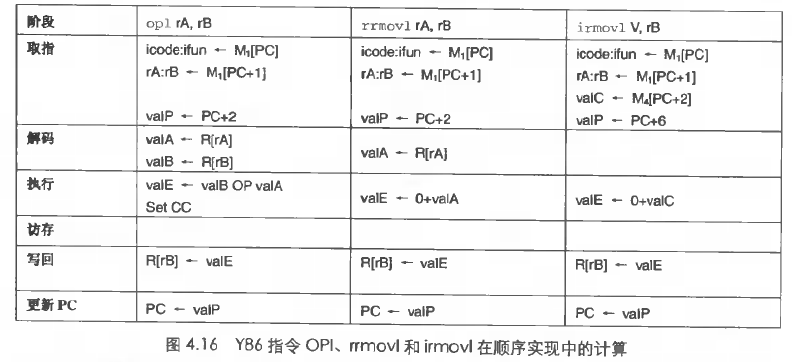

4.3.1 将处理组织成阶段

取指:icode(指令代码),ifun(指令功能)

解码

执行

访存

写回

更新PC

4.3.2 SEQ 硬件结构

4.3.3 SEQ 的时序(timing)

4.3.4 SEQ 的阶段实现

4.3.5 SEQ+: 重新安排计算阶段

4.4 流水线的通用原理

吞吐量,执行时间

4.4.1 计算流水线

4.4.2 流水线操作的详细说明

4.4.3 流水线的局限性

不一致的划分

流水线过深,收益反而下降

4.4.4 带反馈的流水线系统

数据相关

控制相关

4.5 Y86的流水线实现

4.5.1 插入流水线寄存器

4.5.2 对信号进行重新排列和标号

4.5.3 预测下一个PC

设计目的:每个时钟周期都发射(issue)一个指令。

分支预测

4.5.4 流水线冒险(hazard)

数据相关和控制相关。这些相关可能会导致流水线产生计算错误,称为冒险。

数据冒险和控制冒险

4.5.5 用暂停(stalling)来避免数据冒险

4.5.6 用转发(forwarding)来避免数据冒险

将结果值直接从一个流水线阶段传到较早阶段的技术称为数据转发。

4.5.7 加载/使用(load/use)数据冒险

4.5.8 PIPE 各阶段的实现

PC选择和取指阶段

解码和写回阶段

执行阶段

访存阶段

4.5.9 流水线控制逻辑

4.5.10 性能分析

4.5.11 未完成的工作

496

496

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?