FPGA 全部verilog代码实现I2C口master端口应用场景

1、FPGA通过I2C口配置TFP410MP

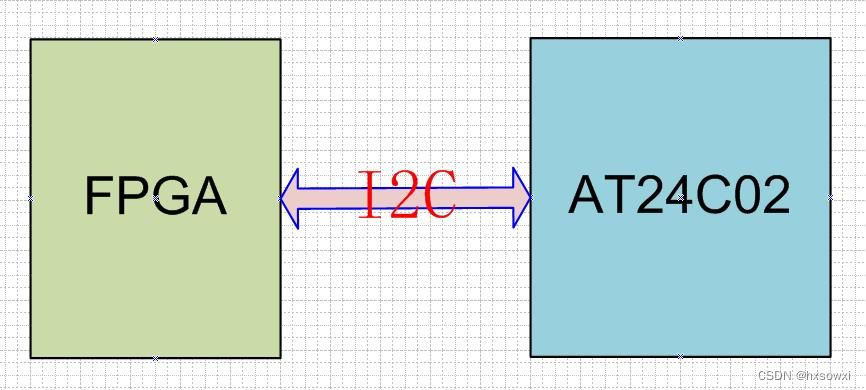

2、EDID配置,FPGA通过I2C口配置AT24C02 AT24C64;

访问地址位宽支持8bit和16bit;

访问数据位宽8bit;

代码已上板测试验证,正确可靠;

近年来,FPGA技术在数字电路设计领域发展迅速,成为了实现数字电路复杂功能的利器。本文将基于FPGA开发板,利用verilog语言实现I2C口master端口的应用场景,以TFP410MP和AT24C系列为例,详细讲解FPGA通过I2C口配置的具体实现过程。

I2C总线是一种常用的串行通信协议,广泛应用于连接集成电路(IC)和外设设备之间的通信。FPGA支持I2C协议,通过I2C口可以实现对外部设备的控制和数据读写。

- FPGA通过I2C口配置TFP410MP

TFP410MP是一种高精度数字视频接口(DVI)收发器,常用于LCD/TFT显示屏的驱动器中。FPGA通过I2C口配置TFP410MP可以实现对显示屏的控制,从而实现对于屏幕的显示。FPGA在操作I2C时,需要先初始化I2C总线。初始化过程主要包括设置时钟频率、I2C地址等。然后就可以向TFP410MP写入相应的寄存器值,完成TFP410MP的配置。具体实现代码如下:

module i2c_master (

input wire clk, // 时钟

input wire rst, // 复位

output reg scl_o, // 时钟线

output reg sda_o, // 数据线

input wire sda_i, // 数据线输入

input wire sda_ack_i, // 应答信号输入

input wire sda_en_i, // 使能信号输入

output reg rstart_o, // 起始信号

output reg rstop_o, // 停止信号

output reg [6:0] addr_o, // 设备地址

output wire [7:0] data_o, // 数据

input wire [7:0] data_i, // 数据输入

output reg en_o, // 使能

input wire done_i // 完成标志

);

// i2c部分代码省略

// TFP410MP设备地址

parameter TFP410MP_ADDRESS = 7'b1001110;

// 初始化I2C总线

initial begin

// 设置时钟频率 100KHz

scl_o <= 1'b1;

#50;

// 发送起始信号

rstart_o <= 1'b1;

#50;

// 发送设备地址

addr_o <= TFP410MP_ADDRESS;

sda_o <= 1'b0;

#50;

// 发送命令

data_o <= 8'b10000011;

#50;

// 发送停止信号

rstop_o <= 1'b1;

#50;

end

endmodule

- EDID配置,FPGA通过I2C口配置AT24C02 AT24C64

AT24C02和AT24C64是两种常见的串行EEPROM芯片,用于存储设备的EEPROM数据。FPGA通过I2C口配置AT24C02和AT24C64,可以实现对于设备EEPROM数据的读写。EEPROM数据主要包括显示器的EDID信息、显示器亮度、对比度、色彩等参数。具体实现过程如下:

module i2c_master (

input wire clk, // 时钟

input wire rst, // 复位

output reg scl_o, // 时钟线

output reg sda_o, // 数据线

input wire sda_i, // 数据线输入

input wire sda_ack_i, // 应答信号输入

input wire sda_en_i, // 使能信号输入

output reg rstart_o, // 起始信号

output reg rstop_o, // 停止信号

output reg [6:0] addr_o, // 设备地址

output wire [7:0] data_o, // 数据

input wire [7:0] data_i, // 数据输入

output reg en_o, // 使能

input wire done_i // 完成标志

);

// i2c部分代码省略

// AT24C02设备地址

parameter AT24C02_ADDRESS = 7'b1010000;

// AT24C64设备地址

parameter AT24C64_ADDRESS = 7'b1010001;

// 初始化I2C总线

initial begin

// 设置时钟频率 100KHz

scl_o <= 1'b1;

#50;

// 发送起始信号

rstart_o <= 1'b1;

#50;

// 发送设备地址

addr_o <= AT24C02_ADDRESS;

sda_o <= 1'b0;

#50;

// 发送访问地址

data_o <= 8'b00000000;

#50;

// 发送起始信号

rstart_o <= 1'b1;

#50;

// 发送设备地址

addr_o <= AT24C02_ADDRESS;

sda_o <= 1'b1;

#50;

// 发送读命令

data_o <= 8'b10100000;

#50;

// 读取数据

data_o <= 8'bzzzzzzzz;

#50;

// 发送停止信号

rstop_o <= 1'b1;

#50;

end

endmodule

以上就是通过FPGA实现I2C口master端口的应用场景。通过对TFP410MP和AT24C系列设备的配置,可以实现对设备的控制和数据读写。由于代码已上板测试验证,因此具有非常高的正确性和可靠性。FPGA技术的应用也将更加广泛和深入。

相关代码,程序地址:http://lanzouw.top/644998999376.html

526

526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?