Compiler Optimization on VLIW Instruction Scheduling for Low Power

ChingRen Lee, Jenq Kuen Lee, TingTing Hwang

National Tsing-Hua University, Taiwan

ACM Transactions on Design Automation of Electronic Systems, 2003

CSDN图片审核,我把博文上传到资源里,需要的朋友可以在这里下载。

多DSP核心(VLIW架构)的嵌入式系统,往往要求高性能与低功耗。本文侧重后者,基于VLIW架构做指令总线上指令调度的优化,编译器的改造工作。

![]()

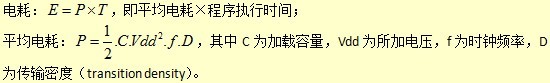

以上公式表明,编译器优化,要么减小T,要么减小D,本文关注后者。

先来一张架构图,看看总线模型:

图1. 一个VLIW机器架构和总线模型

ü 建模

采用Hamming码作为代价函数:

其中X,Y是连续的两条k-way发射的VLIW指令,Xi、Yi分别为X、Y的指令分量,H(X, Y)表示两指令间的汉明码距离,即两指令有几位不一样的。

图2. 汉明码示意

ü 指令调度策略

分两个阶段,一阶段采用list scheduling做性能优化,而后我们reschedule这份指令以降低功耗。可做水平调度和垂直调度,水平调度指一条指令里的各“微指令”间水平方向上的交换,垂直调度指上下连续若干条指令里的各“微指令”间垂直方向上的交换。

a) 水平调度

给出一种贪心机制(greedy bipartite-matching scheme),并证明在给定的VLIW指令调度策略基础上该机制总是最优的,给出最优的指令总线切换活动。

图3. 水平调度的bipartite-matching示意图

建立bipartite matching图,赋边权"-Hamming"。这里求最优方案最大值,故取各汉明码的相反数。很简单的贪心算法,每次贪最大的(也即Hamming最小的,指令间区别最小的)则最后全局最大,形成最优方案。理论证明很简单,反证,如果能找到更优的,那么我们的当前阶段一定某个阶段非最优的,与每阶段最优矛盾。

伪码如下:

图4. 水平调度伪码

b) 指令调度策略之垂直调度

证明这是一个NP难问题,继而给出一个启发式算法。

输入还有DDG的critical path,关键路径上的节点往往很高贵需要特殊待遇(这里指关键路径上的节点只允许做水平调度,垂直方向不可以)。

图5. 垂直调度伪码与图解

ü 如何做实验

实验环境:Alpha-based VLIW arch, a compiler based on SUIF + machSUIF + our scheme, an ATOM simulator on the DEC Alpha UNIX v4.0(插入代价模型即汉明距离)

图6. 将代码注入编译器(in phase 3)

ü 实验结果

与常规的list scheduling相比,水平调度:4-way issue arch平均提高了13.30%,对于8-way issue arch,平均提高了20.15%。水平调度+垂直调度:window size = 4时平均提高了7.66%,window size = 8时,平均提高了10.55%.

1885

1885

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?