每个主存在直接映射cache中恰好映射到一条cacheline。 内存地址中的索引位选择映射的cacheline。

例如,6bit索引位从64个cacheline中选择一个。 tag字段表示内存块的地址,该内存块映射到索引字段选择的cacheline。 因此,有2^tag内存块映射到同一cacheline! 这可能会导致大量的cache冲突,导致cacheline过早地替换成另一个cacheline。

为了缓解cache冲突,我们使用结构略有不同的组相联cache。 在组相联cache中,我们将多个cacheline分组到一个集合set中。 在这里,内存块映射到同一个集合中的任何可用cacheline, 因此冲突较少。

在组相联cache中,术语N-way组相联cache是指cache的关联性级别。具体来说,N路组相联cache意味着cache中的每个集合都包含N个cacheline。

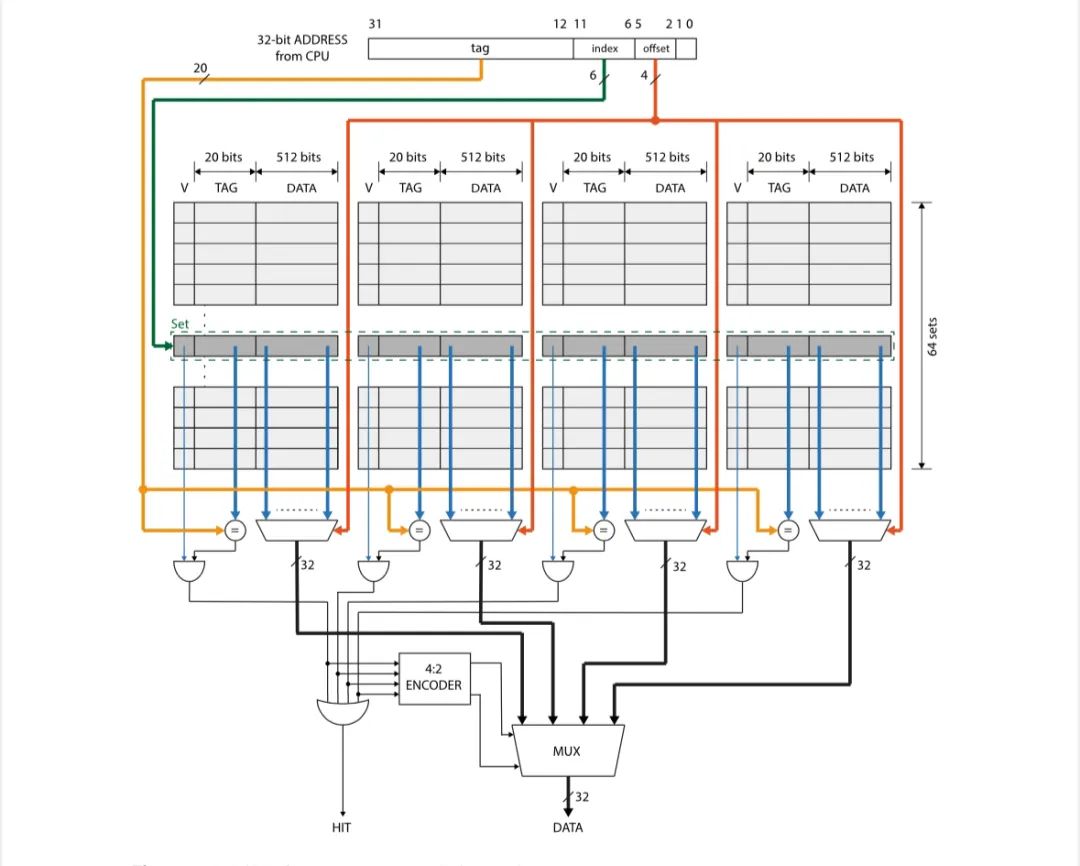

上图中描绘了16 kB四路组相联cache。在4路组相联cache中,当向cache提供内存地址时,cache控制器会解释地址以确定组的index、tag和offset。

tag位唯一标识主存中的内存块。它用于检查cacheline中的数据是否与请求的数据相同。index字段指定将请求的内存块映射到cache中的哪个set。

offset在cacheline中标识所需内存字的位置。

上图中的cache包含64(2^6)组。 每组包含16个32位数据字的四行cache。 因此,cache的大小为64组×每组4行×16×4B=16kB。

在选定的set中,内存字由每个cacheline中的四个多路复用器选择。

将所选set中所有四个cacheline的tag字段与内存地址的tag字段进行比较, 如果有匹配并且设置了有效位,则会发生cache hit。 否则,会发生cache miss。假设第三个cacheline中的tag字段等于所提供地址的tag字段。 在这种情况下,使用mux选择第三条cacheline的32位数据字。

659

659

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?