最简单或者说最直观的内存一致性模型是顺序一致性(sequential consistency,SC)。顺序一致性定义如下:

“the result of any execution is the same as if the operations of all processors (cores) were executed in some sequential order, and the operations of each individual processor (core) appear in this sequence in the order specified by its program.”

Lamport

简单来说,就是程序在多核心上执行时就像是在单核心上执行一样,并且原先单核心上的指令执行顺序保持不变。

这里就要区分两个概念:memory order和program order。memory order是指总的程序执行时的memory操作顺序,program order是指单个核心上指令执行的逻辑上顺序。

在SC中,memory order遵循每个核心的program order。

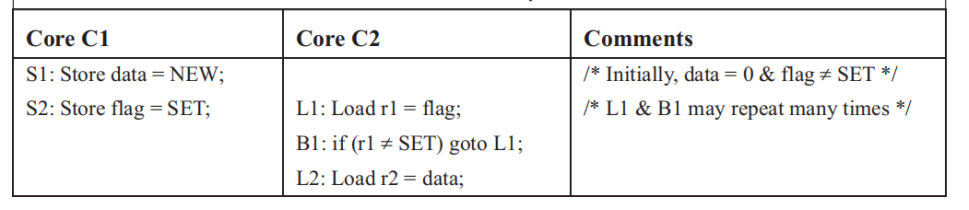

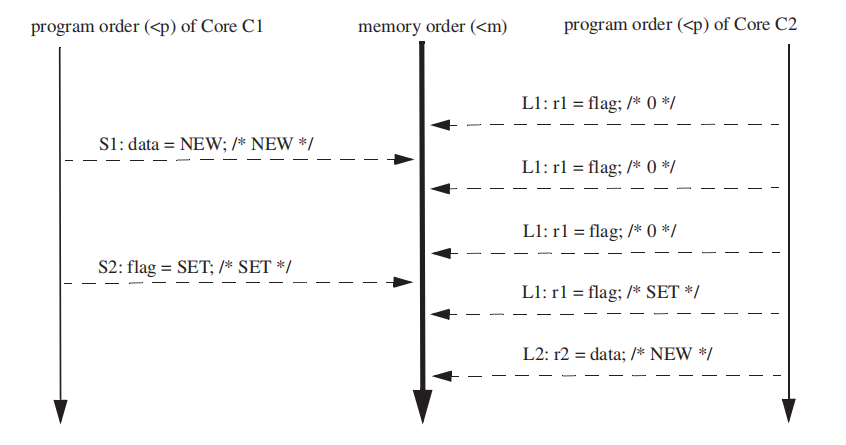

上表和图分别是遵循SC模型的示例程序program order(左右向下箭头)和memory order (中间向下箭头) 。也就是说在SC模型中memory order 总是遵循program order。

op1 >p op2 ---> op1 >m op2

上述程序执行结果总是r2=NEW,消除了在多处理器程序中的结果不确定性。唯一的不确定性 L1 load多少次,但是这已经对功能无存在什么影响了。

在实现这种顺序一致性模型是也很简单。如果你的目标是单核心里面的多个并行进程,在不同进程间做好同步即可,T1的指令在进程C1上执行完之后再切换到进程T2,反之亦然。如果你针对的是多个CPU核心,就是用随机切换的开关或者RR仲裁等。

上述的实现方式使得这些多核心并非完全并行执行,CPU核心的增多对性能的提高可能并没有显著的作用。

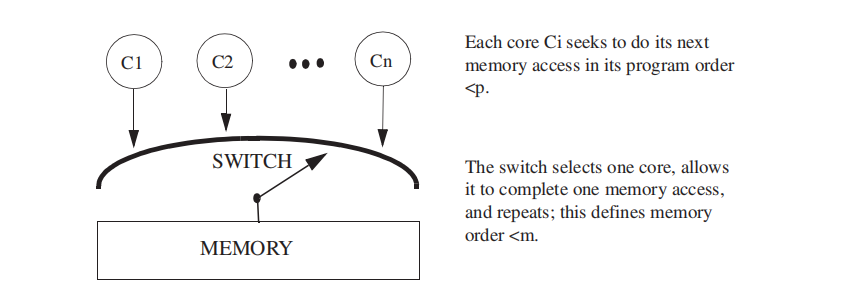

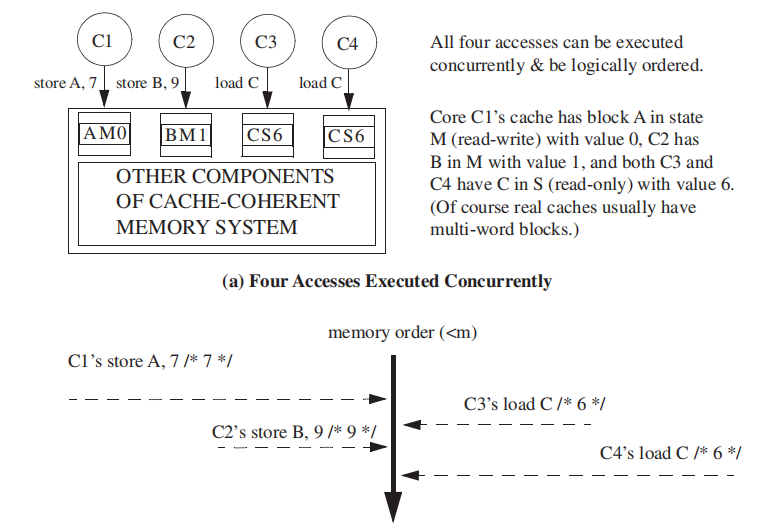

而缓存一致性促进了SC实现,就算两个核心的内存操作位于同一地址,如果是non-conflicting的,还是可以完全并行的。

这需要了解cache一致性相关内容,以及各自cache block的状态含义。上图中Block A和Block B状态为write-read,block C状态为read-only。这时候C1写Block A,C2写Block B,同时C3和C4读Block C 完全是可以并行的,不会引起数据正确性问题。

866

866

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?