fpga图像缩放代码及相关资料

ID:56600718070748482

tb_bysg

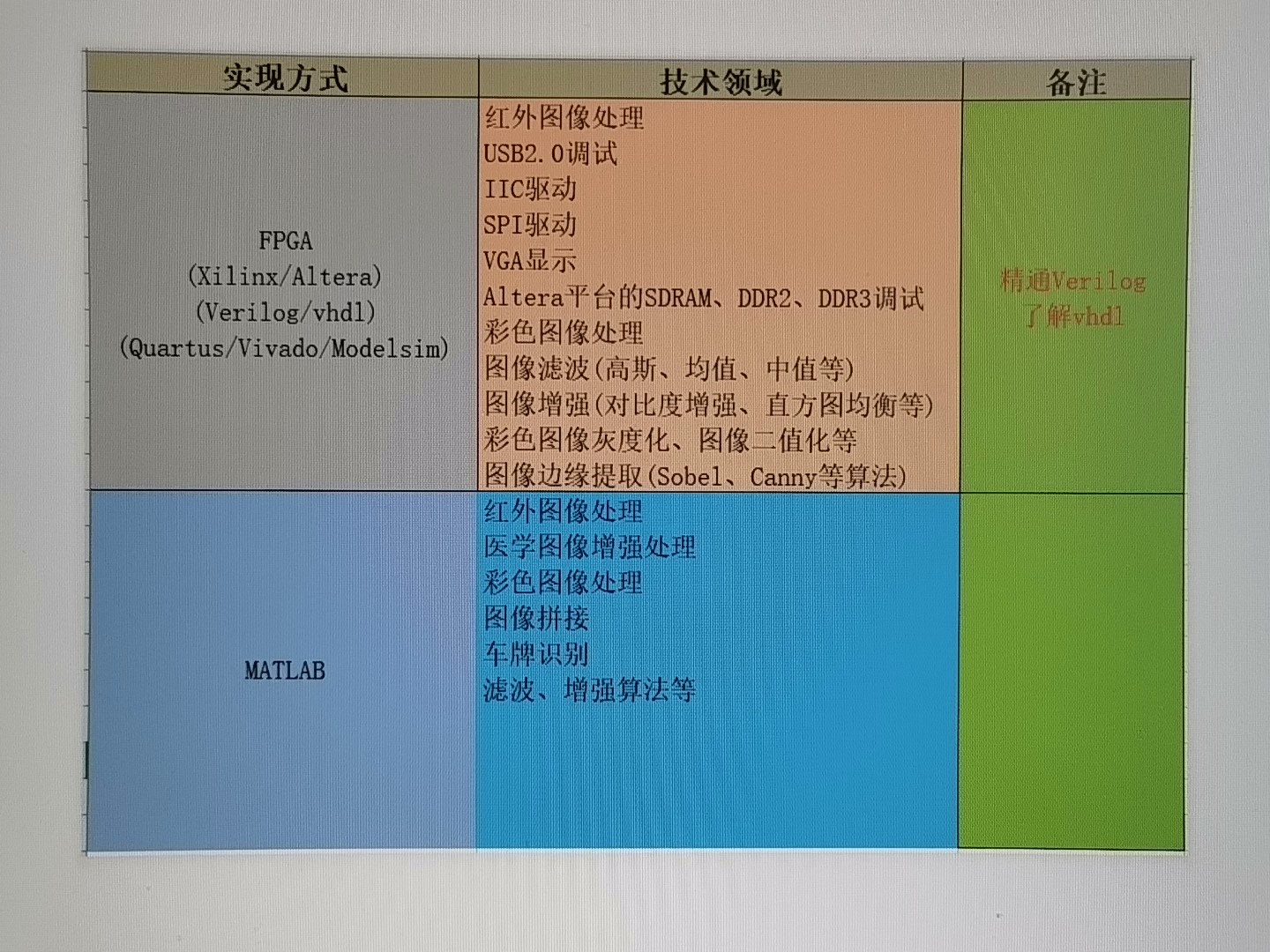

FPGA (Field Programmable Gate Array)是一种可编程逻辑器件,广泛应用于图像处理领域。图像缩放是图像处理中常见的操作之一,可以将图像的尺寸进行放大或缩小。在本文中,我们将重点讨论FPGA图像缩放代码及相关资料。

图像缩放在许多应用中具有重要的作用,例如数字摄像机、医学成像、视频游戏等。 在这些应用中,我们通常需要将图像的尺寸进行调整,以便适应不同的显示屏或者其他设备的要求。 与软件实现相比,FPGA具有并行处理的能力,可以提供更高的处理性能和更低的延迟。

在FPGA图像缩放代码的实现中,我们通常需要考虑以下几个关键因素:图像数据存储、图像数据传输、缩放算法以及系统时钟同步。

首先,图像数据存储是实现图像缩放的基础。 FPGA通常具有大容量的片上存储器(BRAM),可以用于存储图像数据。 在图像缩放过程中,我们需要将输入图像数据存储在BRAM中,并在缩放完成后将结果写回BRAM。

其次,图像数据传输是实现图像缩放的关键。 FPGA通常具有高带宽的外部存储器接口(如DDR3),可以用于传输图像数据。 在图像缩放过程中,我们需要将输入图像数据从外部存储器传输到FPGA内部,并在缩放完成后将结果传输回外部存储器。

缩放算法是实现图像缩放的核心。常见的图像缩放算法包括最近邻插值、双线性插值和立方插值等。在FPGA中,我们可以使用定点数乘法和累加器等硬件资源来实现这些算法,以提高处理性能和减少延迟。

最后,系统时钟同步是实现图像缩放的基本要求。 FPGA中有多个时钟域,我们需要确保输入图像数据和输出图像数据在不同时钟域之间的同步。 可以通过FIFO(First-In-First-Out)缓冲区来实现时钟域之间的数据传输,并采取合适的同步机制来解决时钟偏差和抖动问题。

在实际应用中,为了实现高质量的图像缩放效果,我们还可以考虑其他因素,例如抗锯齿滤波、平滑处理以及多通道并行处理等。 这些技术可以提高图像的清晰度、减少伪影和噪声,并实现实时的图像缩放效果。

综上所述,FPGA图像缩放代码及相关资料是实现图像处理的重要组成部分。通过代码的实现和相关资料的整理,可以帮助开发者理解图像缩放的原理和实现方法,并实现高性能、低延迟的图像缩放应用。在今后的研究和应用中,我们可以进一步探索FPGA在图像处理领域的潜力,提升图像处理的效果和性能。

这篇文章旨在介绍FPGA图像缩放代码及相关资料,从图像数据存储、传输、缩放算法和系统时钟同步等方面进行了讨论。希望读者通过阅读本文,能够了解FPGA图像缩放的基本原理和实现方法,并在实际应用中能够灵活运用。通过不断地研究和探索,我们可以进一步提升FPGA在图像处理领域的性能和应用范围,为图像处理技术的发展贡献一份力量。

以上相关代码,程序地址:http://wekup.cn/718070748482.html

353

353

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?