一、IO接口分析基本模型

数据按照同步方式可分为系统同步和源同步方式两种。所谓系统同步指发送端和接收端共用一个时钟源;源同步指发送端提供数据同步时钟,接收端根据该时钟进行数据接收。现在多数通信中使用源同步方式,例如以太网、ADC等。

此外还有自同步方式,在这不做介绍。

二、input delay分析

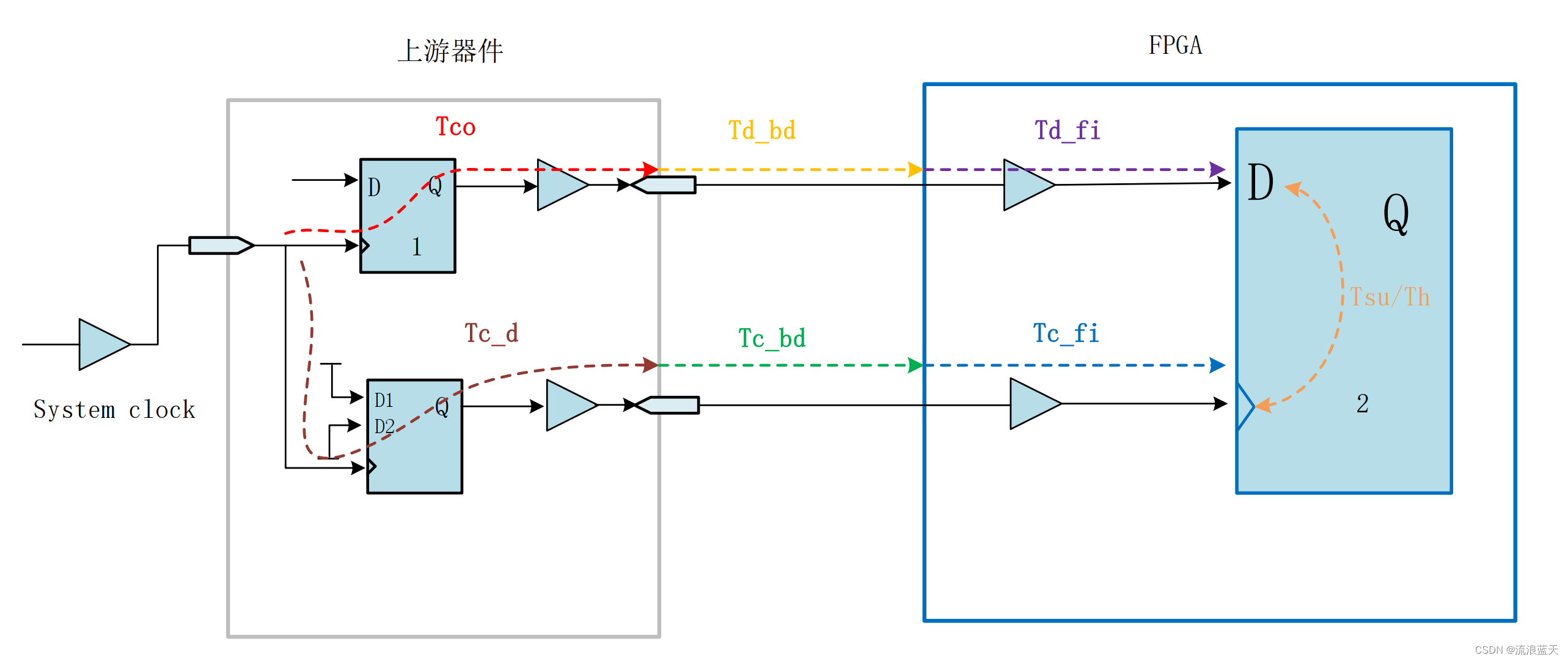

首先进行input delay分析。既然分析“input”,那么FPGA就是接收端,接收来自外部芯片(发送端)的数据和同步时钟,这里我们把发送端称为上游器件。input delay分析模型如下图:

图中不同颜色的虚线表示不同的信号传输路径,对应传输延时含义如下:

|

Tco | Tco指上游器件中的数据延时,包括时钟到reg1的延时Tco1、数据从reg1的D端到Q端的延时Tco2以及数据从reg1的Q端到上游器件pad的延时 |

| Tc_d | 时钟在上游器件内部的延时 |

| Td_bd | 数据信号的PCB板级延时 |

| Tc_bd | 时钟信号的PCB板级延时 |

| Td_fi | 数据信号在FPAG内部的延时 |

| Tc_fi | 时钟信号在FPAG内部的延时 |

| Tsu\Th | FPGA接收(输入)寄存器的建立时间门限\保持时间门限 |

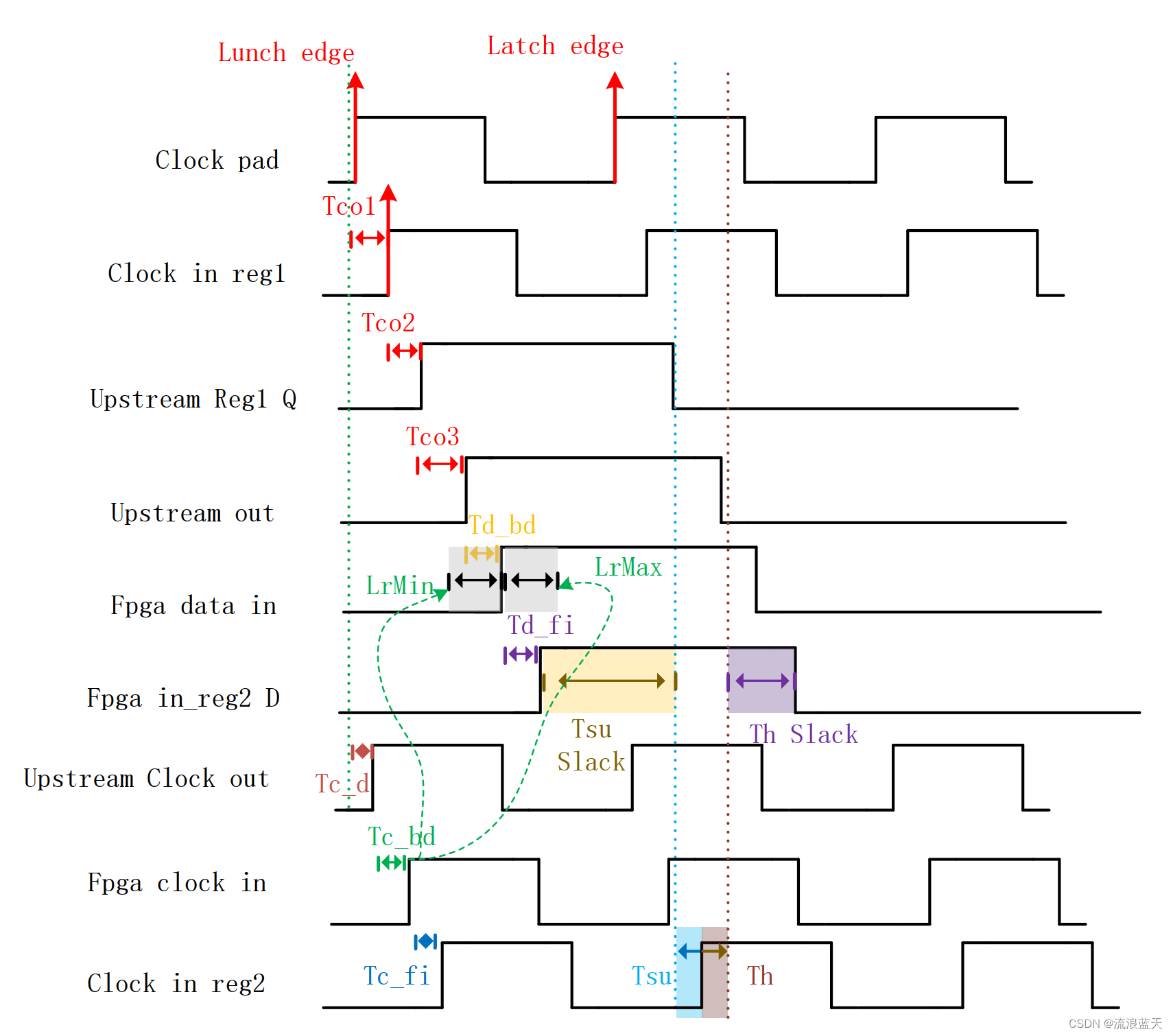

根据分析模型可以得到时序图:

图中各波形的含义从他们的名字就可以看出,其中Fpga data in指数据到达FPGA的输入引脚,Fpga clock in指时钟信号到达FPGA的输入引脚,这两个信号波形很重要,后边会讲为什么。

画出时序图,很容易就可以得到:

- 数据达到FPGA中reg2D端的实际时间Data Arrival time = Tco + Td_bd + Td_fi

- 数据达到FPGA中reg2D端的要求时间Data Required time = Tcycle + Tc_d + Tc_bd + Tc_fi – Tsu

- 建立时间裕量Setup Slack = Data Required time - Data Arrival time

同样可得:

- 数据达到FPGA中寄存器D端的实际结束时间Data End time = Tcycle +Tco + Td_bd + Td_fi

- 数据达到FPGA中寄存器D端的要求结束时间Data Required End time = Tc_d + Tc_bd + Tc_fi + Tcycle + Th

- 保持时间裕量Hold Slack = Data End time - Data Required End time

知道了建立时间裕量和保持时间裕量,我们就可以做时序分析了,即要想不发生时序违例,必须满足建立时间裕量Setup Slack > 0,保持时间裕量Hold Slack > 0。

但是以上计算为通用公式,我们知道实际数据信号传输是以总线的方式,数据到达FPGA输入引脚的延时可能大也可能小,称作数据skew。

观察图中波形,Fpga in data延时变大时会压缩建立时间裕量,因此在延时最大时分析建立时间时序。如果延时最大时仍旧没有发生时序违例,那么延时小时更不会。同理,Fpga in data延时变小时会压缩保持时间裕量,因此在延时最小时分析保持时间时序。如果延时最小时仍旧没有发生时序违例,那么延时大时更不会。

现在我们以分析建立时间为例,要想分析时序是否违例,根据上文必须要知道Tco max、Td_bd max和Td_fi_max。对于FPGA来说或者对于编译器来说,Td_fi和Tc_fi是已知的(因为他们在FPGA内部),而Tco、Tc_d、Tc_bd和Td_bd是未知的。因此我们要告诉编译器输入到FPGA管脚的时钟和数据的关系(Tco、Td_bd),也就是上文提到的Fpga data in和Fpga clock in之间的关系,这也是input delay约束的目的所在。

现在计算Setup Slack = Data Required time - Data Arrival time

= cycle + Tc_d + Tc_bd + Tc_fi – Tsu - (Tco max + Td_bd max + Td_fi max),结合时序图可知,input delay约束的就是发射沿lunch到数据有效的延时,即时序图中的:

LrMax = Tco max + Td_bd max -(Tc_d + Tc_bd) ------分析建立时间时序

LrMin = Tco min + Td_bd min -(Tc_d + Tc_bd) ------分析保持时间时序

6831

6831

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?