这里写自定义目录标题

- 编译Vivado仿真库报错

- Warning: (vlog-159) Mode option -64 is not supported in this context and will be ignored.

- # ** Warning: (vsim-8683) Uninitialized out port /tb_ip_fft2/u_top/u_ip_fft/u_xfft_0/U0///(0) has no driver.

- # Block Memory Generator module tb_ip_fft2.u_top.u_ip_ram.u_ram.inst.native_mem_module.blk_mem_gen_v8_4_2_inst is using a behavioral model for simulation which will not precisely model memory collision behavior.

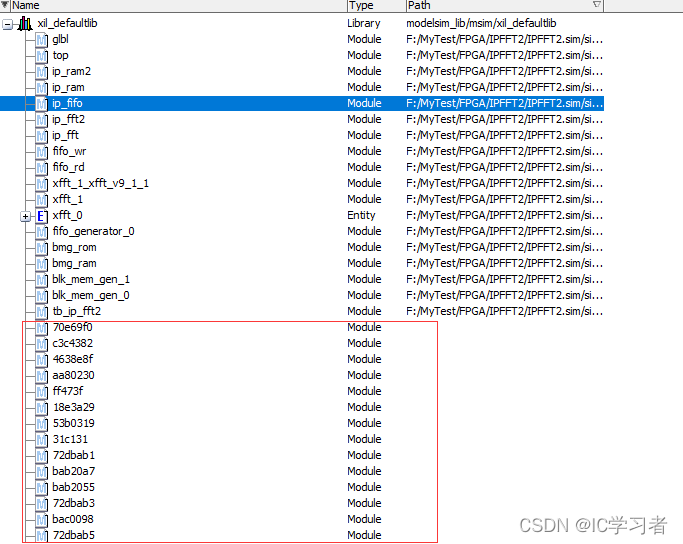

- xil_defaultlib中包含未知模块

- Break in file E:/Program_Files/Xilinx/Vivado/2018.3/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

编译Vivado仿真库报错

原因是Modelsim版本和Vivado版本不匹配,更换版本之后,只有个别IP报错,不影响使用。

68324 - Vivado Simulation - Supported Third party simulators for major Vivado Design Suite release

我是10.6c+2018.3

Warning: (vlog-159) Mode option -64 is not supported in this context and will be ignored.

这个警告一直没啥影响,所以也没有管它,可能就是设置一个选项的事。

或者说是编译仿真库的时候的一个选项

launch_simulation -install_path E:/Program_Files/modelsim_dlx64_10.6c/win64pe

INFO: [Vivado 12-5698] Checking validity of IPs in the design for the 'ModelSim' simulator...

INFO: [Vivado 12-5682] Launching behavioral simulation in 'F:/MyTest/FPGA/IPFFT2/IPFFT2.sim/sim_1/behav/modelsim'

INFO: [Vivado 12-4795] Using compiled simulation libraries for IPs

INFO: [USF-ModelSim-47] Finding simulator installation...

INFO: [USF-ModelSim-50] Using simulator executables from 'E:/Program_Files/modelsim_dlx64_10.6c/win64pe/vsim.exe'

INFO: [SIM-utils-51] Simulation object is 'sim_1'

INFO: [USF-modelsim-7] Finding pre-compiled libraries...

INFO: [USF-modelsim-11] File 'E:/Program_Files/Xilinx/Modelsim_Vivado_Lib/modelsim.ini' copied to run dir:'F:/MyTest/FPGA/IPFFT2/IPFFT2.sim/sim_1/behav/modelsim'

INFO: [SIM-utils-54] Inspecting design source files for 'tb_ip_fft2' in fileset 'sim_1'...

INFO: [SIM-utils-43] Exported 'F:/MyTest/FPGA/IPFFT2/IPFFT2.sim/sim_1/behav/modelsim/blk_mem_gen_1.mif'

INFO: [SIM-utils-43] Exported 'F:/MyTest/FPGA/IPFFT2/IPFFT2.sim/sim_1/behav/modelsim/tran_matrix_para_1024.coe'

INFO: [SIM-utils-43] Exported 'F:/MyTest/FPGA/IPFFT2/IPFFT2.sim/sim_1/behav/modelsim/bmg_rom.mif'

INFO: [SIM-utils-43] Exported 'F:/MyTest/FPGA/IPFFT2/IPFFT2.sim/sim_1/behav/modelsim/fftshift_1024.coe'

INFO: [USF-ModelSim-107] Finding global include files...

INFO: [USF-ModelSim-108] Finding include directories and verilog header directory paths...

INFO: [USF-ModelSim-109] Fetching design files from 'sim_1'...

INFO: [USF-ModelSim-2] ModelSim::Compile design

INFO: [USF-ModelSim-15] Creating automatic 'do' files...

INFO: [USF-ModelSim-69] Executing 'COMPILE and ANALYZE' step in 'F:/MyTest/FPGA/IPFFT2/IPFFT2.sim/sim_1/behav/modelsim'

Reading E:/Program_Files/modelsim_dlx64_10.6c/tcl/vsim/pref.tcl

# 10.6c

# do {tb_ip_fft2_compile.do}

# ** Warning: (vlib-34) Library already exists at "modelsim_lib/work".

# ** Warning: (vlib-34) Library already exists at "modelsim_lib/msim".

# ** Warning: (vlib-34) Library already exists at "modelsim_lib/msim/xil_defaultlib".

# Model Technology ModelSim DE-64 vmap 10.6c Lib Mapping Utility 2017.07 Jul 26 2017

# vmap xil_defaultlib modelsim_lib/msim/xil_defaultlib

# Modifying E:\Program_Files\Xilinx\Modelsim_Vivado_Lib\modelsim.ini

# ** Warning: (vlog-159) Mode option -64 is not supported in this context and will be ignored.

# Model Technology ModelSim DE-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

# Start time: 18:47:20 on Apr 08,2022

# vlog -64 -incr -work xil_defaultlib ../../../../IPFFT2.srcs/sources_1/ip/bmg_rom/sim/bmg_rom.v ../../../../IPFFT2.srcs/sources_1/ip/bmg_ram/sim/bmg_ram.v ../../../../IPFFT2.srcs/sources_1/ip/xfft_1/xfft_1_sim_netlist.v ../../../../IPFFT2.srcs/sources_1/ip/blk_mem_gen_1/sim/blk_mem_gen_1.v ../../../../IPFFT2.srcs/sources_1/ip/blk_mem_gen_0/sim/blk_mem_gen_0.v ../../../../IPFFT2.srcs/sources_1/ip/fifo_generator_0/sim/fifo_generator_0.v

# -- Skipping module bmg_rom

# -- Skipping module bmg_ram

# -- Skipping module xfft_1

# -- Skipping module xfft_1_xfft_v9_1_1

# -- Compiling module glbl

# -- Skipping module blk_mem_gen_1

# -- Skipping module blk_mem_gen_0

# -- Skipping module fifo_generator_0

#

# Top level modules:

# bmg_rom

# bmg_ram

# xfft_1

# glbl

# blk_mem_gen_1

# blk_mem_gen_0

# fifo_generator_0

# End time: 18:47:21 on Apr 08,2022, Elapsed time: 0:00:01

# Errors: 0, Warnings: 1

# ** Warning: (vcom-159) Mode option -64 is not supported in this context and will be ignored.

# Model Technology ModelSim DE-64 vcom 10.6c Compiler 2017.07 Jul 26 2017

# Start time: 18:47:21 on Apr 08,2022

# vcom -64 -93 -work xil_defaultlib ../../../../IPFFT2.srcs/sources_1/ip/xfft_0/sim/xfft_0.vhd

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Loading package NUMERIC_STD

# -- Compiling entity xfft_0

# -- Compiling architecture xfft_0_arch of xfft_0

# End time: 18:47:21 on Apr 08,2022, Elapsed time: 0:00:00

# Errors: 0, Warnings: 1

# ** Warning: (vlog-159) Mode option -64 is not supported in this context and will be ignored.

# Model Technology ModelSim DE-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

# Start time: 18:47:21 on Apr 08,2022

# vlog -64 -incr -work xil_defaultlib ../../../../IPFFT2.srcs/sources_1/new/fifo_rd.v ../../../../IPFFT2.srcs/sources_1/new/fifo_wr.v ../../../../IPFFT2.srcs/sources_1/new/ip_fft.v ../../../../IPFFT2.srcs/sources_1/new/ip_fft2.v ../../../../IPFFT2.srcs/sources_1/new/ip_fifo.v ../../../../IPFFT2.srcs/sources_1/new/ip_ram.v ../../../../IPFFT2.srcs/sources_1/new/ip_ram2.v ../../../../IPFFT2.srcs/sources_1/new/top.v ../../../../IPFFT2.srcs/sim_1/new/tb_ip_fft2.v

# -- Skipping module fifo_rd

# -- Skipping module fifo_wr

# -- Skipping module ip_fft

# -- Skipping module ip_fft2

# -- Skipping module ip_fifo

# -- Skipping module ip_ram

# -- Skipping module ip_ram2

# -- Skipping module top

# -- Skipping module tb_ip_fft2

#

# Top level modules:

# tb_ip_fft2

# End time: 18:47:21 on Apr 08,2022, Elapsed time: 0:00:00

# Errors: 0, Warnings: 1

# Model Technology ModelSim DE-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

# Start time: 18:47:21 on Apr 08,2022

# vlog -work xil_defaultlib glbl.v

# -- Compiling module glbl

#

# Top level modules:

# glbl

# End time: 18:47:21 on Apr 08,2022, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

INFO: [USF-ModelSim-69] 'compile' step finished in '3' seconds

INFO: [USF-ModelSim-4] ModelSim::Simulate design

INFO: [USF-ModelSim-69] Executing 'SIMULATE' step in 'F:/MyTest/FPGA/IPFFT2/IPFFT2.sim/sim_1/behav/modelsim'

Program launched (PID=14728)

# ** Warning: (vsim-8683) Uninitialized out port /tb_ip_fft2/u_top/u_ip_fft/u_xfft_0/U0///(0) has no driver.

这个警告的原因应该是我的ip的部分输出端口没有接,所以导致的,没啥影响。

我很多的output都是悬空的,因为用不到

# ** Warning: (vsim-8683) Uninitialized out port /tb_ip_fft2/u_top/u_ip_fft/u_xfft_0/U0/<protected>/<protected>/<protected>(0) has no driver.

# This port will contribute value (U) to the signal network.

# Block Memory Generator module tb_ip_fft2.u_top.u_ip_ram.u_ram.inst.native_mem_module.blk_mem_gen_v8_4_2_inst is using a behavioral model for simulation which will not precisely model memory collision behavior.

使用ram ip产生的提醒,没有实际影响

xil_defaultlib中包含未知模块

很多,有是有有时没有,不知道触发的原因。

原因知道了,是应为我的IP没有综合完整导致的。

Break in file E:/Program_Files/Xilinx/Vivado/2018.3/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

# ** Failure: ERROR:add_1 must be in range [-1,DEPTH-1]

# Time: 160 ns Iteration: 1 Protected: /tb_ip_fft2/u_top/u_fft2_top/u_ip_fft/u_xfft_0/U0/<protected>/<protected>/<protected>/<protected>/<protected>/<protected> File: E:/Program_Files/Xilinx/Vivado/2018.3/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

# Break in file E:/Program_Files/Xilinx/Vivado/2018.3/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

参考链接 Assertion Error in Protected Xilinx Code - How to debug?

看参考链接的时候懵懵懂懂,不知所以然,真正想清楚的时候,才豁然开朗,发现参考链接完全是对的。可能还是因为中英文表述的原因,没有读懂。

本质上,查一下自己的复位信号,复位信号出问题了

我也是在读波形的时候找到的,rst_n同时接了输入信号和输出信号。导致rst_n在输入信号拉高时,被输出信号拉成高阻态。

很遗憾的是,这种问题没有语法报错,只能自己找具体的那个地方。

大家如果有知道的,还望不吝赐教!

都看到这儿了,点个赞呗

||

\/

2248

2248

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?