在进行FPGA调试的过程中,进行行为仿真,能观察设计的逻辑是否正确,通常情况下需要进行run all的运行,这样才能看到信号在运行过程中的状态,

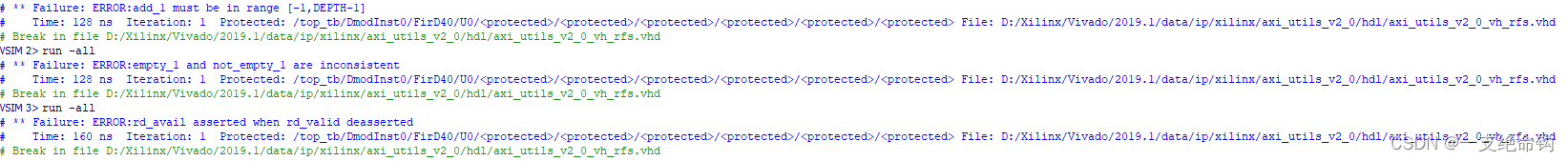

在调试的过程中遇到如下的报错:

# ** Failure: ERROR:add_1 must be in range [-1,DEPTH-1]

# Time: 128 ns Iteration: 1 Protected: /top_tb/DmodInst0/FirD40/U0/<protected>/<protected>/<protected>/<protected>/<protected>/<protected> File: D:/Xilinx/Vivado/2019.1/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

# Break in file D:/Xilinx/Vivado/2019.1/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

run -all

# ** Failure: ERROR:empty_1 and not_empty_1 are inconsistent

# Time: 128 ns Iteration: 1 Protected: /top_tb/DmodInst0/FirD40/U0/<protected>/<protected>/<protected>/<protected>/<protected>/<protected> File: D:/Xilinx/Vivado/2019.1/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

# Break in file D:/Xilinx/Vivado/2019.1/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

run -all

# ** Failure: ERROR:rd_avail asserted when rd_valid deasserted

# Time: 160 ns Iteration: 1 Protected: /top_tb/DmodInst0/FirD40/U0/<protected>/<protected>/<protected>/<protected>/<protected>/<protected> File: D:/Xilinx/Vivado/2019.1/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

# Break in file D:/Xilinx/Vivado/2019.1/data/ip/xilinx/axi_utils_v2_0/hdl/axi_utils_v2_0_vh_rfs.vhd

用的是vivado 2019.1联合modelism 10.7进行的仿真过程,用vivado内置的仿真也是同样的报错信息,建议用modelsim进行仿真,速度快。

因为存在报错,所以仿真程序是不能连续运行的。如何解决这个报错,让程序连续运行?

如下为解决这个问题的思路:

1.从打印的报错信息来看,这个错误的字段是add_1和empty_1和rd_avail的错误,但是实际上自己编写的Verilog代码是没有这个变量的,所以这个应该是其他内部的错误。

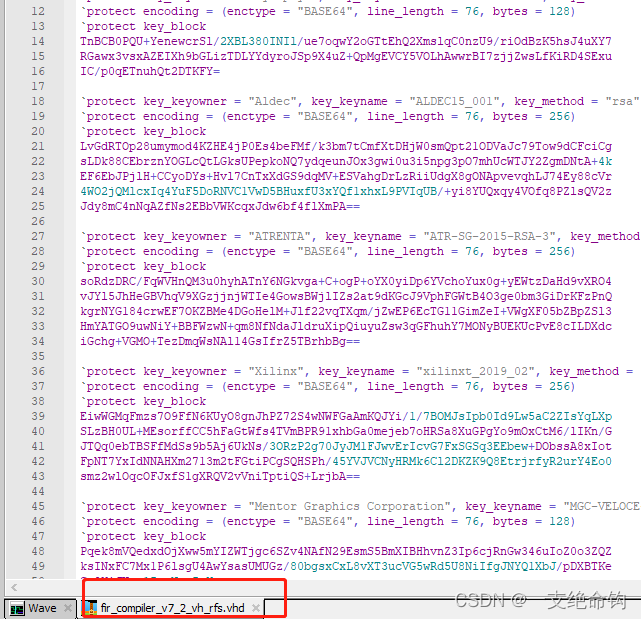

2.判断是哪个内部的错误,基本上可以判断是调用的IP核的内部报错,但是如何判断是哪个IP核使用过程中引起的呢,在利用vivado内部的仿真工具是是无法看到其他信息的,但是在利用modeisim仿真的时候,可以看到程序停止时,停在了打开的fir_complier_v7_2_vh_rfs_vhd,在这里判断应该是调用的Fir的IP核引起的错误。

3.定位了IP核,因为每个人使用IP核的习惯可能不同,所以最直观有效的办法是把用的fir的IP核都注释掉,让程序运行,看是否还存在该报错信息。通过自己的测试,注释掉之后确实可以,接下来对IP核的使用过程重新例化。

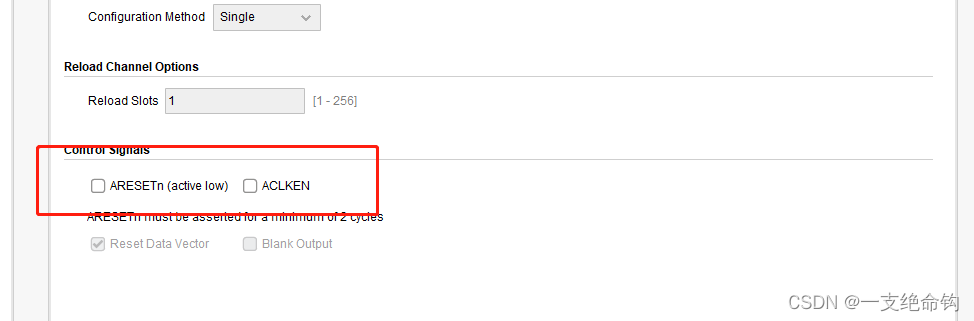

4.在不使用如下的ARESET和ACLKEN时,共有六个接口,可以逐一排查,

FirR your_instance_name (

.aclk(aclk), // input wire aclk

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.s_axis_data_tdata(s_axis_data_tdata), // input wire [31 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata) // output wire [63 : 0] m_axis_data_tdata

);

在排查的时候重点是s_axis_data_tvalid和s_axis_data_tready,这个两个信号一个输入,一个输出,这个是可以利用输出与其他信号做逻辑运算然后给到输入的,重点是在初始化的时候保证s_axis_data_tvalid要有效,因为本人在例化的时候没有采用aclken接口,而且没有注意输入信号的初始状态,导致s_axis_data_tvalid信号在开始时存在一段不确定状态,为X,导致了上述的报错内容。

5.把信号的初始状态搞定,不让存在X即解决了该错误,最终程序能够run all,不报错。

总结:出现这种add_1等的内部IP核的错误的时候,要有一个清晰的思路,在不确定的时候用控制变量法,一点点增加,然后注意保证IP例化的过程中数据一直有状态,而不是X,这样的思路去解决问题最后应该都能够解决

1299

1299

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?