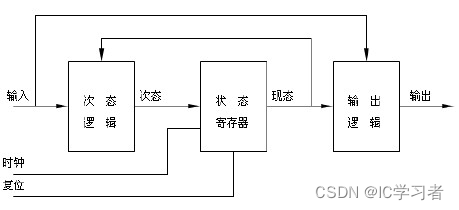

这张图片是mealy型状态机的结构,Moore型类似,输出与输入无关。

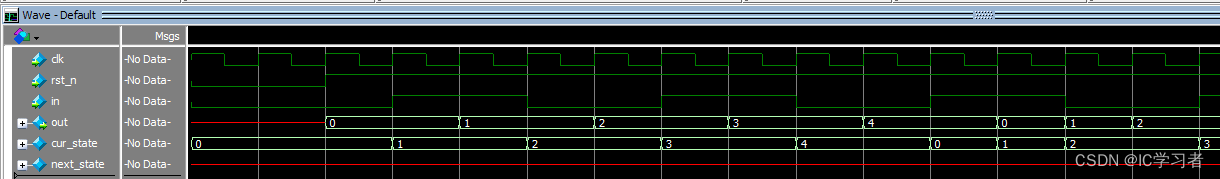

一段式

module moduleName (

input clk,

input rst_n,

input in,

output reg [3:0] out

);

localparam s1=4'd0, s2=4'd1, s3=4'd2, s4=4'd3, s5=4'd4;

reg [3:0] cur_state;

reg [3:0] next_state;

always @(posedge clk) begin

if(!rst_n) begin

cur_state <= s1;

end

else begin

case (cur_state)

s1:begin

if(in)

cur_state <= s2;

out <= cur_state;

end

s2:begin

if(~in)

cur_state <= s3;

out <= cur_state;

end

s3:begin

if(in)

cur_state <= s4;

out <= cur_state;

end

s4:begin

if(~in)

cur_state <= s5;

out <= cur_state;

end

s5:begin

if(in)

cur_state <= s1;

out <= cur_state;

end

default: begin

cur_state <= s1;

out <= cur_state;

end

endcase

end

end

endmodule

如果将输出单独用组合逻辑表示,本质上也是一段式状态机

缺点是,输出比状态晚一个时钟

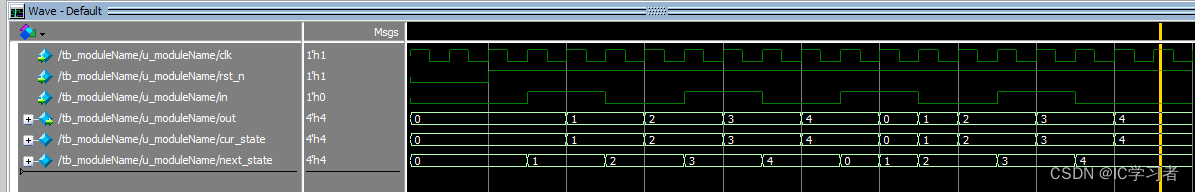

两段式

module moduleName (

input clk,

input rst_n,

input in,

output reg [3:0] out

);

localparam s1=4'd0, s2=4'd1, s3=4'd2, s4=4'd3, s5=4'd4;

reg [3:0] cur_state;

reg [3:0] next_state;

// ========================================

// 二段式

// ========================================

always @(posedge clk) begin

if(!rst_n) begin

cur_state <= s1;

end

else begin

cur_state <= next_state;

end

end

always @(*) begin

case (cur_state)

s1:begin

if(in)

cur_state = s2;

out = cur_state;

end

s2:begin

if(~in)

cur_state = s3;

out = cur_state;

end

s3:begin

if(in)

cur_state = s4;

out = cur_state;

end

s4:begin

if(~in)

cur_state = s5;

out = cur_state;

end

s5:begin

if(in)

cur_state = s1;

out = cur_state;

end

default: begin

cur_state = s1;

out = cur_state;

end

endcase

end

如果将输出单独用组合逻辑表示,本质上也是二段式状态机

输出和状态的时序是一致的

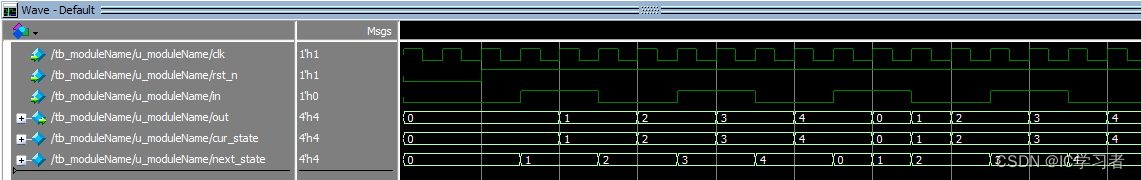

三段式

module moduleName (

input clk,

input rst_n,

input in,

output reg [3:0] out

);

localparam s1=4'd0, s2=4'd1, s3=4'd2, s4=4'd3, s5=4'd4;

reg [3:0] cur_state;

reg [3:0] next_state;

// ========================================

// 三段式

// ========================================

always @(posedge clk) begin

if(!rst_n) begin

cur_state <= s1;

end

else begin

cur_state <= next_state;

end

end

always @(*) begin

case (cur_state)

s1:begin

if(in)

next_state = s2;

end

s2:begin

if(~in)

next_state = s3;

end

s3:begin

if(in)

next_state = s4;

end

s4:begin

if(~in)

next_state = s5;

end

s5:begin

if(in)

next_state = s1;

end

default: begin

next_state = s1;

end

endcase

end

`ifdef SEQUENTIAL_LOGIC

always @(posedge clk) begin

if(!rst_n) begin

out <= 4'd0;

end

else begin

case (next_state)

s1:begin

out <= s1;

end

s2:begin

out <= s2;

end

s3:begin

out <= s3;

end

s4:begin

out <= s4;

end

s5:begin

out <= s5;

end

default: begin

out <= s1;

end

endcase

end

end

`else

always @(*) begin

if(!rst_n) begin

out <= 4'd0;

end

else begin

case (cur_state)

s1:begin

out <= s1;

end

s2:begin

out <= s2;

end

s3:begin

out <= s3;

end

s4:begin

out <= s4;

end

s5:begin

out <= s5;

end

default: begin

out <= s1;

end

endcase

end

end

`endif

都看到这儿了,点个赞呗

||

\/

3058

3058

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?