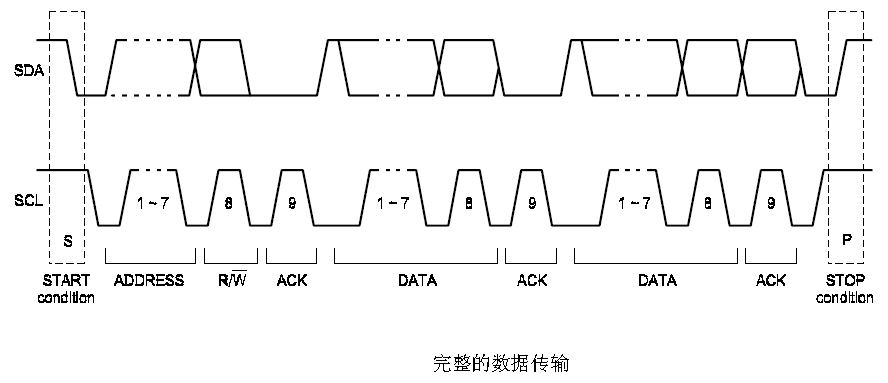

I2C总线信号时序总结

总线空闲状态

I2C总线总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

启动信号

在时钟线SCL保持高电平期间,数据线SDA上的电平被拉低(即负跳变),定义为I2C总线总线的启动信号,它标志着一次数据传输的开始。启动信号是一种电平跳变时序信号,而不是一个电平信号。启动信号是由主控器主动建立的,在建立该信号之前I2C总线必须处于空闲状态。

重启动信号

在主控器控制总线期间完成了一次数据通信(发送或接收)之后,如果想继续占用总线再进行一次数据通信(发送或接收),而又不释放总线,就需要利用重启动Sr信号时序。重启动信号Sr既作为前一次数据传输的结束,又作为后一次数据传输的开始。利用重启动信号的优点是,在前后两次通信之间主控器不需要释放总线,这样就不会丢失总线的控制权,即不让其他主器件节点抢占总线。

重启动信号

在主控器控制总线期间完成了一次数据通信(发送或接收)之后,如果想继续占用总线再进行一次数据通信(发送或接收),而又不释放总线,就需要利用重启动Sr信号时序。重启动信号Sr既作为前一次数据传输的结束,又作为后一次数据传输的开始。利用重启动信号的优点是,在前后两次通信之间主控器不需要释放总线,这样就不会丢失总线的控制权,即不让其他主器件节点抢占总线。

停止信号

在时钟线SCL保持高电平期间,数据线SDA被释放,使得SDA返回高电平(即正跳变),称为I2C总线的停止信号,它标志着一次数据传输的终止。停止信号也是一种电平跳变时序信号,而不是一个电平信号,停止信号也是由主控器主动建立的,建立该信号之后,I2C总线将返回空闲状态。

本文详细介绍了I2C总线的信号时序,包括启动信号、重启动信号、停止信号的产生及其作用。在数据传输过程中,每个信号位与时钟脉冲同步,接收器通过应答信号ACK/NACK反馈接收状态。文中还讨论了总线竞争的仲裁机制,确保了多主控设备间的数据传输可靠性。此外,还提到了总线封锁状态和时钟信号的同步原理。

本文详细介绍了I2C总线的信号时序,包括启动信号、重启动信号、停止信号的产生及其作用。在数据传输过程中,每个信号位与时钟脉冲同步,接收器通过应答信号ACK/NACK反馈接收状态。文中还讨论了总线竞争的仲裁机制,确保了多主控设备间的数据传输可靠性。此外,还提到了总线封锁状态和时钟信号的同步原理。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2998

2998

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?