verilog实现乘法器

两个N位二进制数x、y的乘积用简单的方法计算就是利用移位操作来实现。

以下介绍两种实现乘法器的方法:串行乘法器和流水线乘法器。

两个N位二进制数x、y的乘积用简单的方法计算就是利用移位操作来实现。

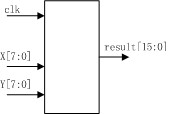

其框图如下:

其状态图如下:

其实现的代码如下:

modulemulti_CX(clk, x, y, result); |

02 |

|

03 |

inputclk; |

04 |

input[7:0] x, y; |

05 |

output[15:0] result; |

06 |

07 |

reg[15:0] result; |

08 |

09 |

parameters0 = 0, s1 = 1, s2 = 2; |

10 |

|

本文介绍了两种Verilog实现乘法器的方法:串行乘法器和流水线乘法器。串行乘法器资源占用最少,适合低速应用;流水线乘法器通过多级流水线提高速度,适用于非高速信号处理。文中给出了8位乘法器的流水线实现代码,并指出高速乘法常利用FPGA的DSP单元。

本文介绍了两种Verilog实现乘法器的方法:串行乘法器和流水线乘法器。串行乘法器资源占用最少,适合低速应用;流水线乘法器通过多级流水线提高速度,适用于非高速信号处理。文中给出了8位乘法器的流水线实现代码,并指出高速乘法常利用FPGA的DSP单元。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2160

2160

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?