一种乘法器的设计。

一、乘法器概述

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。

乘法器是模拟式电子式电能表的重要组成部分,也是电能表计量误差的最主要来源。对时分割乘法器在谐波条件下的计量误差进行了定量的研究与分析,根据时分割乘法器的工作原理,推导其在谐波条件下计量误差的理论表达式,并通过仿真计算验证计量误差量化表达式的准确性。从计量准确性和成本角度综合比较了时分割乘法器电能表与数字式电子式电能表。对谐波电能计量的合理性进行探讨。为定量化分析谐波条件下计量系统的误差提供了理论依据,对适用于谐波条件下计量的电子式电能表的设计具有参考价值。

乘法器可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器有多种类型,这里讨论的是硬件乘法器,其核心基础就是加法器结构。乘法器的模型就是基于“移位和相加”的算法,在该算法中,乘法器中每一个比特位都会产生一个局部乘积。第一个局部乘积由乘法器的LSB产生,第二个乘积由乘法器的第二位产生,以此类推。如果相应的乘数比特位是1,那么局部乘积就是被乘数的值,如果相应的乘数比特位是0,那么局部乘积全为0。每次局部乘积都向左移动一位。乘法器可以用更普遍的方式来表示。每个输入,局部乘积数,以及结果都被赋予了一个逻辑名称(如A1、A2、B1、B2),而这些名称在电路原理图中就作为了信号名称。在原理图的乘法例子中比较信号名称,就可以找到乘法电路的行为特性。

在乘法器电路中,乘数中的每一位都要和被乘数的每一位相与,并产生其相应的乘积位。这些局部乘积要馈入到全加器的阵列中(合适的时候也可以用半加器),同时加法器向左移位并表示出乘法结果。最后得到的乘积项在CLA电路中相加。注意,某些全加器电路会将信号带入到进位输入端(用于替代邻近位的进位)。这就是一种全加器电路的应用:全加器将其输入端的任何三个比特相加。随着乘数和被乘数位数的增加,乘法器电路中的加法器位数也要相应的增加。通过研究CLA电路的特性,也可以在乘法器中开发出更快的加法阵列。

二、代码实现

代码实现:

module multiplier #(parameter N=8)(

input clk,

input rst_n,

input [N-1:0] ain,bin,

output reg [2*N-1:0] dout

);

integer i;

reg [2*N-1:0] a;

reg [2*N-1:0] b;

assign a = ain;

assign b = bin;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

dout <= 0;

end

end

always@(*)begin

dout = 0;

for(i=0;i<N;i=i+1)begin

if(b[i])begin

dout = dout + (a << i);

end

else begin

dout = dout;

end

end

end

endmodule采用参数化定义,注意乘数和结果的位宽定义。定义足够位宽的中间变量,将输入的两个乘数赋值给中间变量,进行移位相加操作。

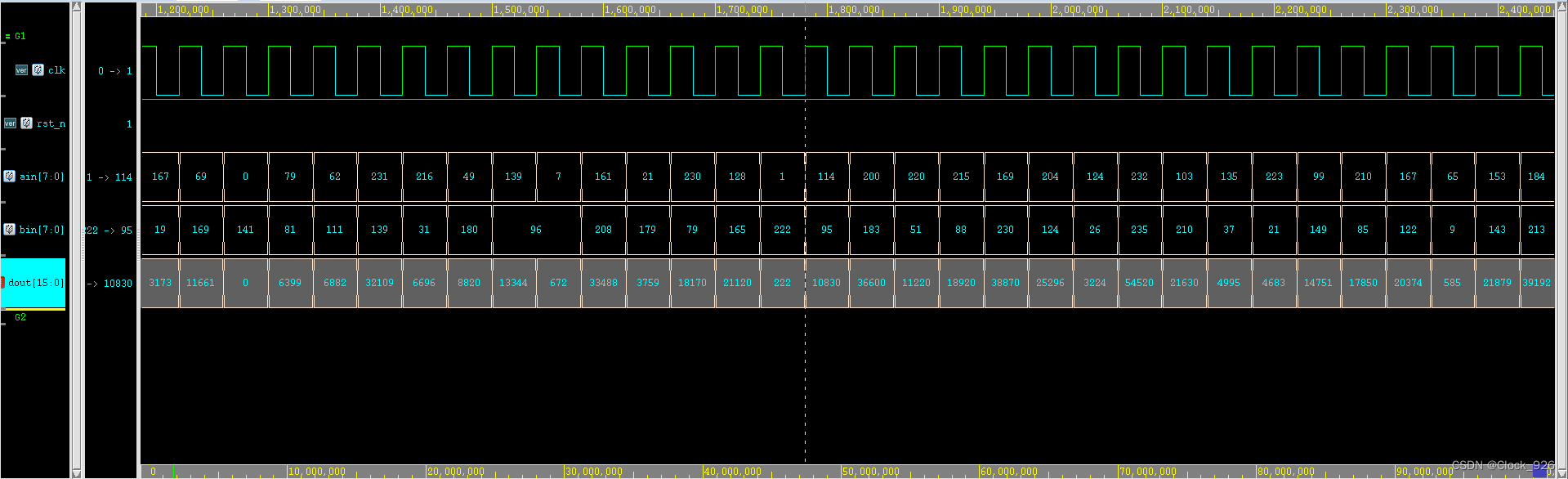

测试波形:

为了观察结果更加直观采用的是十进制显示。

文章介绍了乘法器的基本概念及其在电子式电能表中的应用,特别是在谐波条件下的计量误差分析。乘法器通过‘移位和相加’算法工作,由加法器组成,文中给出了一个8位乘法器的Verilog代码实现,展示了如何进行移位相加操作来完成两个二进制数的乘法。

文章介绍了乘法器的基本概念及其在电子式电能表中的应用,特别是在谐波条件下的计量误差分析。乘法器通过‘移位和相加’算法工作,由加法器组成,文中给出了一个8位乘法器的Verilog代码实现,展示了如何进行移位相加操作来完成两个二进制数的乘法。

7206

7206

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?