1. 简介

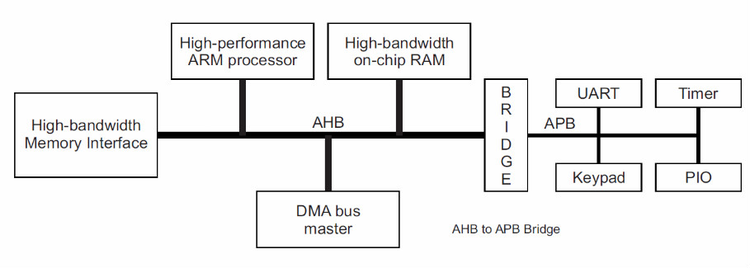

AHB总线规范是AMBA总线规范的一部分,AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。APB用于连接外部设备,对性能要求不高,而考虑低功耗问题。ASB是AHB的一种替代方案。1.1 AHB总线的架构

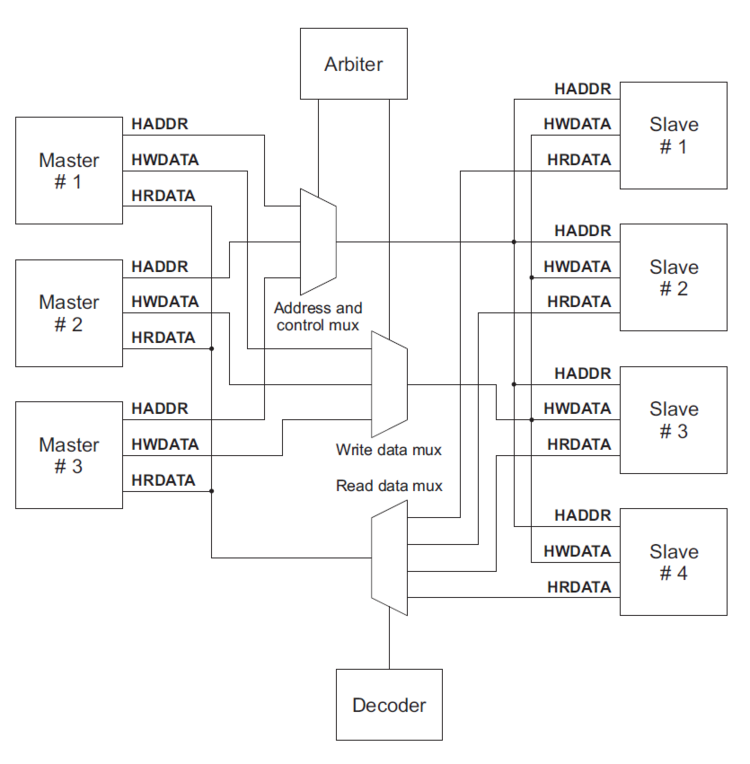

AHB总线的强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线master、各种拥有AHB接口的控制器等等连接起来构成一个独立的完整的SOC系统,不仅如此,还可以通过AHB-APB桥来连接APB总线系统。AHB可以成为一个完整独立的SOC芯片的骨架。下图是一个典型的AHB系统总线的结构示意图

1.2 AHB基本特性

- Burst传输

- Split事务处理

- 单周期master移交

- 单一时钟沿操作

- 无三态

- 更宽的数据总线配置(64/128)

- 流水线操作

- 可支持多个总线主设备(最多16个)

2. AHB总线的组成

AHB总线由Master、Slave和Infrastructure构成。Infrastructure由arbiter、数据多路、地址控制多路、译码器构成。

某一时刻只允许一个主设备使用总线

通过地址映射来选择使用哪一个从设备

读数据总线(HRDATA)

地址控制总线(HADDR)

- 主设备Master

某一时刻只允许一个主设备使用总线

- 从设备Slave

通过地址映射来选择使用哪一个从设备

- 仲裁器arbiter

- 译码器decoder

- 总线可以分为三组

读数据总线(HRDATA)

地址控制总线(HADDR)

3. 信号描述

| Name | Source | To | Description |

| HCLK | clock source | 各module | 总线时钟,上升沿采样 |

| HRESETn | reset controller | 各module | 总线复位,低电平有效 |

| HADDR[31:0] | Master | decoder mux to slave arbiter |

32位系统地址总线 |

| HTRANS[1:0] | Master | mux to slave | 当前传输类型NONSEQ, SEQ, IDLE, BUSY |

| HWRITE | Master | mux to slave | 1为写,0为读 |

| HSIZE[2:0] | Master | mux to slave | 每一个transfer传输的数据大小,以字节为单位,最高支持1024位 |

| HBURST[2:0] | Master | mux to slave | burst类型,支持4、8、16 burst,incrementing/wrapping |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?