1 FIFO原理

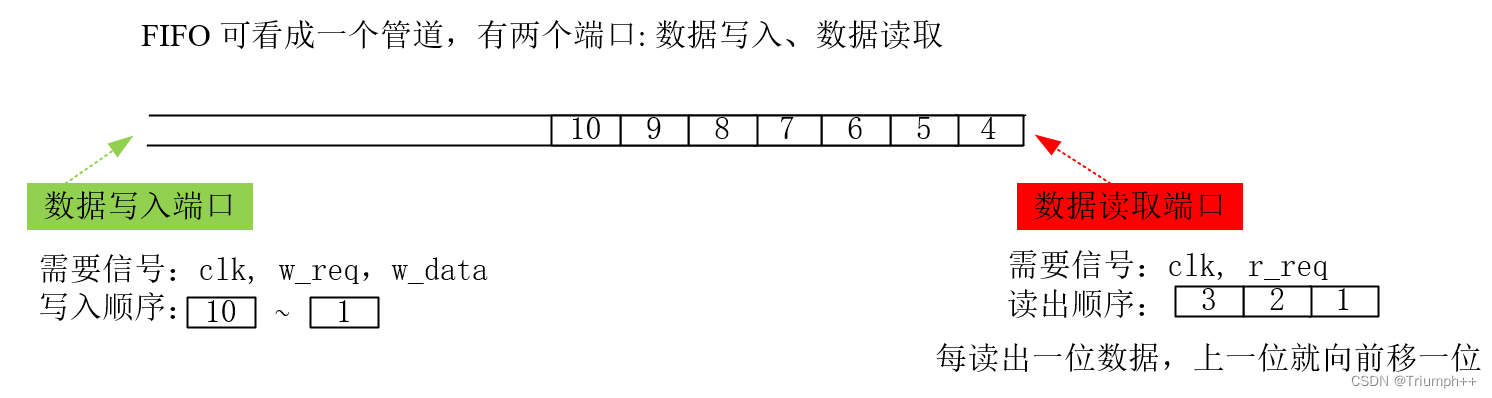

FIFO(First In First Out,即先入先出),是一种数据缓冲器。先被写入的数据会按顺序先被读出。FIFO可看做一个管道,有数据写入端口和 数据读取端口:

如图,数据写入端口从1~10依次写入数据,则数据读取端口也从1~10依次读取数据。输出端口每读出一位数据,FIFO中的后一位数据就向前移一位。如读取端口读出1、2、3后FIFO输出端口的第一位变为4。

1.1 FIFO的使用

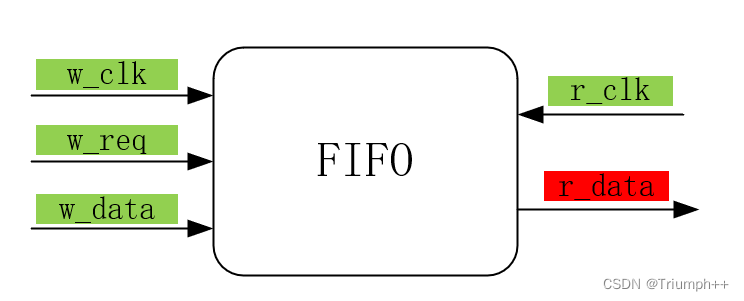

写数据端口:

- w_clk : 写数据时钟信号

- w_req : 写请求信号

- w_data : 要写入的数据

读数据端口:

- r_clk : 读数据时钟信号

- r_data : 读出的数据

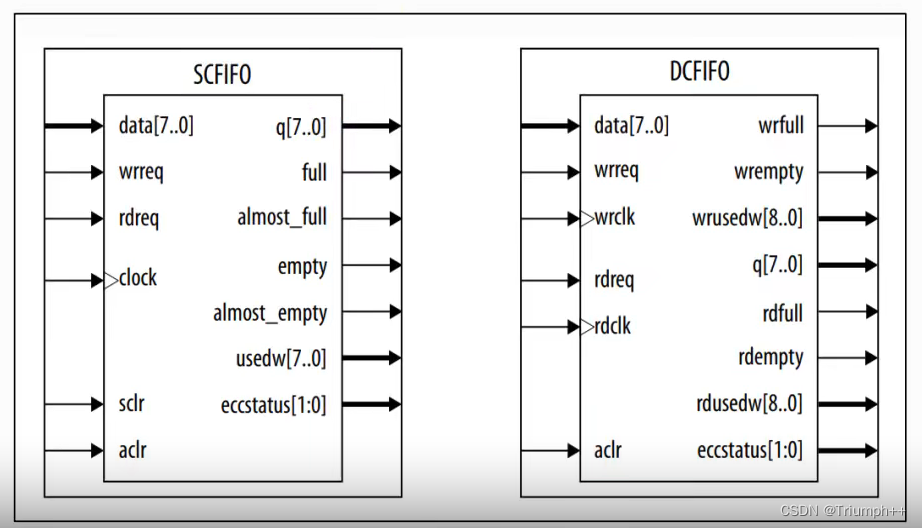

1.2 FIFO的分类

- SCFIFO (同步FIFO) : w_clk 和 r_clk 一致

- DCFIFO (同步FIFO) : w_clk 和 r_clk 不一致

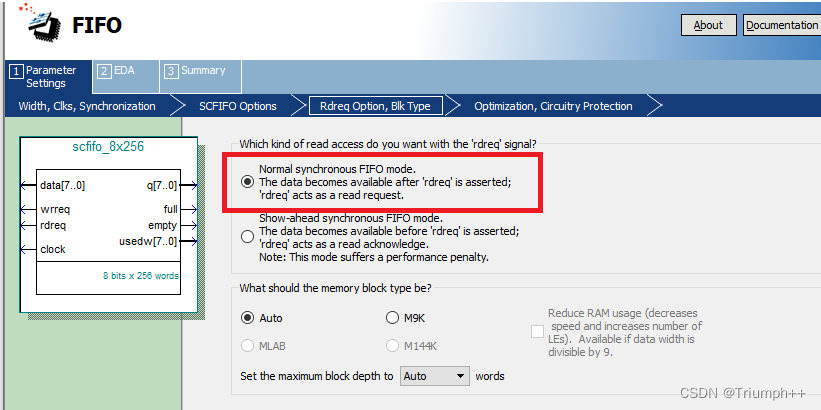

1.3 读取数据的模式

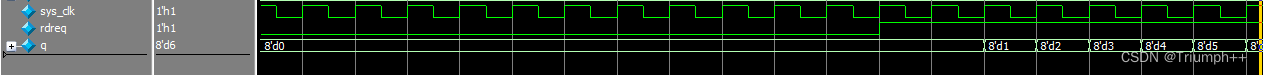

(1) 普通同步FIFO模式

设置:

读取数据波形:

数据输出q滞后读请求信号rdreq一个时钟周期!

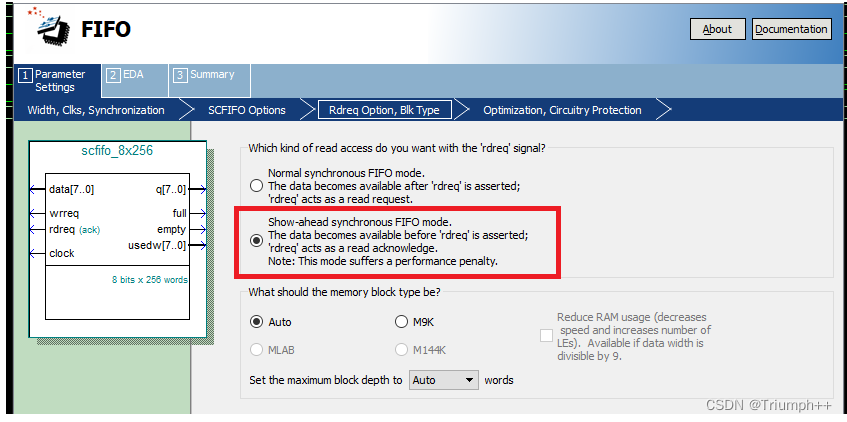

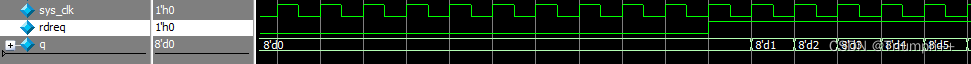

(2) 先出数据FIFO模式

设置:

读取数据波形:

rdreq有效立即输出信号,rdreq信号与数据输出q同步!

2 FIFO的应用

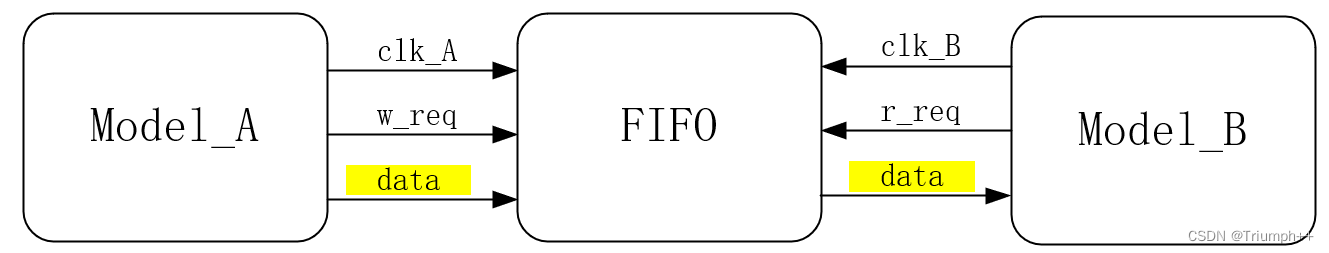

2.1 多bit数据做跨时钟域转换

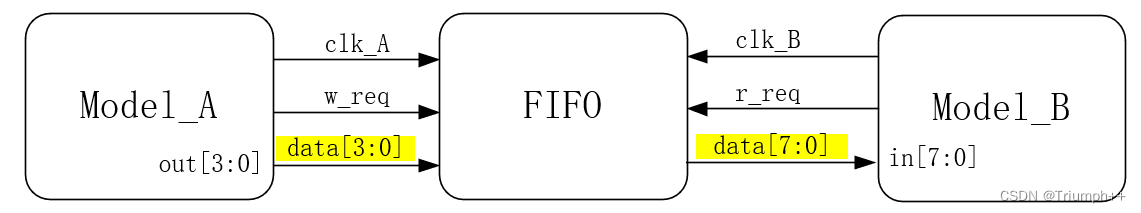

当两个模块的时钟不一致,它们之间需要进行数据传输时。(如A模块的数据需要传输到B模块进行处理),此时就需要做跨时钟域处理。先把模块A的数据按照clk_A写入FIFO,然后模块B再按clk_B读取FIFO中的数据,因此数据data在模块B中就能得到正确的处理!

2.2 带宽同步

当两个模块的数据传输端口带宽不一致,其它们之间需要进行数据传输时。此时就需要做带宽同步处理。 先把模块A的数据按照clk_A写入FIFO(设模块A输出的数据位宽为4,此时也把FIFO的数据写入端口位宽设置为4),然后模块B再按clk_B读取FIFO中的数据(设模块B输入的数据位宽为8,此时也把FIFO的数据读取端口位宽设置为8),从而实现了带宽同步。

此时数据拼接的方式为:

即两个数据位宽为 4 的数据拼接为 一个数据位宽为8的数据,先输入的为高4位,后一位为低4位!

本文详细介绍了FIFO的工作原理,包括同步与异步FIFO的区别,以及它们在跨时钟域转换和带宽同步中的关键作用。通过实例展示了如何配置和解读数据波形,探讨了FIFO在多比特数据处理和不同模块间高效通信中的实用策略。

本文详细介绍了FIFO的工作原理,包括同步与异步FIFO的区别,以及它们在跨时钟域转换和带宽同步中的关键作用。通过实例展示了如何配置和解读数据波形,探讨了FIFO在多比特数据处理和不同模块间高效通信中的实用策略。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?