STM32f103系列有3个ADC:ADC1,ADC2,ADC3

通道:ADC1和ADC2都有16个外部通道,2个内部通道:连接到温度传感器和内部参考电压(VREFINT = 1.2V)

ADC3有8个外部通道

通道列表:

通道顺序转换:使用多个通道涉及到先后顺序,因为规则转换通道只有一个数据寄存器。

规则通道的转换顺序:由三个寄存器控制:SQR1、SQR2、SQR3

注入通道的转换顺序:寄存器:JSQR

DMA功能:仅ADC1有

规则通道:是最常用的通道,ADC转换都是用规则通道实现的。

注入通道:相对于规则通道,可以在规则通道转换时,强行插入转换,相当于一个“中断通道”。当有注入通道需要转换时,规则通道的转换会停止,优先执行注入通道的转换,当注入通道的转换执行完毕后,再回到之前规则通道进行转换。

精度:为12位,2^12=4096,各通道的A/D转换可以单次、连续、扫描或间断执行,转换结果可以左对齐或右对齐储存在16位数据寄存器中。

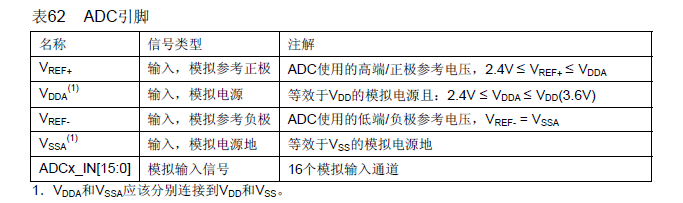

输入(测量)的电压范围:VREF- ≤ VIN ≤ VREF+,把 VSSA 和 VREF-接地,把 VREF+和 VDDA 接 3V3,得到ADC 的输入电压范围为: 0~3.3V。

VDD是3.3V,VSS接地,相对应的,VDDA是3.3V,VSSA也接地,模拟输入信号不要超过VDD(3.3V)。

触发源:(后面代码中有详细说明)通过内部定时器、 外部IO触发转换

配置寄存器触发:寄存器CR2的ADON位,写1时开始转换,写0时停止转换。程序运行过程中调用库函数,操作CR2寄存器的ADON位置。

转换速度:ADC的时钟(ADCCLK)最大14MHz,由PCLK2分频产生(2、4、6、8分频)。

- SYSCLK 系统时钟,最大72MHz

- HCLK :AHB总线时钟,由系统时钟SYSCLK 分频得到,一般不分频,等于系统时钟。(可以是 2/4/6/8 分频)

- PCLK1与PCLK2时钟:经过总线桥AHB--APB,通过设置分频,由HCLK得到。

- PCLK2时钟最高可达72MHz,PCLK1最大36MHz。PCLK2对应APB2外设。PCLK1对应APB1外设。

- ADCCLK对应PCLK2,可以为72MHz,或56MHz

- 转换时间:看手册可知 STM32F103xx增强型产品:ADC时钟为56MHz时为1μs,为72MHz时是1.17μs

计算公式:T=(ADC_SampleTime_xxCyclesx+12.5)×时钟周期

说明ÿ

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5426

5426

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?