新思的一系列小外设如I2C,SPI都采用了相似的微架构,即寄存器模块,TX/RX FIFO,移位逻辑模块,TX/RX状态机等。如下图所示。

APB的总线作为配置寄存器和处理中断的总线接口。与CSR直接相接,同时还可以hardcore是否让core和CSR采用相同的时钟(同步设计),不同的时钟域(异步设计)。

IP整体的数据流为:

1. 作为master,通过写寄存器(等效于向TX FIFO中写数据),硬件逻辑检测到TX FIFO中存在数据之后发送一个start bit到txd上,之后不断向TX FIFO中写数据,进行连续的传输。在TX FIFO中的entry传送完毕之后,TX FIFO发送empty信号,同时硬件逻辑会据此生成一个stop bit。完成一笔数据的传输。

2. 作为slave,slave不断检测serial bus上面的信号,检测到bus上的数据和IP内部寄存器中存储的地址相同,根据读写位的情况判断接收数据或发送数据。

连接性:

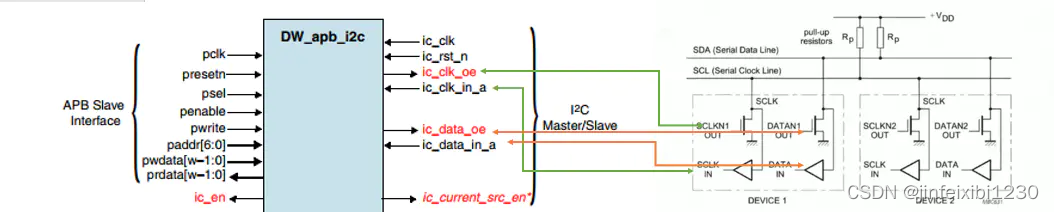

参考上图,dw_apb_i2c既有master模式也有slave模式,因此在IP的端口上可以看到输入和输出的时钟信号和数据信号。

I2C是服务于片间的通信,时钟信号和数据信号需要先传递给芯片的IO,之后再传到片外的SCL和SDA线上。多个I2C挂在同样的SCL和SDA上面,就实现了多个I2C之间的传输。

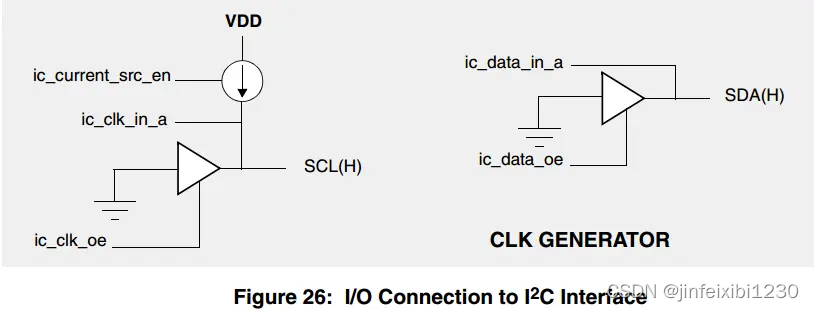

需要注意的是,I2C用的IO,一般是I2C专用的IO,当然条件有限的时候也可以GPIO的cell去替代。这种IO连接的特点是由芯片向片外方向的端口接地,ic_clk输出接oe,可以理解为enable端。片外输入的ic_clk_in接片外向芯片方向的端口。这样接的作用是当ic_clk_oe为高时,芯片向外输出低电平,当ic_clk_oe为低时,SCL通过ic_clk_in_a端口传到芯片内,检测这个信号可以检测此时serial bus处于什么状态。

2291

2291

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?