计算机寄存器实验

| 1.基本要求 理解CPU运算器中寄存器的作用;设计并验证寄存器组(不少于四个寄存器);利用寄存器或组合逻辑电路实现移位运算功能(至少含左移、右移、循环左移、循环右移四种运算功能); 2.扩展要求 实现更多的寄存器;实现多总线结构寄存器访问; 3.思考要求 思考随着寄存器的增多,电路设计的复杂度是什么比例增大。 | |||

| 二.理论分析或算法分析(文字描述以及算法流程图,包括基本与扩展要求的分析与设计思路描述) 基本与扩展要求的分析与设计思路描述: 计算机寄存器是计算机中的重要组成部分,它们用于存储计算机指令和数据,以及提供给CPU运算器进行运算。为了实现基本要求,我需要首先理解CPU运算器中寄存器的作用,然后设计并验证寄存器组,并利用寄存器或组合逻辑电路实现移位运算功能,包括左移、右移、循环左移和循环右移四种运算功能。 对于扩展要求,我可以实现更多的寄存器,以及多总线结构寄存器访问。通过增加寄存器数量和访问方式,可以提高计算机的性能和效率。但同时,随着寄存器的增多,电路设计的复杂度也会相应增加。 | |||

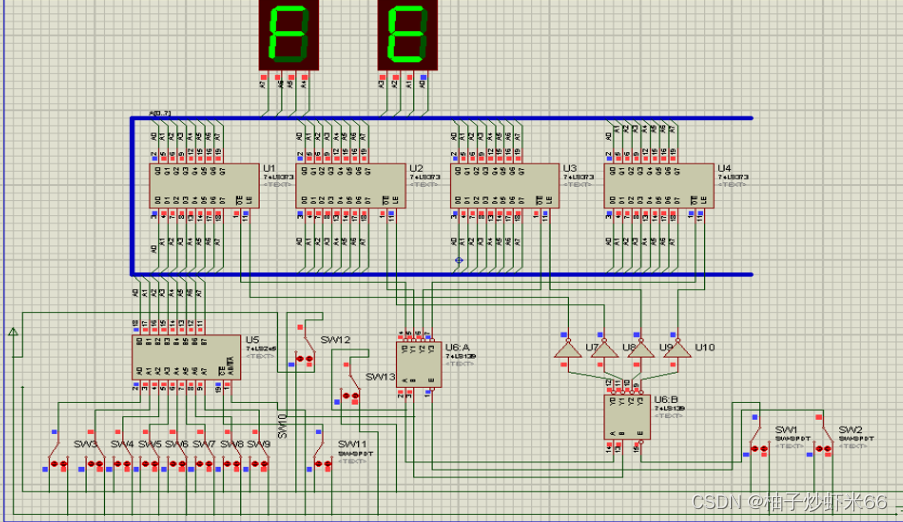

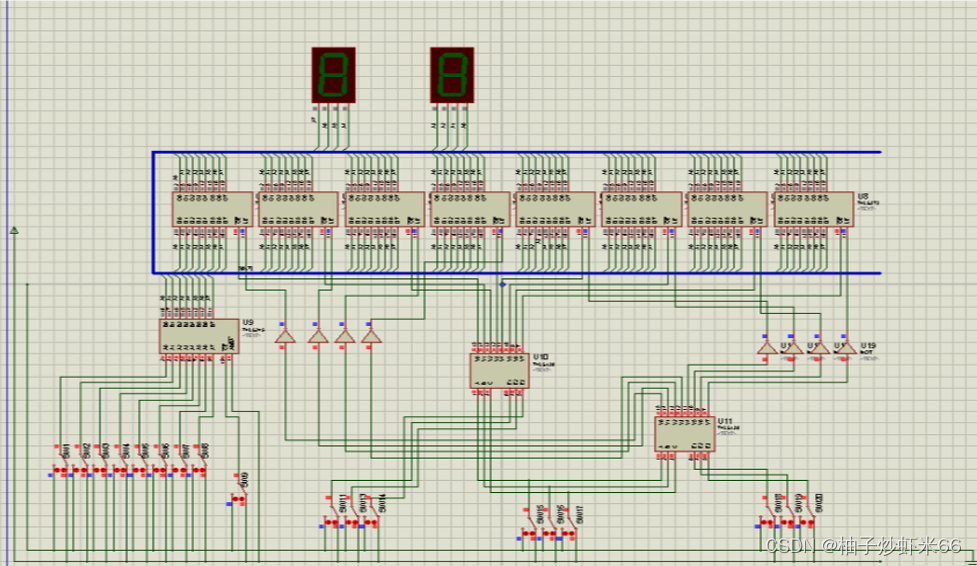

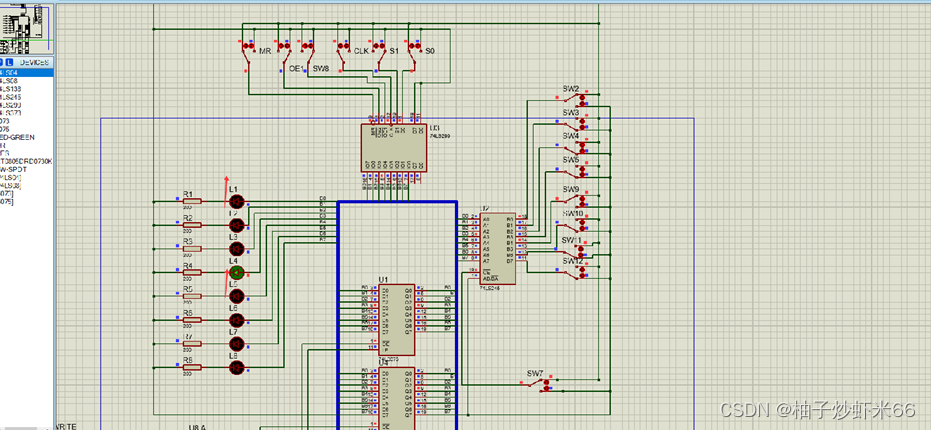

| 三.实现方法(含实现思路、程序流程图、实验电路图和源程序列表等) 1.实现思路: 设计并验证寄存器组,包括至少四个寄存器; 利用寄存器或组合逻辑电路实现移位运算功能,包括左移、右移、循环左移和循环右移四种运算功能; 实现更多的寄存器,以及多总线结构寄存器访问; 在Proteus软件中,实现寄存器的电路布局和连接,对电路进行仿真测试。 2.涉及知识点: CPU运算器中寄存器的作用; 寄存器的设计和验证; 移位运算的电路实现方式; Proteus软件的使用方法。 3.实现过程的介绍: 设计并验证寄存器组,包括至少四个寄存器,通过Proteus软件的仿真测试,验证寄存器的功能和性能; 利用寄存器或组合逻辑电路实现移位运算功能,包括左移、右移、循环左移和循环右移四种运算功能; 实现更多的寄存器,以及多总线结构寄存器访问,进一步提高计算机的性能和效率; 在Proteus软件中,实现寄存器的电路布局和连接,包括寄存器、多总线结构以及移位电路; 对寄存器进行仿真测试,验证寄存器的功能和性能。 设计并验证寄存器:

扩展要求设计:

| |||

| 四.实验结果分析(含执行结果验证、输出显示信息、图形、调试过程中所遇的问题及处理方法等) 1.执行结果验证: 通过Proteus软件的仿真测试,验证寄存器的功能和性能,包括移位运算和多总线结构访问的效果以及时序准确性。 2.结果分析: 通过实现更多的寄存器和多总线结构访问,我提高了计算机的性能和效率。但同时,随着寄存器数量的增加,电路设计的复杂度也会相应增加。需要在设计时合理考虑寄存器数量和访问方式,以保证电路的正确性和可靠性。 3.调试过程中所遇的问题及处理方法: 在实验过程中,可能会遇到电路连接错误、仿真模型不匹配等问题。需要仔细检查电路连接和仿真设置,排除错误并重新测试。

| |||

| 五.结论(含学习总结、思考问题回答等内容) 结论: 1.成功地设计并验证了寄存器组,包括至少四个寄存器,并利用寄存器或组合逻辑电路实现移位运算功能; 2.实现了更多的寄存器和多总线结构寄存器访问,提高了计算机的性能和效率。 收获: 通过本次实验,我深入理解了计算机寄存器的作用,以及实现移位运算和多总线结构寄存器访问的方法。在实验过程中,我也思考了随着寄存器数量增多,电路设计的复杂度是什么比例增大的问题。通过思考和实践,我对计算机寄存器的优化和性能提升有了更深入的理解。 思考问题: 随着寄存器数量的增多,电路设计的复杂度会呈指数级增长。这是因为寄存器数量增多会导致电路中的组合逻辑电路数量增加,同时也会增加电路中的时序逻辑电路。这将导致电路中的管脚数量增多,需要增加更多的电路板和布线,从而增加了电路的物理体积和成本。此外,电路的稳定性和校准难度也会增加,需要更多的时间和精力来进行测试和维护。因此,在实际设计中,需要根据实际需求来平衡寄存器数量和电路设计的复杂度,以确保电路的性能和可靠性。 |

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?