一、实验目的

理解锁存器、通用寄存器及移位寄存器的组成和功能。理解寄存器的基本原理,学习寄存器的编程和控制,掌握数字电路设计基础,培养实验能力和团队合作精神。

二、实验内容

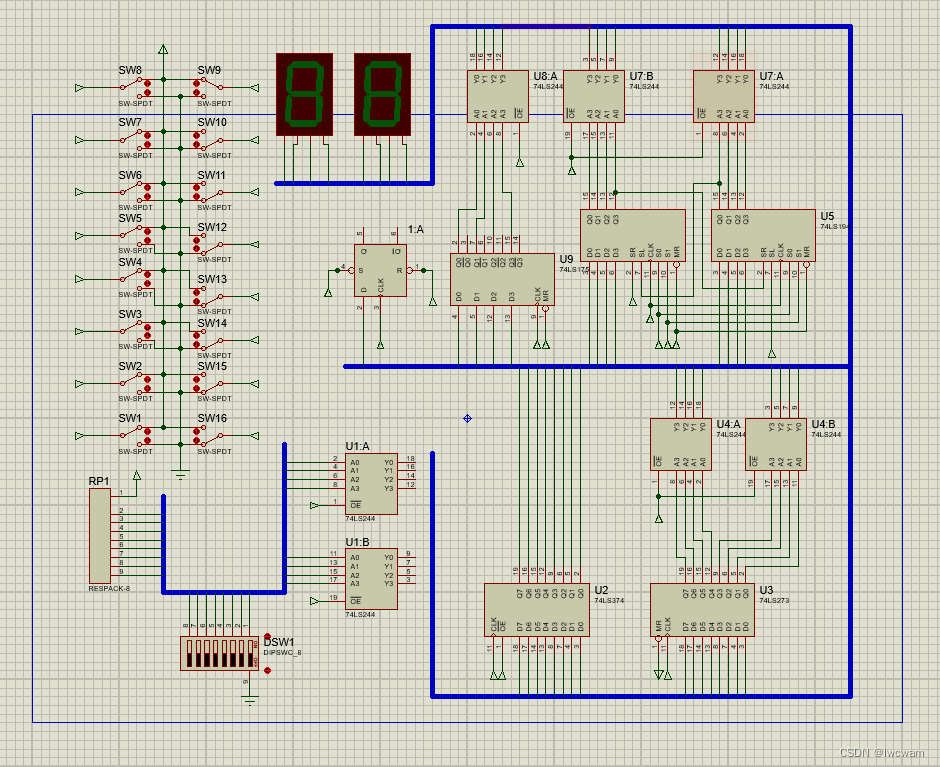

通过拨码开关输入原始数据到某个寄存器;或者从一个寄存器向另一个寄存器赋值。同时,利用移位寄存器实现数据的置数、左移、右移等功能 。

比较以下各组器件之间的异同:触发器 74LS74 和 74LS175;触发器 74LS175 和寄存器 74LS273;寄存器 74LS273 和 74LS374;寄存器 74LS273 和移位寄存器 74LS194。

三、实验器件

1、D 触发器(74LS74、74LS175)、三态缓冲器(74LS244)。

2、寄存器(74LS273、74LS374 )和移位寄存器(74LS194)

四、实验原理

寄存器堆由 D 触发器(74LS74、74LS175)构成的锁存器、通用寄存器 R0(74LS374)和 DR(74LS273)、移位寄存器(74LS194)构成。其中除了 74LS374 器件自带三态门结构外,其余锁存器和寄存器的输出都经过三态门(74LS244)和数据总线 BUS_[0..7]相连,以确保按照信息传输的要求恰当有序的控制锁存器和寄存器的数据输出到总线,任何时刻总线数据都不会发生冲突。

上升沿有效的开关 CLK(74LS74 和 74LS175 共用)、R0_CLK(74LS374 使用)、DR_CLK(74LS273 使用)和 SFT_CLK(74LS194 使用),负责把总线数据打入各自的器件;

低电平有效的开关 OE\(74LS74、74LS175 的三态门控制)、R0_BUS\(74LS374 输出控制)、 DR_BUS\(74LS273 的三态门控制)和 SFT_BUS\(74LS194 的三态门控制),负责各个器件输出所 保存的数据到数据总线。

低电平有效的开关 SET\是 74LS74 的置 1 开关,低电平有效的开关 CLR(\ 74LS74 和 74LS175 共用)、MR\(74LS194 使用)是各个器件相应的清零开关。注意的是:寄存器 74LS374 是没有 清零功能的,74LS273 有置 0 端 MR\,可以设置清零功能。但是,在本实验中 MR\接高电平, 实际上 74LS273 取消了清零功能。

高电平有效的开关 SL、SR、S0、S1 是移位寄存器 74LS194 的专属开关,负责其置数、移位 等功能的设置,具体详细见下文移位寄存器 74LS194 的功能列表。

输入单元

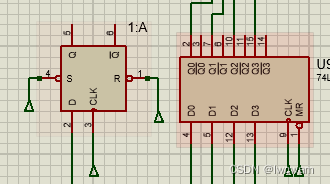

维持-阻塞型 D 触发器:

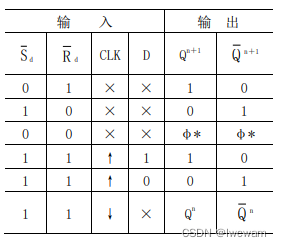

D 触发器逻辑功能如表 Sd 和 Rd 端分别为异步置 1 端和置 0 端,CLK 为时钟脉冲端。CLK 脉冲上升沿触发。触发器的状态只取决于时钟到来前 D 端的状态,其输出状态的更新发生在 CLK 脉冲的上升沿。D 触发器可用作数字信号的寄存,移位寄存,分频和波形发生等。本实验使用的 是单位 D 触发器 74LS74 和四位 D 触发器 74LS175,如图 5-3 所示。74LS175 相当于四个并行的 74LS74 组合,但是省略了置 1 端,保留了置 0 端用以清零。

D触发器

D触发器逻辑功能表

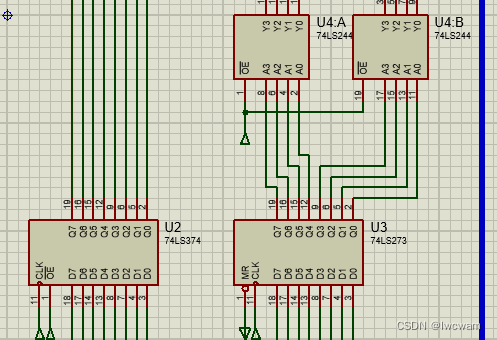

通用寄存器:

本实验中使用了 74LS273 和 74LS374 两款芯片作为通用寄存器,如图 5-5 所示。两者实现的 功能基本相同:D0-D7为并行输入端,Q0-Q7为并行输出端,CLK 端为时钟脉冲(上升沿触发);输 出端 QX的状态只取决于 CLK 端时钟脉冲到来时刻输入端 DX的状态,输出状态的更新发生在 CLK 端脉冲的上升沿。74LS374 自带三态门输出控制结构,比 74LS273 多了一个 OE\端输出使能,相 当于“74LS273 + 74LS244”组合。74LS273 本身没有三态门输出控制,输出端必须经过 74LS244 接到数据总线 BUS。但是,74LS273 比 74LS374 多了一个 MR\端输出清零。

通用寄存器

通用寄存器

五、实验结果

五、实验结果

根据手册完成了本次实验的设计图

在实验过后,又加深了对寄存器的理解。寄存器是CPU内部用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。寄存器是中央处理器内的组成部分。寄存器是有限存储容量的高速存储部件,它们可用来暂存指令、数据和位址。 按照功能的不同,可将寄存器分为基本寄存器和移位寄存器两大类。

基本寄存器只能并行送入数据,也只能并行输出。移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,或串行输入、并行输出,十分灵活,用途也很广。

822

822

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?