文章目录

综述:

使用riffa框架打通PC和fpga之间的PCIE通道很简单,流程如下:

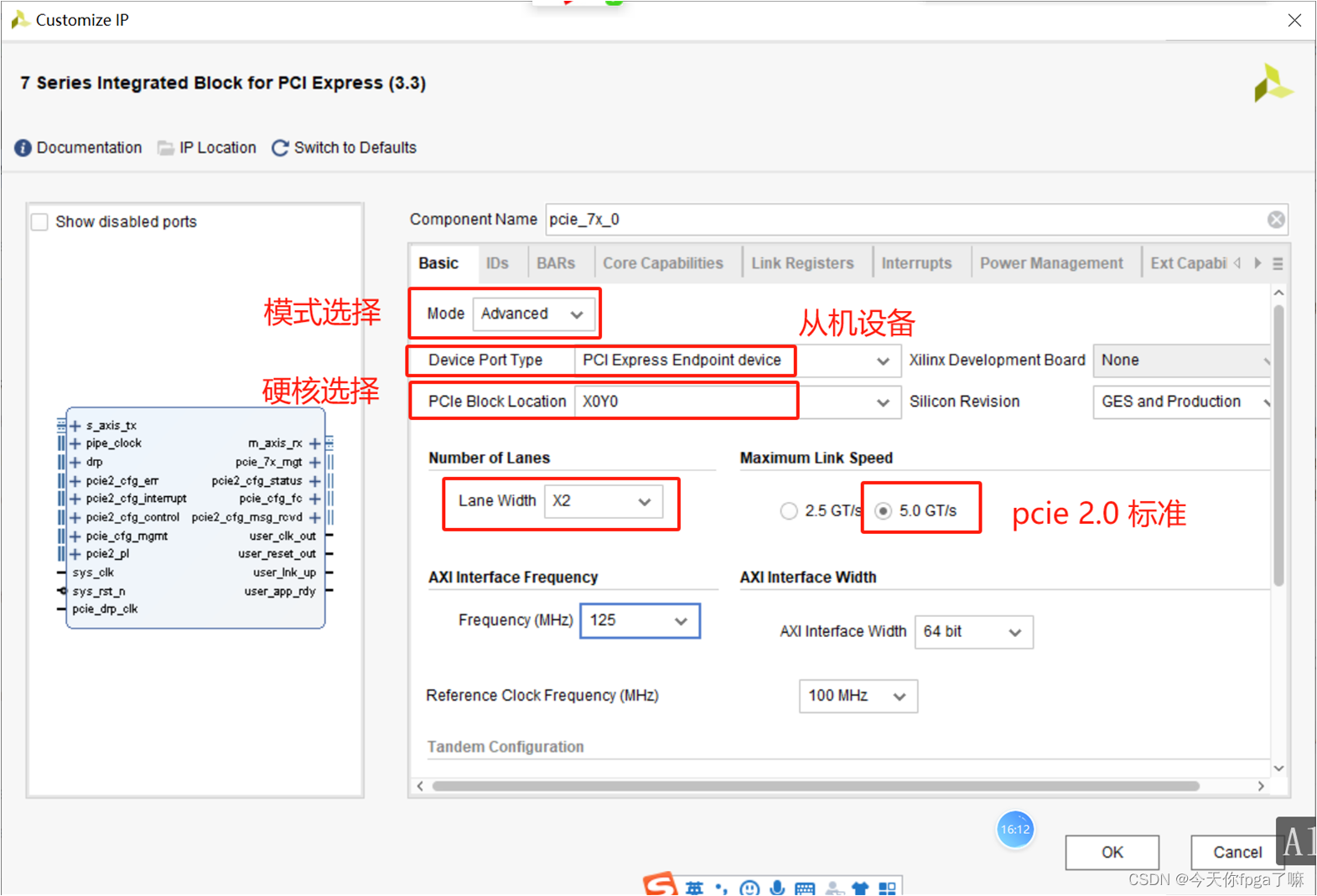

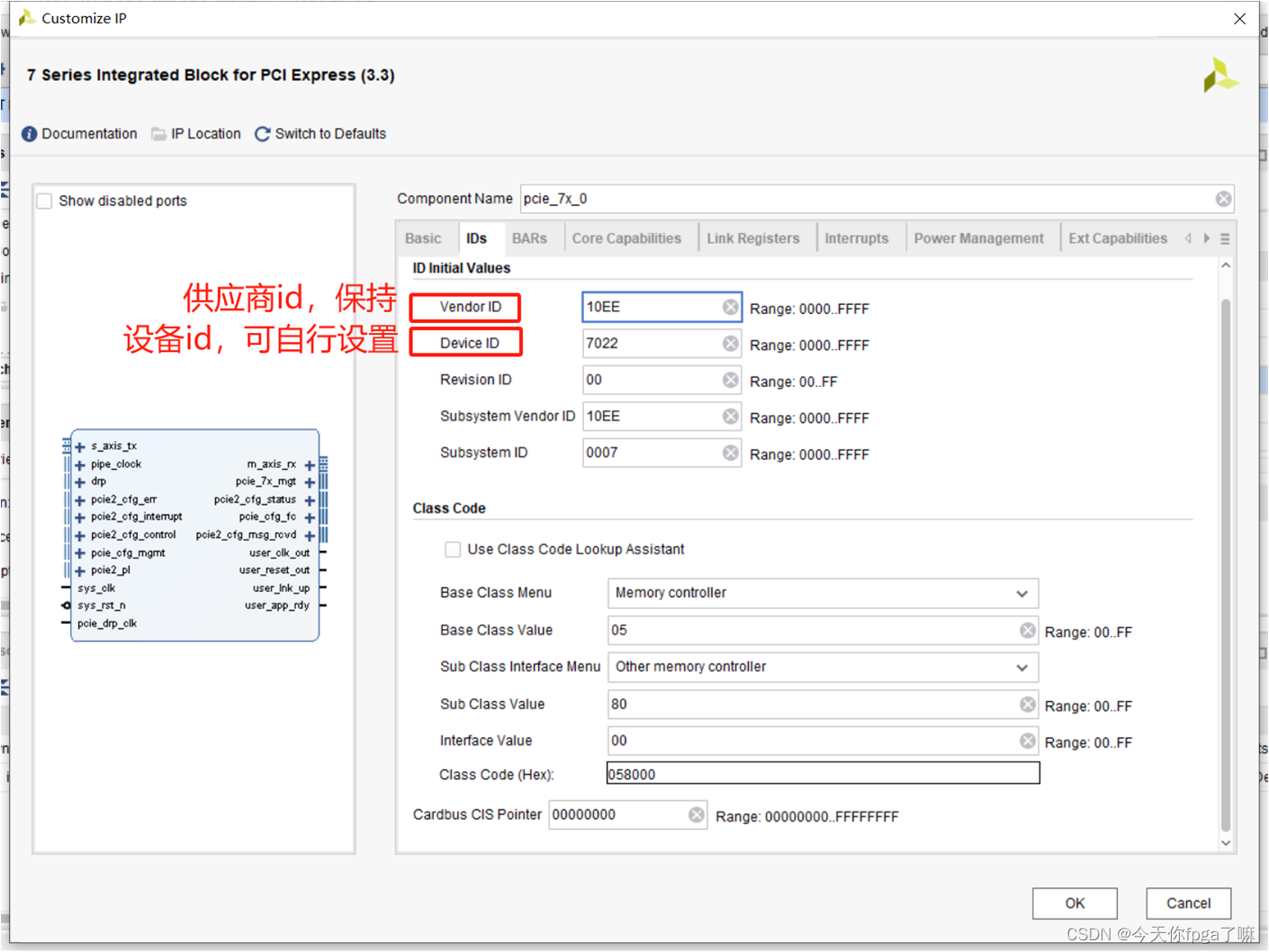

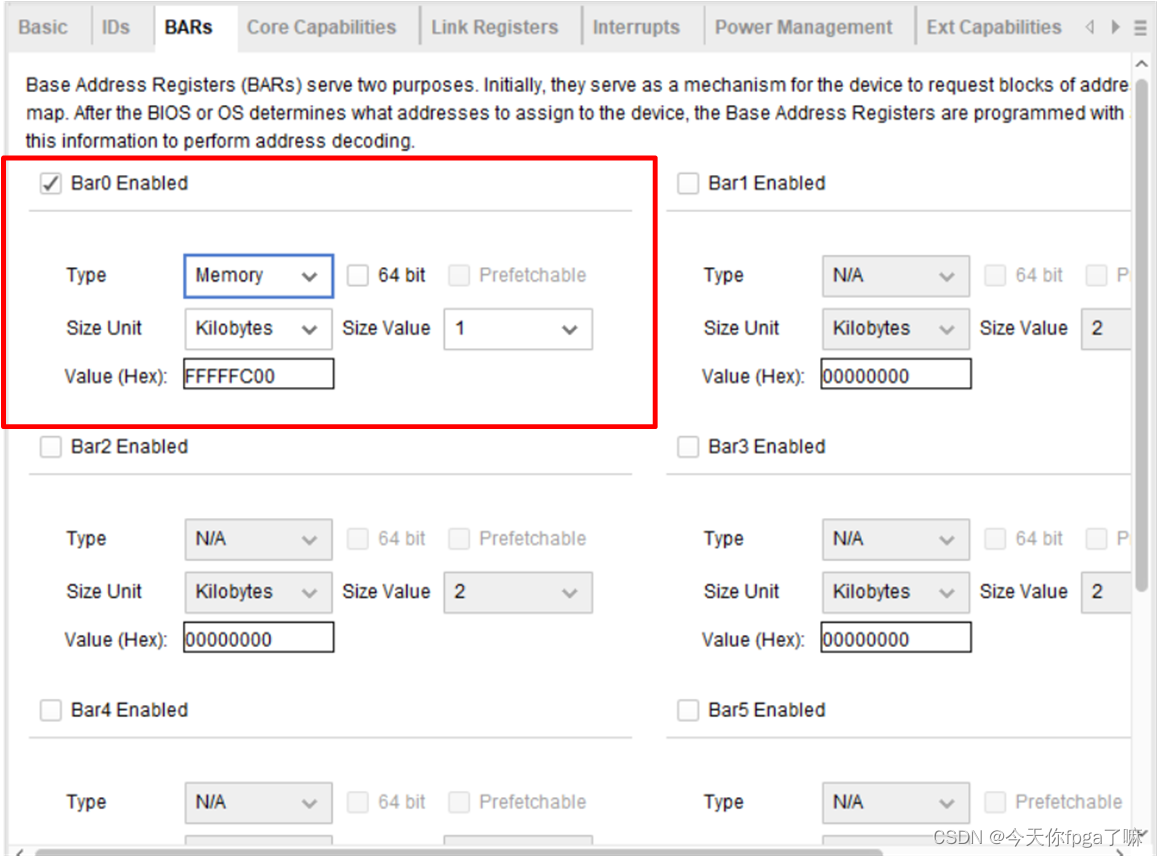

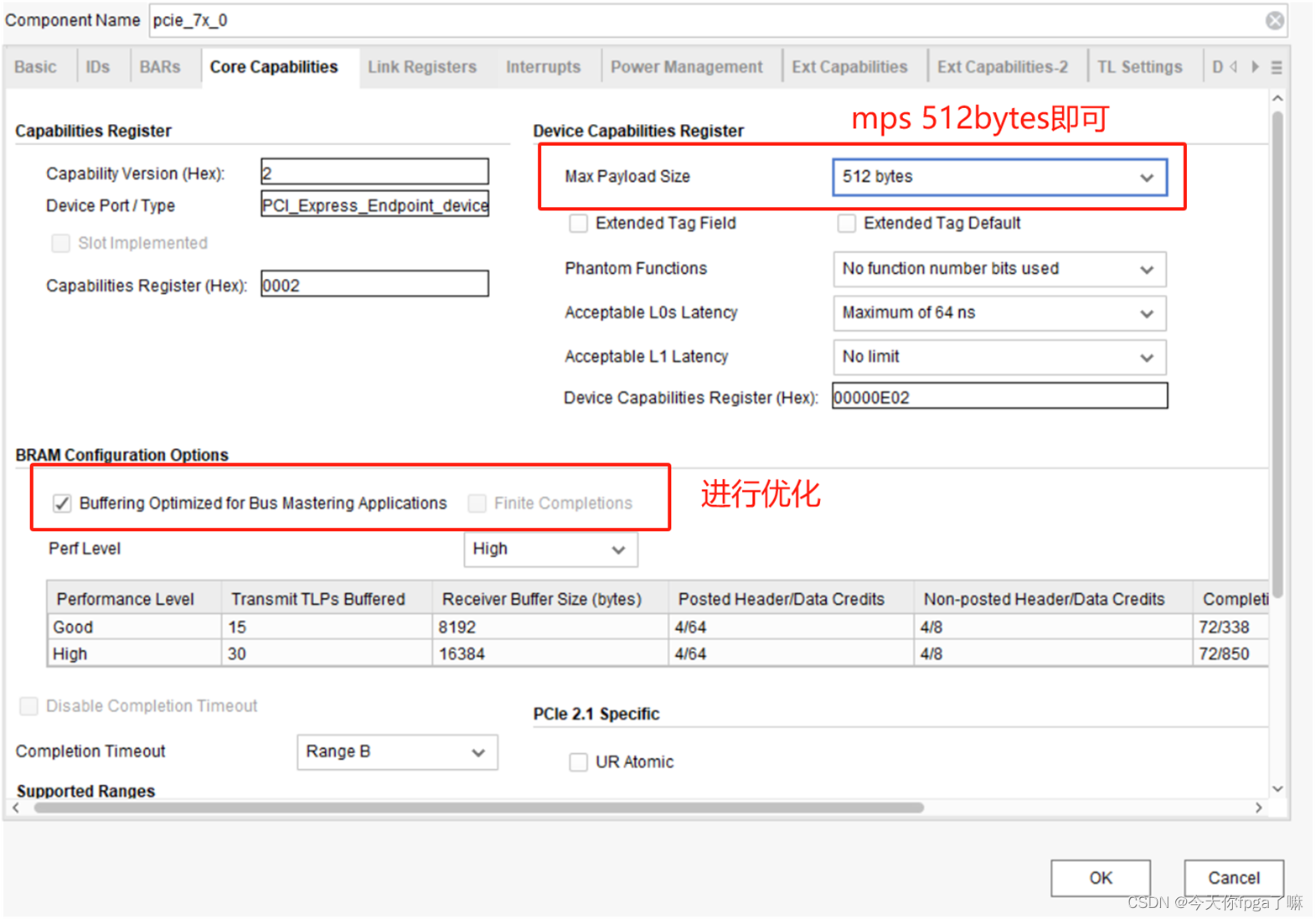

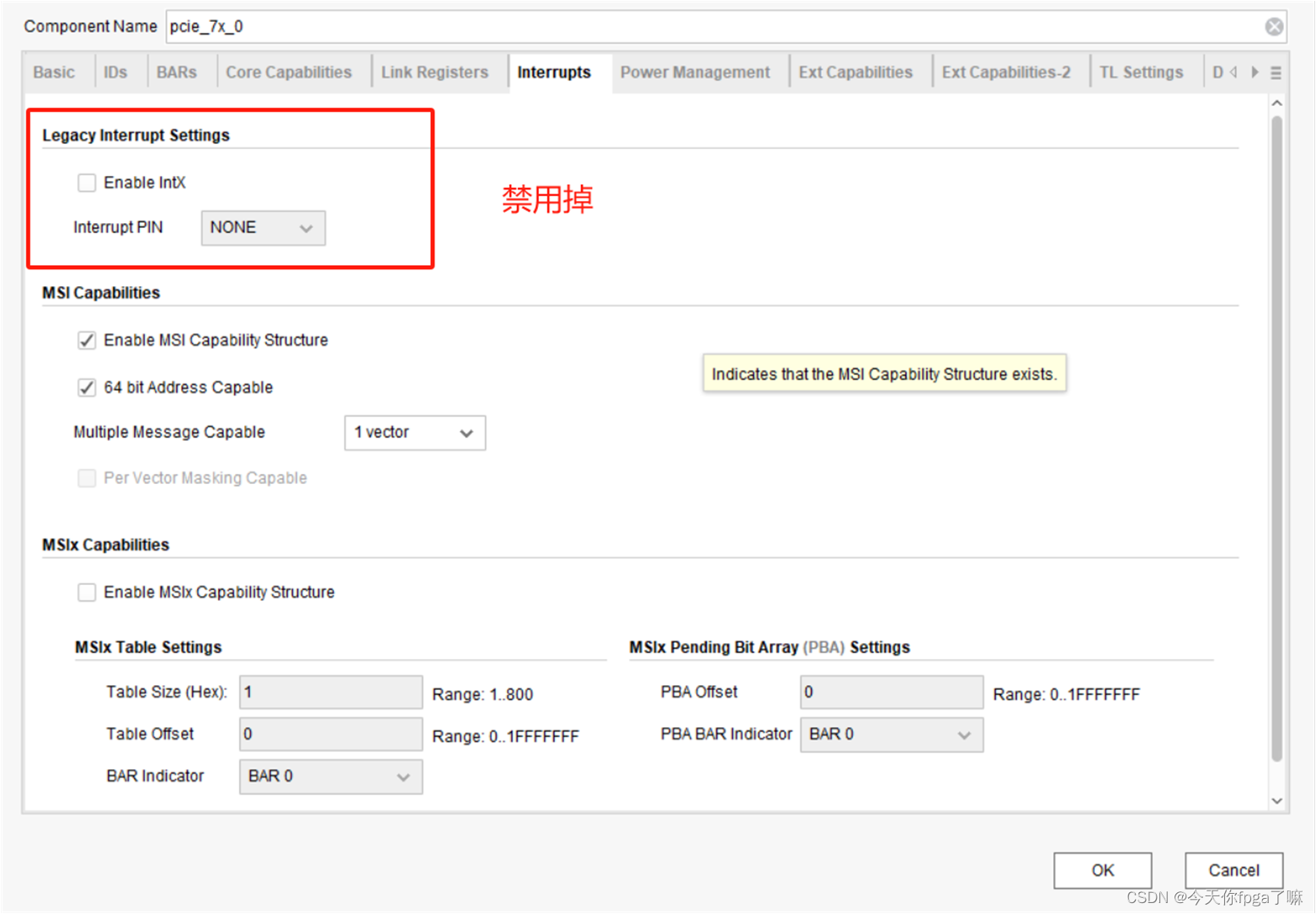

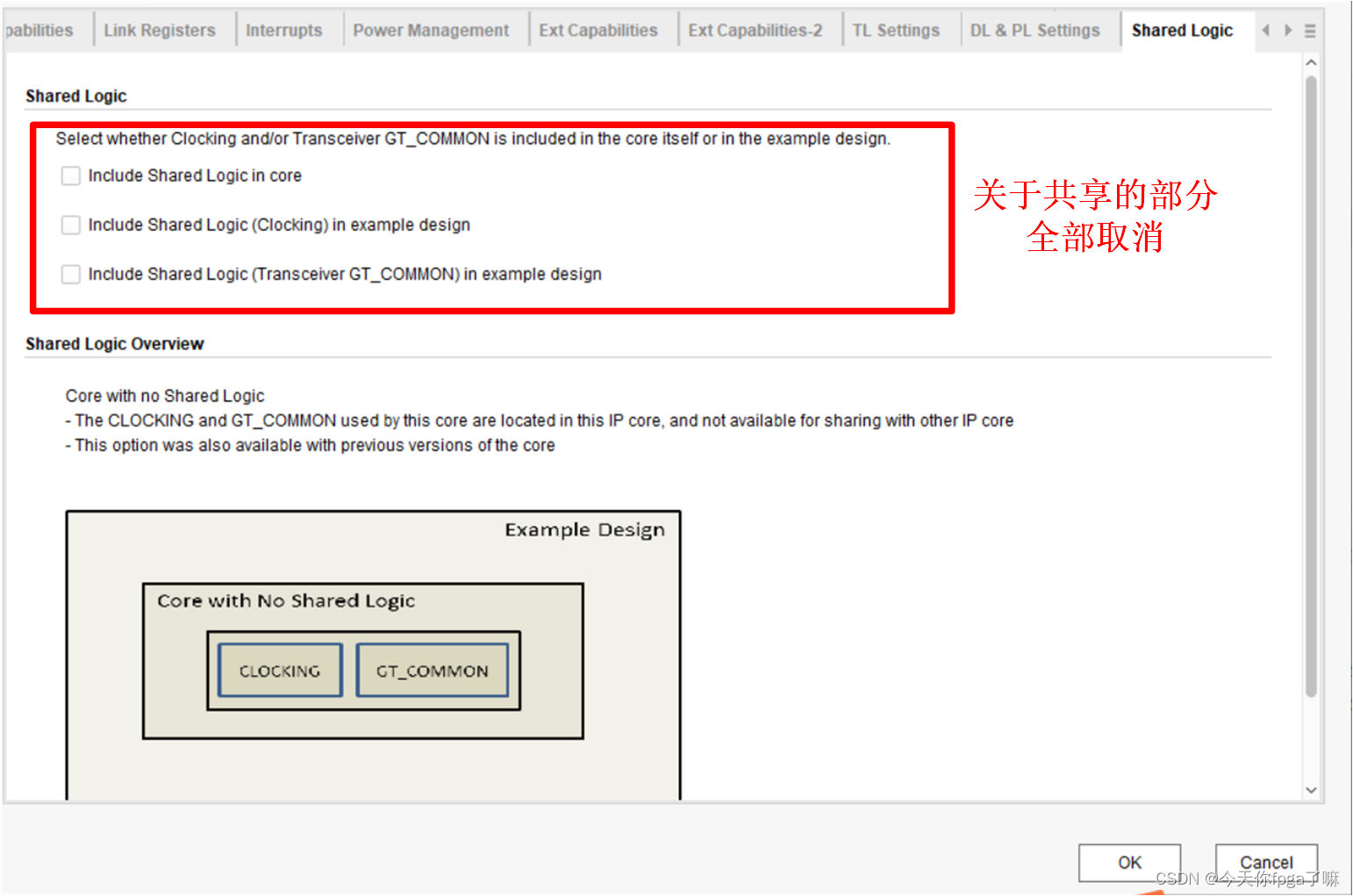

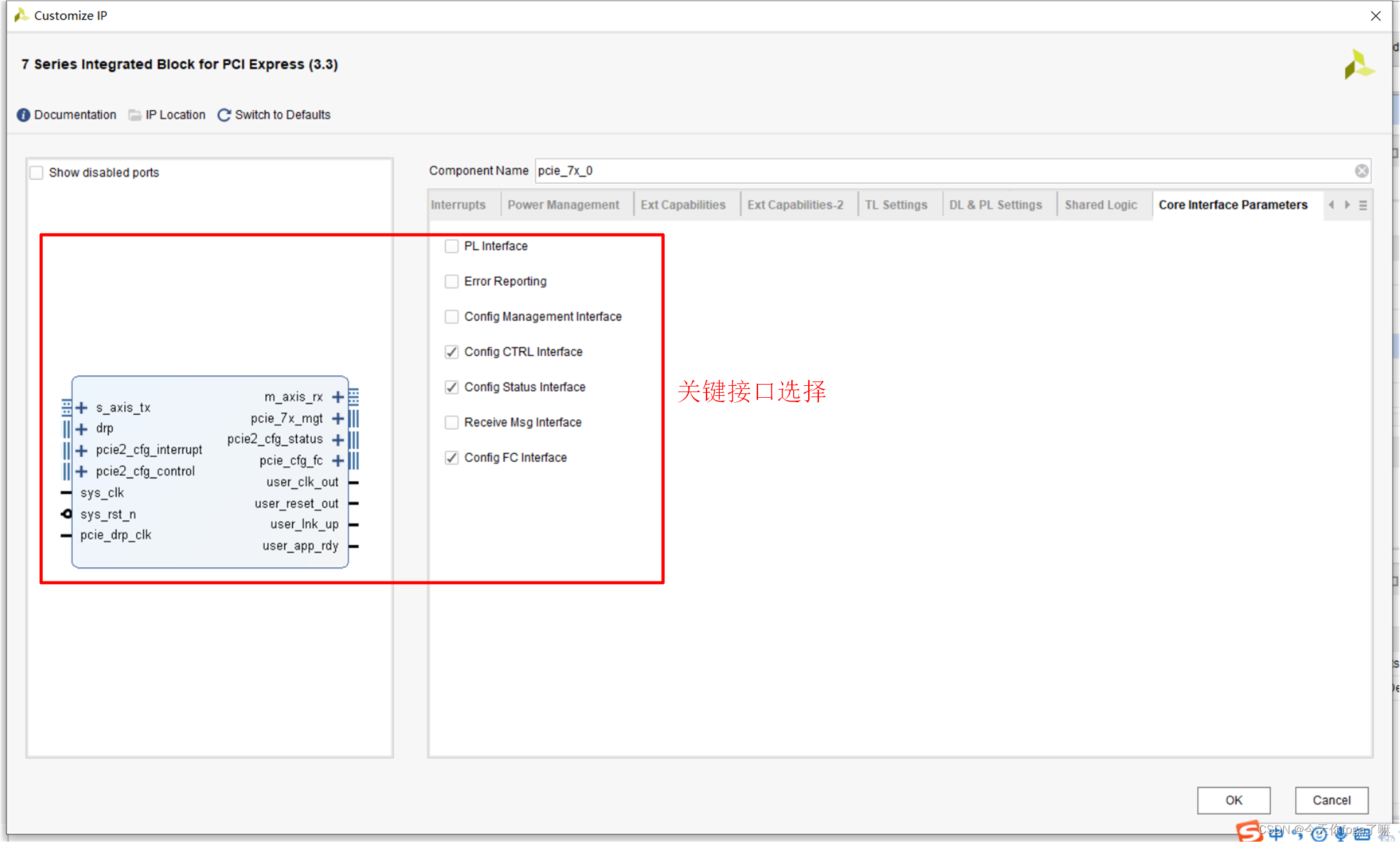

- 1.在工程中调用pcie的ip核(命名为pcie_7x_0),并进行参数设置。

- 2.导入riffa的框架,将pcie的ip核例化到顶层文件当中。(其实顶层文件中已经例化了一个现成的pcie的ip核,所以我们只需要把例化ip核的名称改成我们的pcie_7x_0,并修改部分重要的参数,和我们前面调用ip核时设置的参数保持一致即可)

- 3.修改完成后绑定管脚,生产bit文件,即可下板验证了。

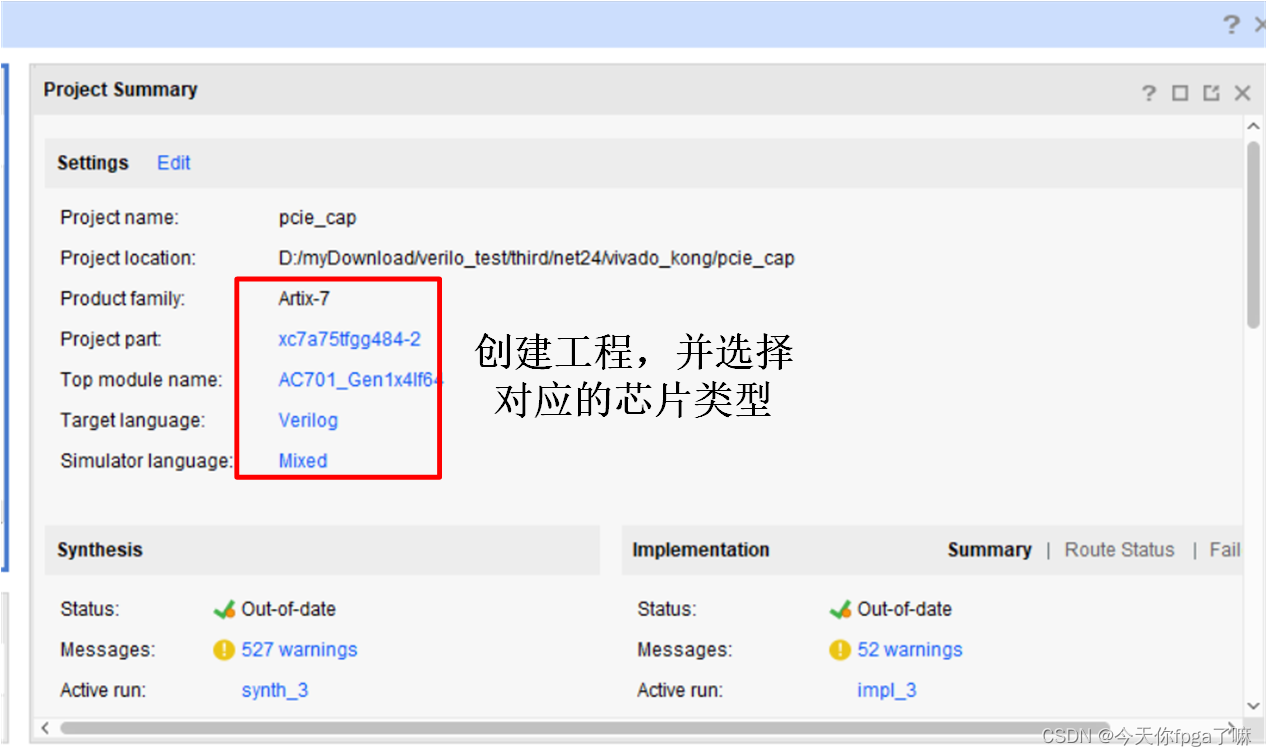

1.创建vivado工程(注意芯片型号的选择)

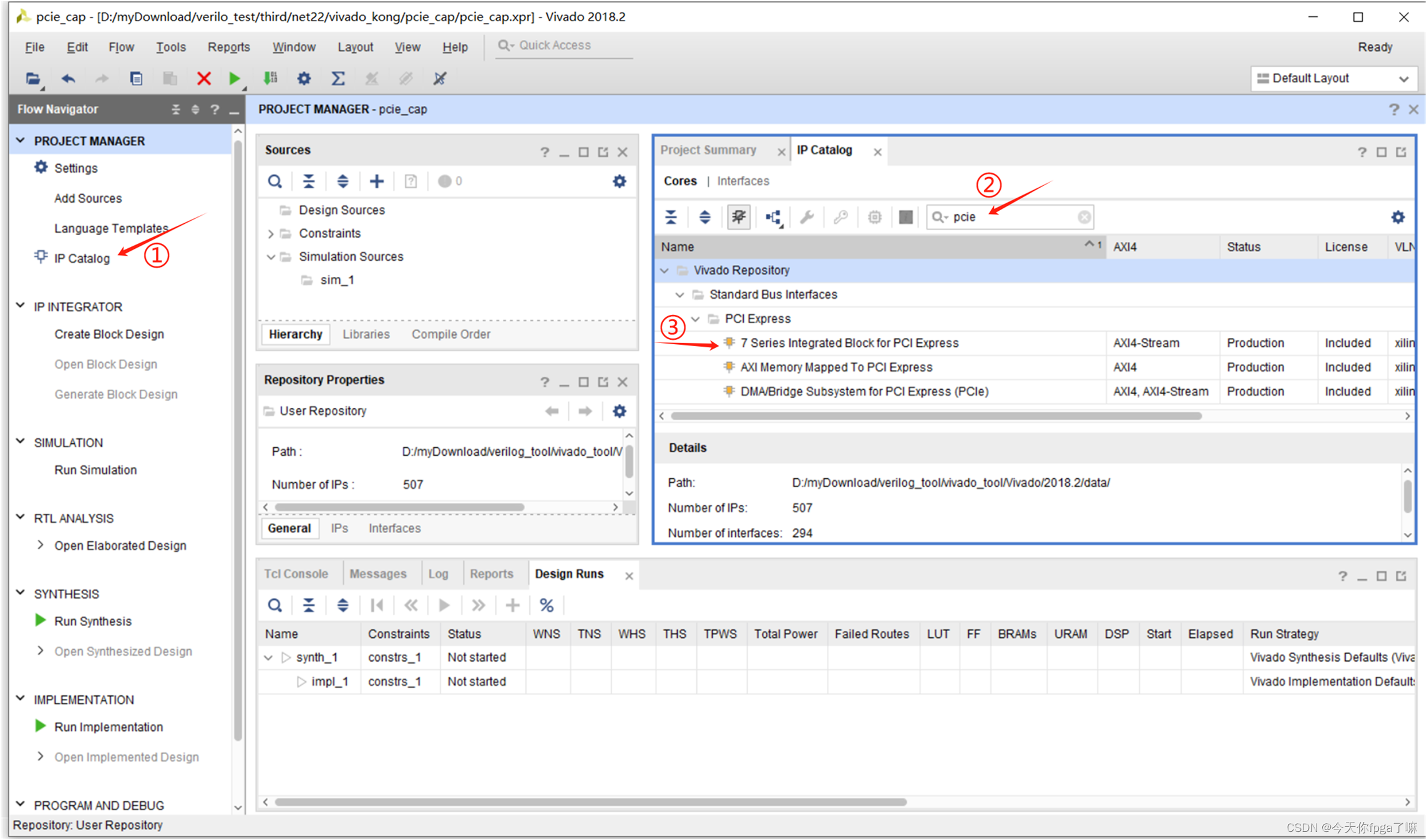

2.pcie ip核的调用

3.导入 Riffa 框架,并做相应修改

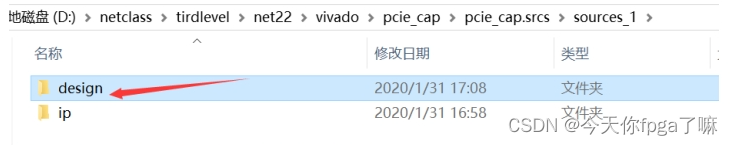

①先在自己vivado工程source目录下建立文件夹design,等下用来存储文件。

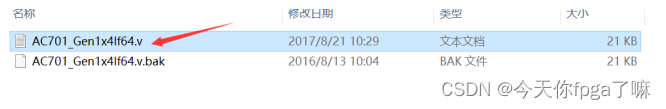

②按照指定路径找到 riffa_2.2.2\source\fpga\xilinx\ac701\AC701_Gen1x4If64\hdl

将该文件复制到design中。

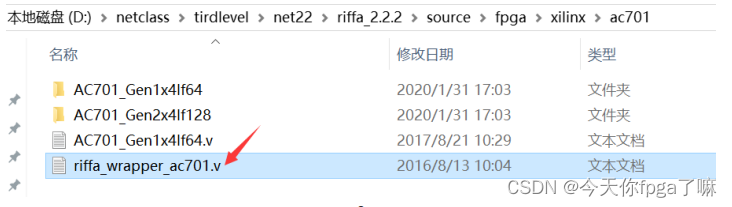

③找到riffa_2.2.2\source\fpga\xilinx\ac701

复制 riffa_wrapper_ac701.v到design中

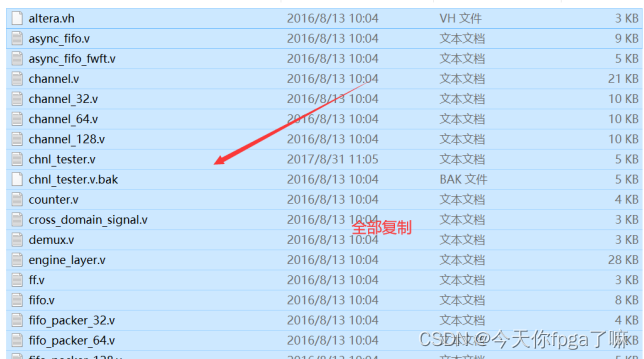

④找到\riffa_2.2.2\source\fpga\riffa_hdl

复制目录里所有文件,黏贴到design中

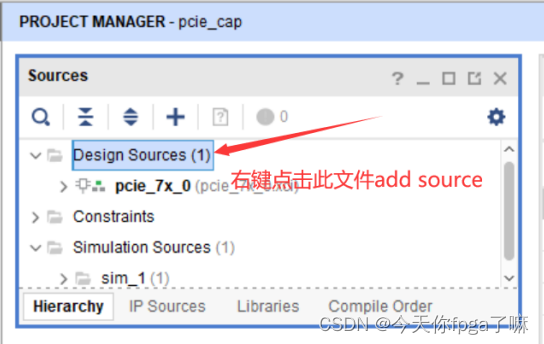

⑤打开vivado,将文件导入到工程中

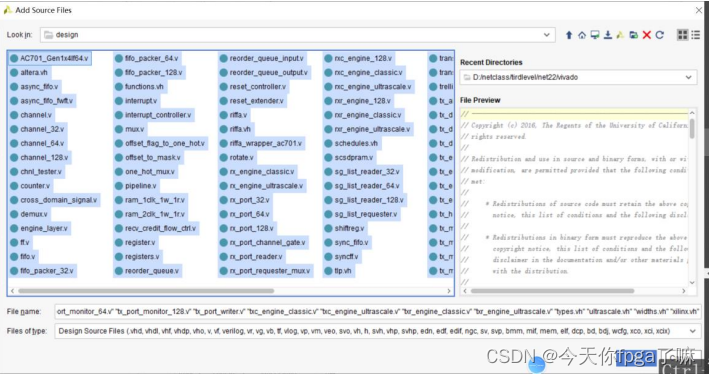

选中刚刚design中添加的所有文件

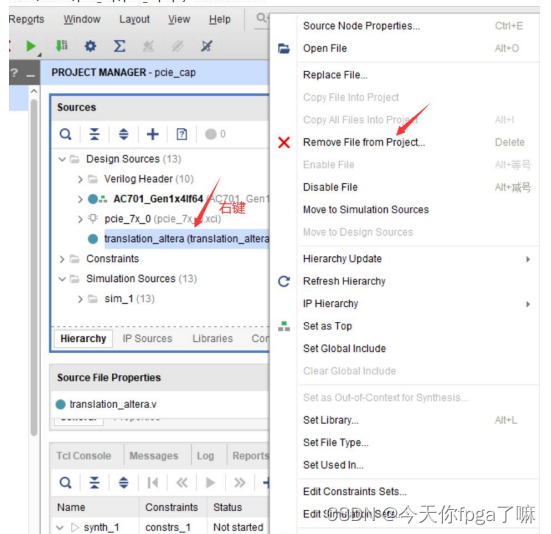

(注意这里还要删除一些关于altera的文件)

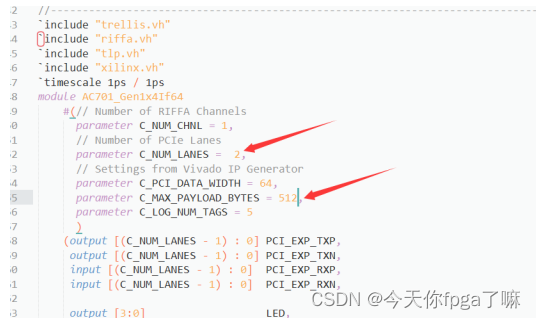

将前面生成的ip核例化到顶层文件( AC701_Gen1x4lf64.v)中去,并修改其中的一些参数,和我们的ip核相匹配。

4.约束 PCIE 相关引脚,生成bit流。

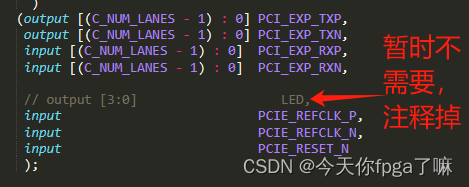

①查看顶层文件,观察我们需要对哪些引脚作约束

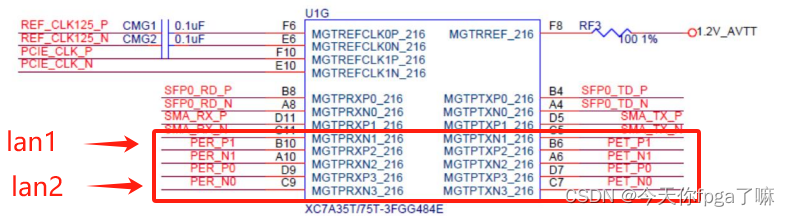

注意:芯片上有4个lane,而我们只用到了2个lane,且tx,rx,clk都是差分信号,只需要约束其中一极,这里需学习一下reset信号的约束方法

set_property IOSTANDARD LVCMOS33 [get_ports PCIE_RESET_N]

set_property PULLUP true [get_ports PCIE_RESET_N]

set_property LOC D21 [get_ports PCIE_RESET_N]

set_property LOC D7 [get_ports PCI_EXP_TXP[0]]

set_property LOC D9 [get_ports PCI_EXP_RXP[0]]

set_property LOC B6 [get_ports PCI_EXP_TXP[1]]

set_property LOC B10 [get_ports PCI_EXP_RXP[1]]

set_property LOC F10 [get_ports PCIE_REFCLK_P]

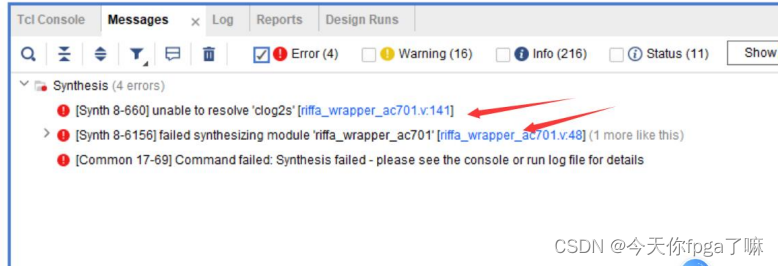

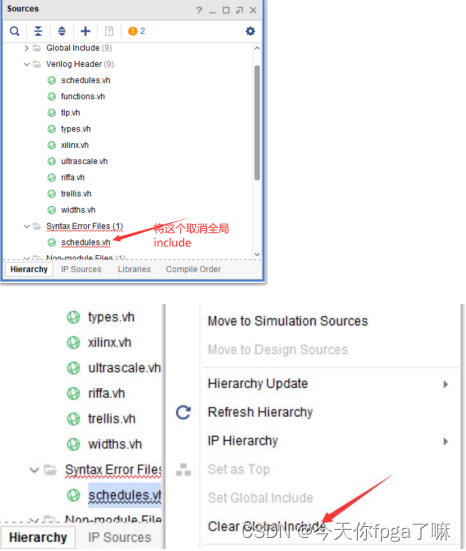

②生成bit文件时出错,需要解决的一些问题

解决办法:

此时生成再生成bit文件即可。

5.使用 jtag 配置板卡 bit 文件,安装驱动做 PCIE 联通测试

这里使用v3学院提供的服务器完成

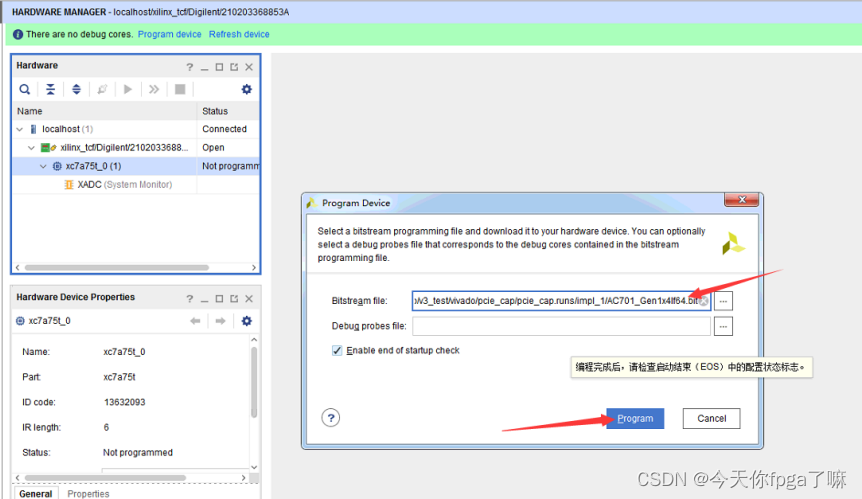

①使用jtag将bit文件下载到板子上

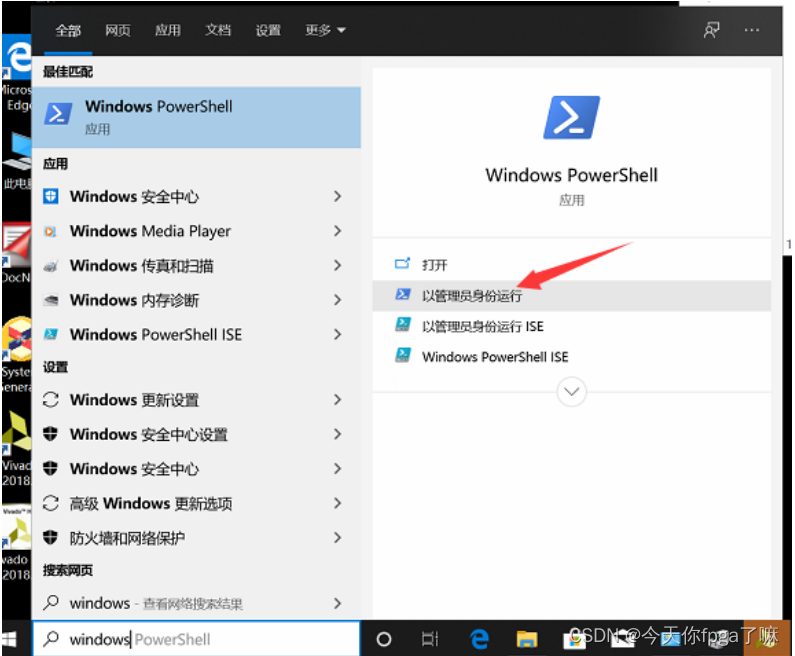

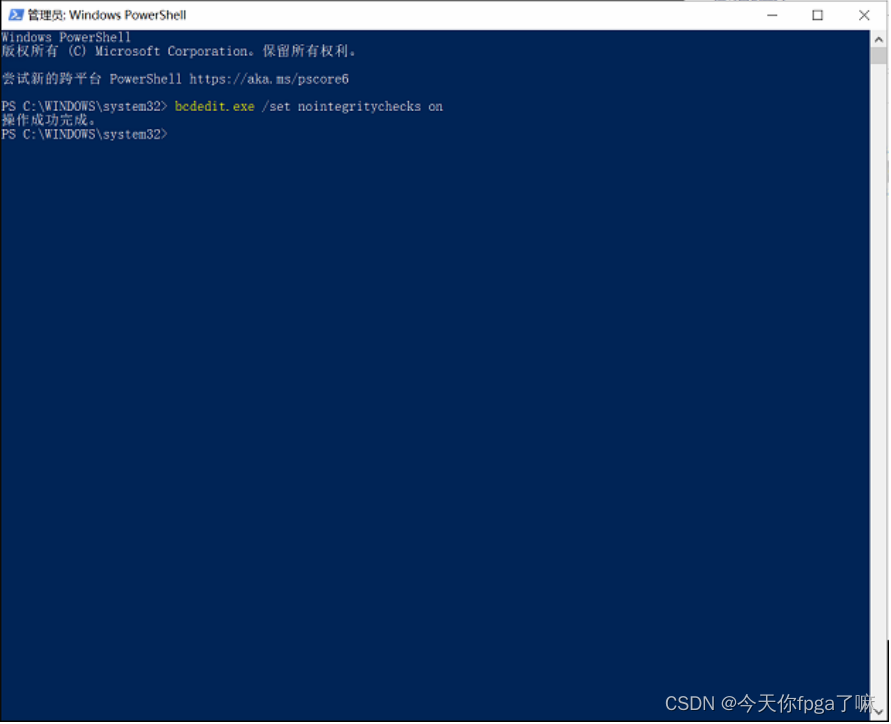

②关闭数字签名(关闭后重启电脑)

复制:bcdedit.exe /set nointegritychecks on,右键粘贴到cmd中

进行第一次重启电脑

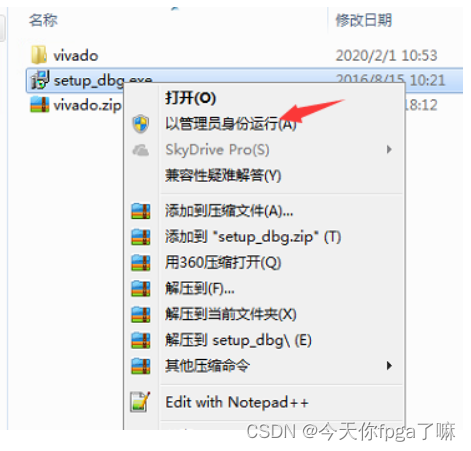

③安装riffa驱动(安装好后进行第二次重启)

安装前先查看一下电脑,是否已经存在riffa的驱动。

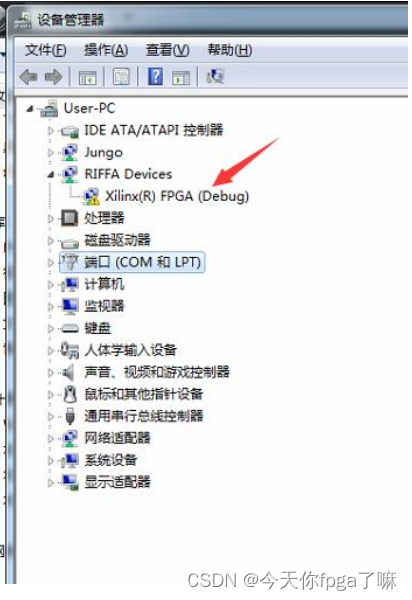

完成后查看设备管理器

进行第二次重启电脑

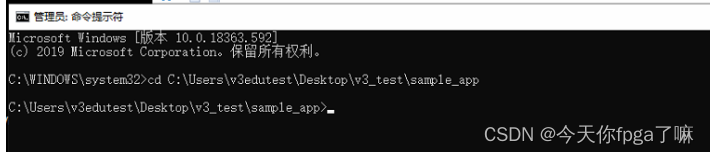

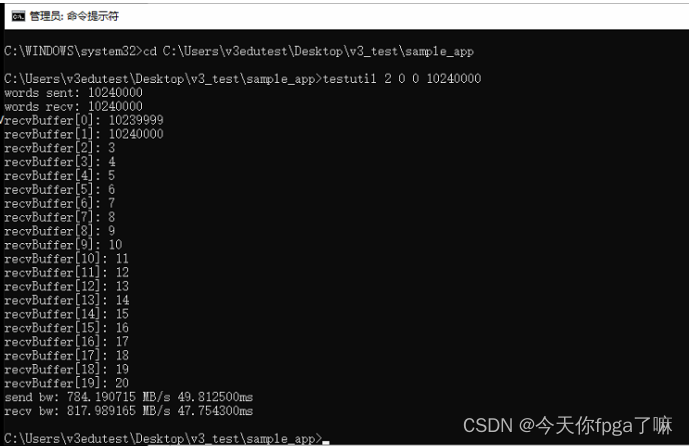

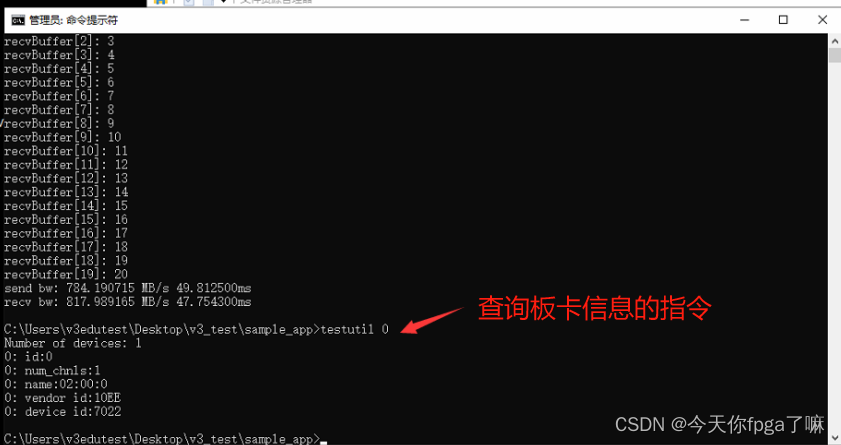

③ 在cmd中进行通信测试

启动cmd输入如下命令:

cd C:\Users\v3edutest\Desktop\v3_test\sample_app ,进入sample_app 中

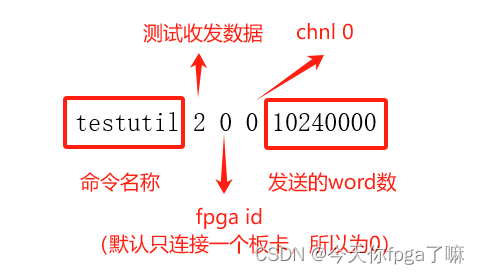

进入后开始使用命令(其实这个命令是sample_app 文件下的 testutil.exe的应用程序,也就是 PCIE 测试程序),进行通信测试。

命令如下:

测试结果如下:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?