前言:本节课开始接触fpga学习中很关键的一章内容——时序分析,也是面试过程中经常会被提到的内容,在这里尽可能的表述清楚,为之后复习做准备。

文章目录

1.什么是时序分析

时序分析本质上是一种时序检查 ,目的是检查设计中所有的D触发器是否能正常工作。

即:

- 检查D触发器的同步端口(数据输入端口)的变化是否满足建立时间(Setup)和保持时间要求(Hold);

- 检查D触发器的异步端口(异步复位端口)的变化是否满足恢复时间要求(Recovery)和移除时间要求(Removal)

2.时序分析的类型

包括:静态时序分析(STA)和动态时序分析。

动态时序分析:将布局布线生成的布线延迟信息反标注到门级网表中进行仿真,来检查是否存在时序违例。此时的仿真包括门延迟和布线延迟信息,能够较好反应芯片的实际工作情况。但是,因为不可能产生完备的测试向量,覆盖门级网表中的每一条路径。因此在动态时序分析中,无法暴露一些路径上可能存在的时序问题。(总结:覆盖度不高,不能全面暴露问题)

静态时序分析:采用穷尽分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误。它不需要输入向量就能穷尽所有的路径,且运行速度很快、占用内存较少,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计,因此静态时序分析已经越来越多地被用到数字集成电路设计的验证中。

3.时序分析中常用的术语

源时钟(Source Clock/Launch Clock,也称为发起时钟)

目的时钟(Destination Clock/Capture Clock,也称为捕获时钟)

发起沿(Destination Clock/Capture Clock,也称为捕获时钟)

捕获沿(capture edge,目的时钟捕获数据的有效时钟沿)

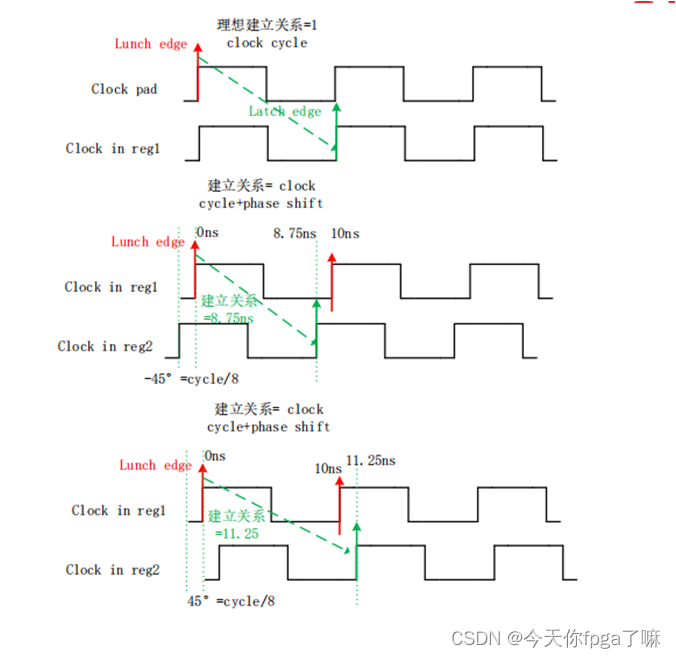

发起沿(launch edge)通常在0ns,捕获沿/锁存沿(latch edge)通常在下一个发起沿,发起沿和捕获沿通常相差一个时钟周期。

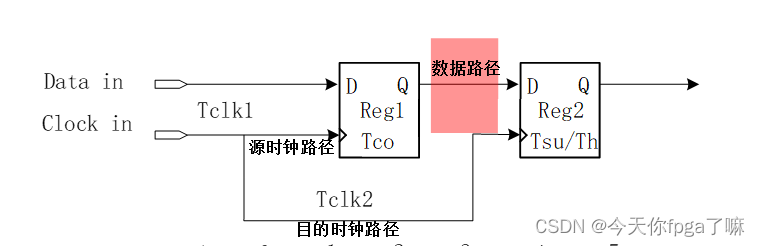

4.一条普通时序路径的三要素

==源时钟路径:==从源时钟的源节点(通常是FPGA的时钟输入引脚)到源寄存器的时钟端口的路径。当时序路径的起点是FPGA输入端口时,该时序路径是没有源时钟路径的。

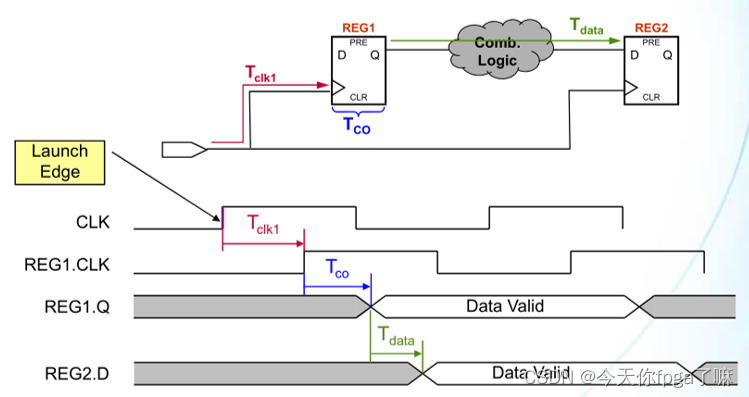

==数据路径:==从时序路径的起点到时序路径的终点之间的数据传播路径。时序路径的起点可以是源寄存器的时钟端口或FPGA的输入端口,时序路径的终点可以是目的寄存器的输入端口或FPGA的输出端口。

==目的时钟路径:==从目的时钟的源节点(通常是FPGA的时钟输入引脚)到目的寄存器的时钟端口的路径。当时序路径的终点是FPGA的输出端口时,该时序路径是没有目的时钟路径的。

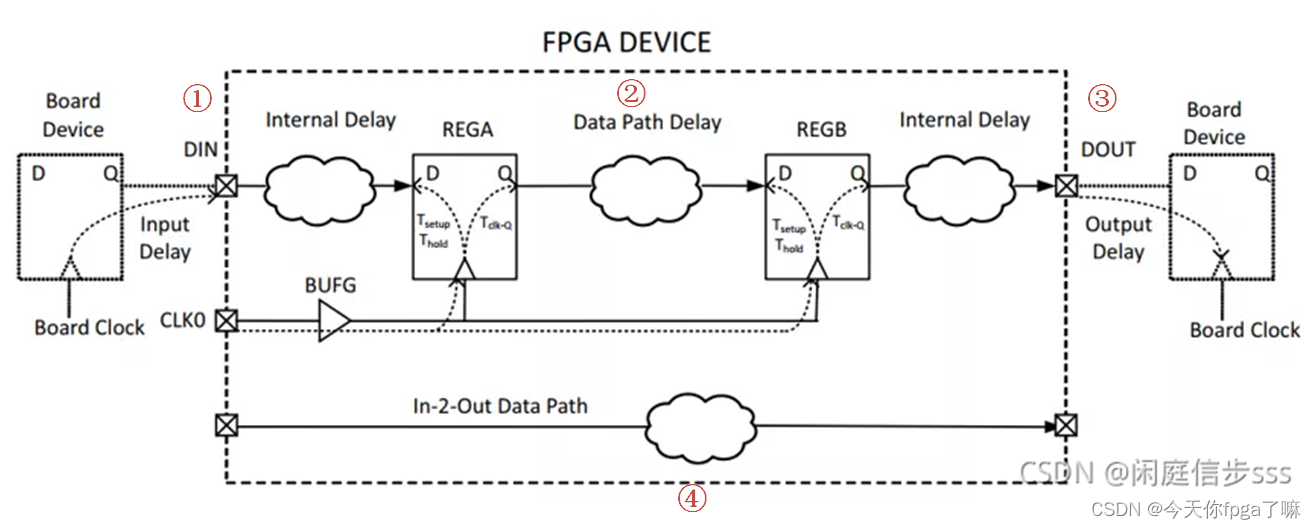

5.fpga中常见的四种时序路径

① 输入pad与寄存器之间

过程描述:

数据由Board clock发起并在FPGA外部产生;

数据经过Input Delay的延迟后到达FPGA的输入端口;

数据经过FPGA的Internal Delay后到达由目的时钟驱动的目的寄存器。

这种路径是没有源时钟路径的,用户需要约束Input Delay和时钟来告知时序引擎必要信息,时序引擎才能正确的分析这种路径。

② 寄存器与寄存器之间

过程描述:

数据由源时钟发起并在FPGA内部产生;

数据经过Data Path Delay后到达由目的时钟驱动的目的寄存器。

这种时序路径是最常见的,用户需要约束源时钟和目的时钟告知时序引擎必要的信息,时序引擎才能正确的分析这种时序路径。

③寄存器与pad之间

过程描述:

数据经过Internal Delay后到达输出端口;

数据经过Output Delay后被Board Clock捕获到。

这种路径是没有目的时钟路径的,用户需要约束Output Delay和时钟来告知时序引擎必要信息,时序引擎才能正确的分析这种路径。

④pad与pad之间

过程描述:

数据横穿FPGA,没有经过任何触发器,这种路径也叫in-to-out path,约束输入和输出延时的参考时钟可以使用虚拟时钟。

这种路径中只有数据路径,用户需要约束Input Delay和Output Delay,告知时序引擎必要的信息,时序引擎才能正确的分析这种时序路径。

6.各种到达时间的具体含义

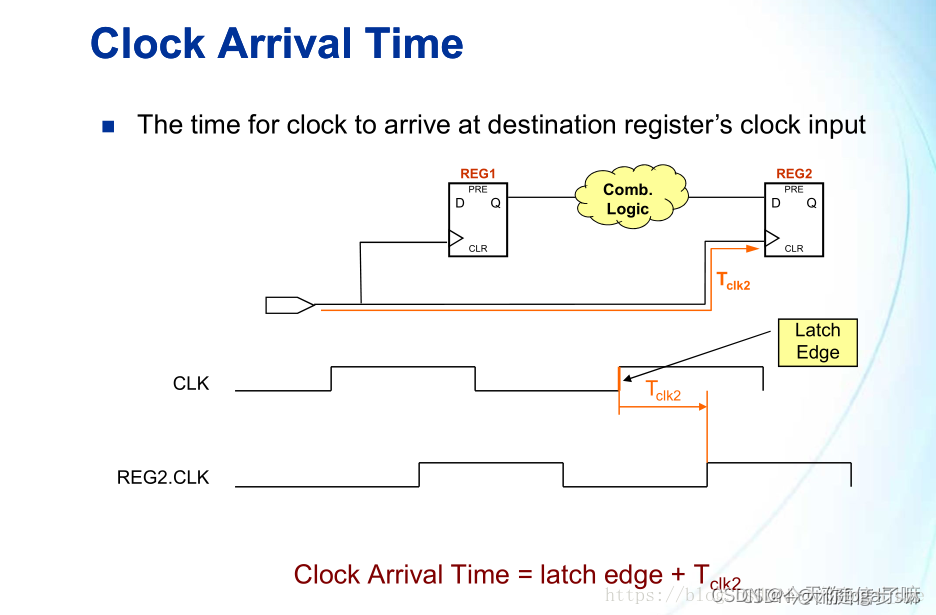

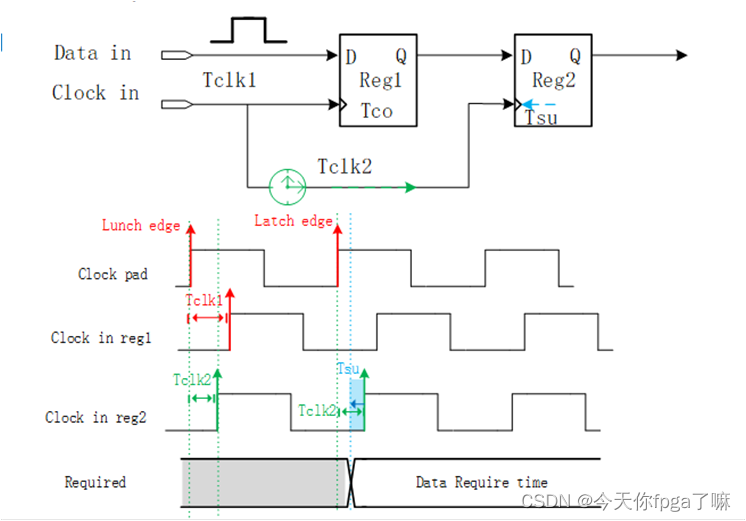

1.时钟到达时间(clock arrival time)

含义:指时钟从latch edge到达目的寄存器输入端所用的时间。

公式:clock arrival time =latch edge+ Tclk2

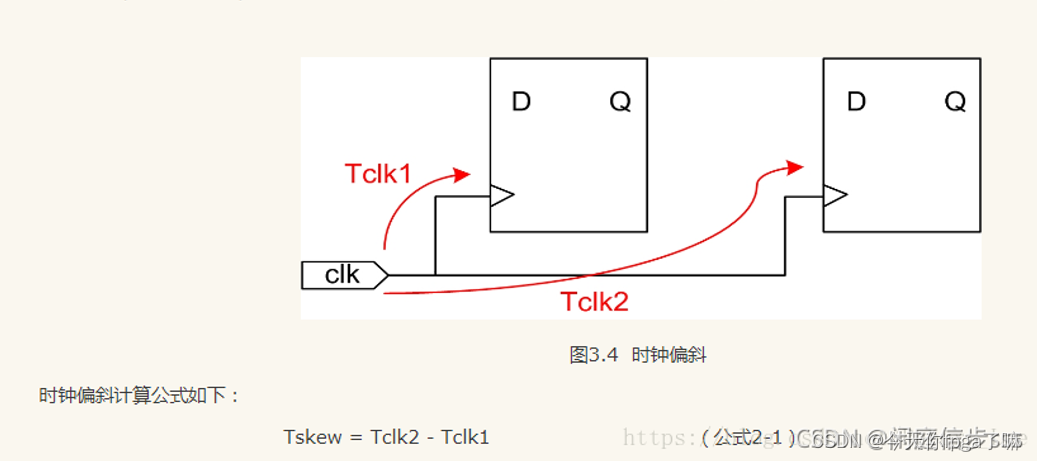

2.时钟偏斜(clock skew)

含义:一个时钟源到达两个不同寄存器时钟端的时间偏移。

公式:Tskew=Tclk2-Tclk1

3.数据到达时间 (data arrival time)

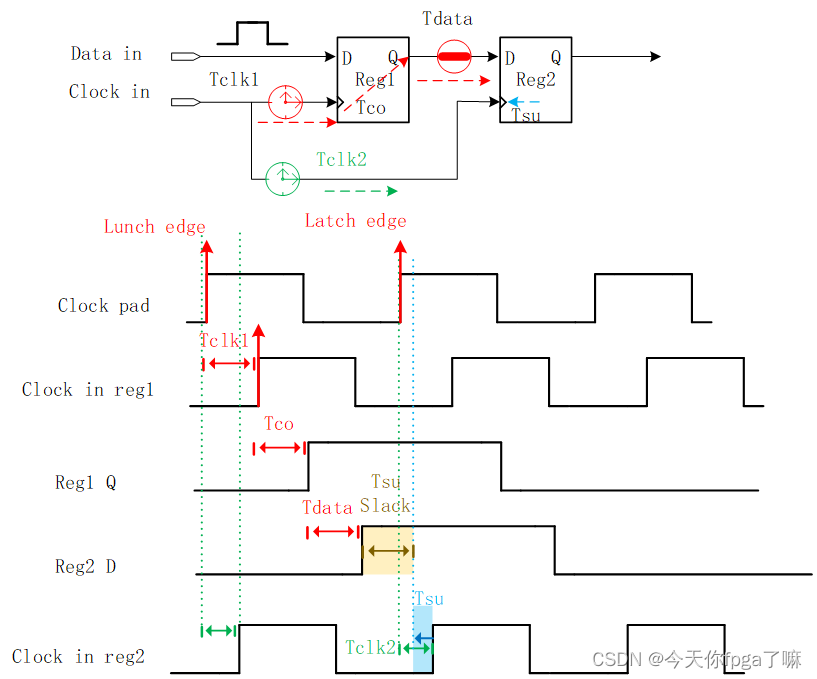

含义:数据由发射沿时钟到达目标采样寄存器的D端时间

公式:Data Arrival time = Lunch edge+Tclk1 + Tco + Tdata

4.数据需求时间(data required time)

含义:数据最晚到达的时间

公式:Data require time=clock arrival time -最小建立时间(tsu)

= Latch edge+Tclk2-Tsu

5.建立时间余量(Setup Slack):

含义:要求最晚的到达时间(data require time )– 数据实际到达时间(data arrival time)

公式:Tsu slack =Data required time- Data arrival time=(Latch edge + Tclk2 -Tsu)-(Lunch edge + Tclk1 + Tco +Tdata)

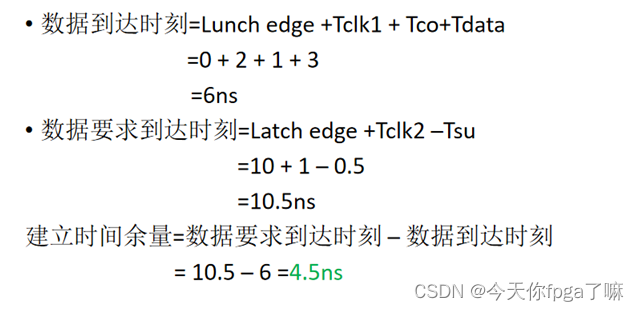

相关例题:

Tcyc=10ns;Pin2PLL=4ns;Tclk1=2ns;Tclk2=1ns;Tco=1ns;Tsu=0.5ns;Tdata=3ns

求:Tsu slack??

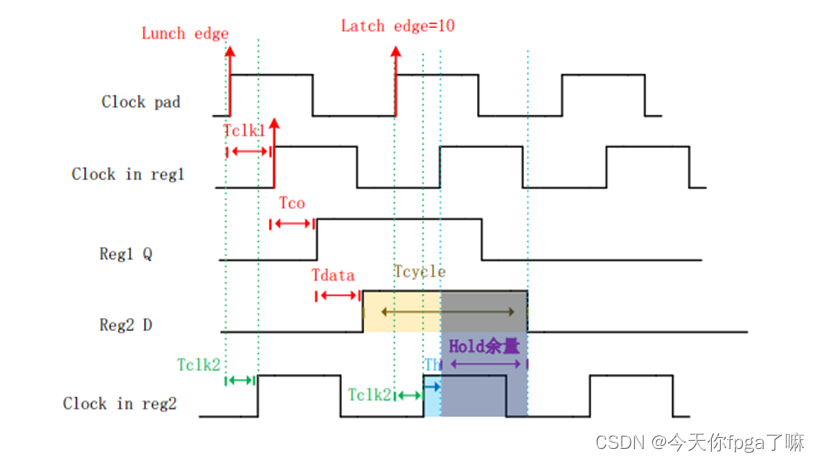

6.保持时间余量计算(hold slack)

保持时间余量=数据实际结束时刻-数据要求结束时刻

数据实际结束时刻=data arrival time + tcycle

数据要求结束时刻=latch edge + tclk2 + th

公式:hold slak =(data arrival time + tcycle)-(latch edge + tclk2 + th)

相关例题:

Tcyc=10ns;Pin2PLL=4ns;Tclk1=2ns;Tclk2=1ns;Tco=1ns;Th=0.5ns;Tdata=3ns

求:Th slack

7. 关于建立关系的一些额外补充

latch edge - lunch edge=建立关系

但!不是所有的建立关系都是一个时钟周期

同源同频同相位时钟理想建立时间关系:

公式:建立关系= clock cycle+phase shift

(正偏右移 反偏左移)

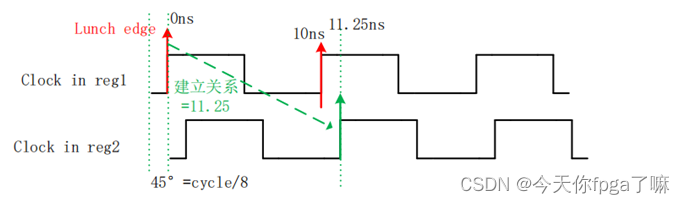

假设将 latch 时钟相移45 度

此时建立关系=clock cycle+(clock cycle*1/8)=10+1.25=11.25

则,建立时间余量(setup slack)计算如下:

总结:

1.建立关系值影响了建立时间余量的计算

2.时钟的skew(tclk2-tclk1)影响建立余量计算

3.数据路径延时(tdata)和tco也会影响建立时间计算

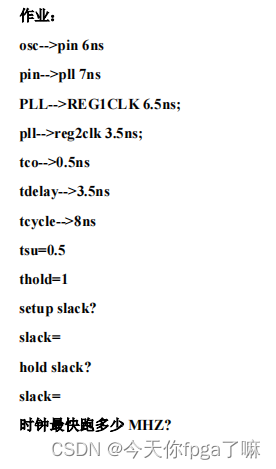

8. 经典计算题示例

答:

1952

1952

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?