数字信号处理(一):Xilinx Vivado DDS IP核设计实例 https://blog.csdn.net/gslscyx/article/details/104024041

vivado DDS IP核参数设置和仿真

https://blog.csdn.net/weixin_43773312/article/details/103964418

Vivado DDS IP核使用和仿真(一、单通道信号发生器)

https://blog.csdn.net/u013215852/article/details/91042672

Vivado DDS IP核使用和仿真(二、多通道信号发生器)

https://blog.csdn.net/u013215852/article/details/91044141

vivado dds Compiler v6.0 学习笔记

https://blog.csdn.net/Real003/article/details/102596387

以上为参考的几篇文章,学习整理如下:

一、DDS IP核简介

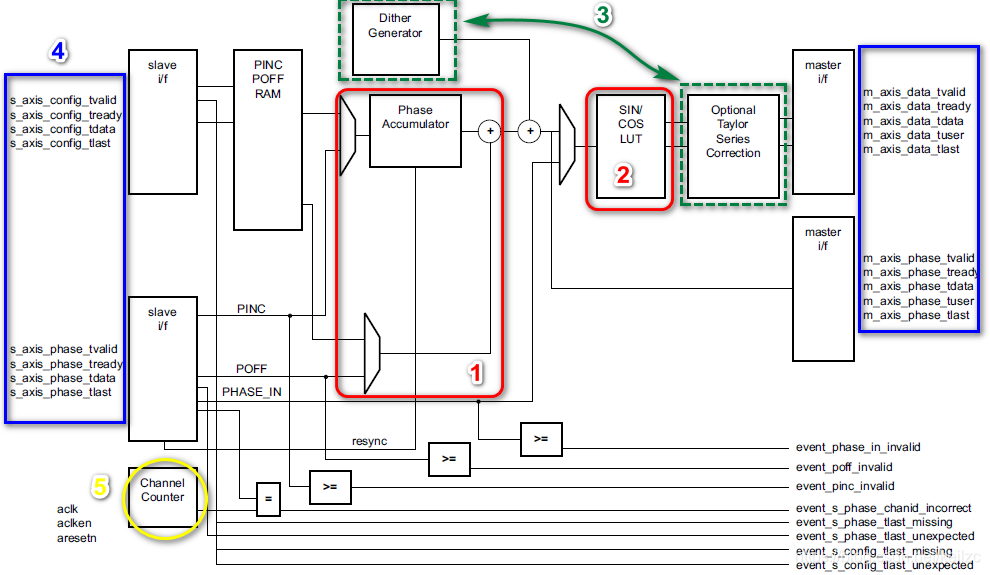

图中我们看到DDS IP核主要包括5部分组成,其中DDS核心为相位累加器(标记1所示)和LUT查找表(标记2所示)。相位累加器实现查找表地址的产生,LUT查找表用来存储输出波形。标记3部分为抖动产生器和泰勒级数矫正产生模块,主要用来改善SFDR,两者改善的效果、使用的逻辑资源存在差异。标记4部分则为AXI4接口,实现相位累加字配置,多通道配置,相位累加器输出和波形数据输出。标记5部分则在多通道DDS输出时使用。

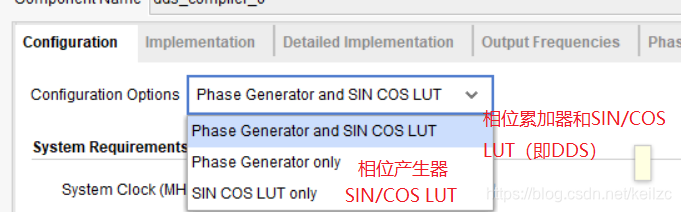

DDS IP核可以配置为三种模式:相位产生器、SIN/COS LUT或者相位累加器和SIN/COS LUT(即DDS)。

二、参数解释

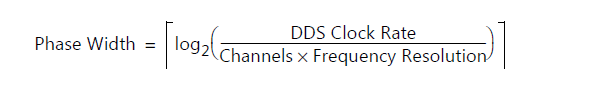

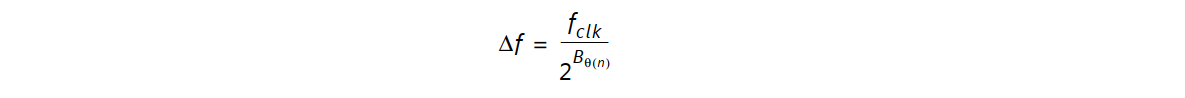

phase width是相位累加器的位宽,Frequency Resolution是频率分辨率,channels是IP核设置的通道数,默认通道数为1时,二者对应关系(对应dds频率分辨率公式):

只不过在VIVADO的DDS IP核使用中,频率分辨率与通道数有关。

只不过在VIVADO的DDS IP核使用中,频率分辨率与通道数有关。

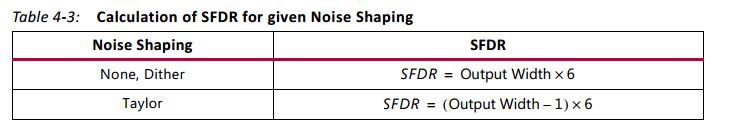

output width是输出波形的数据位宽,一般与DA转换器匹配,SFDR(Spurious Free Dynamic Range(dB))与之有关,具体换算关系见表格4-3。

三、参数配置测试

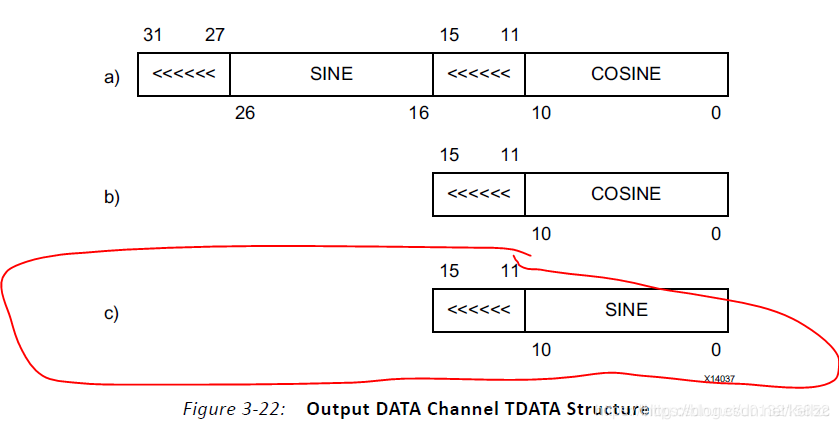

关于output不同的选择,输出数据的格式如下:

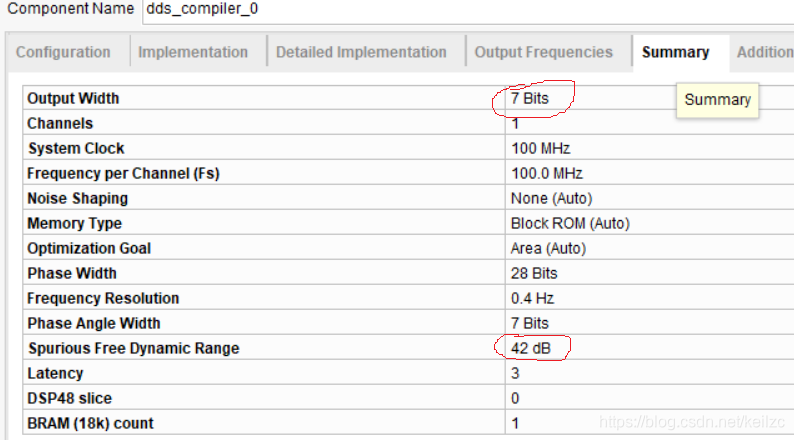

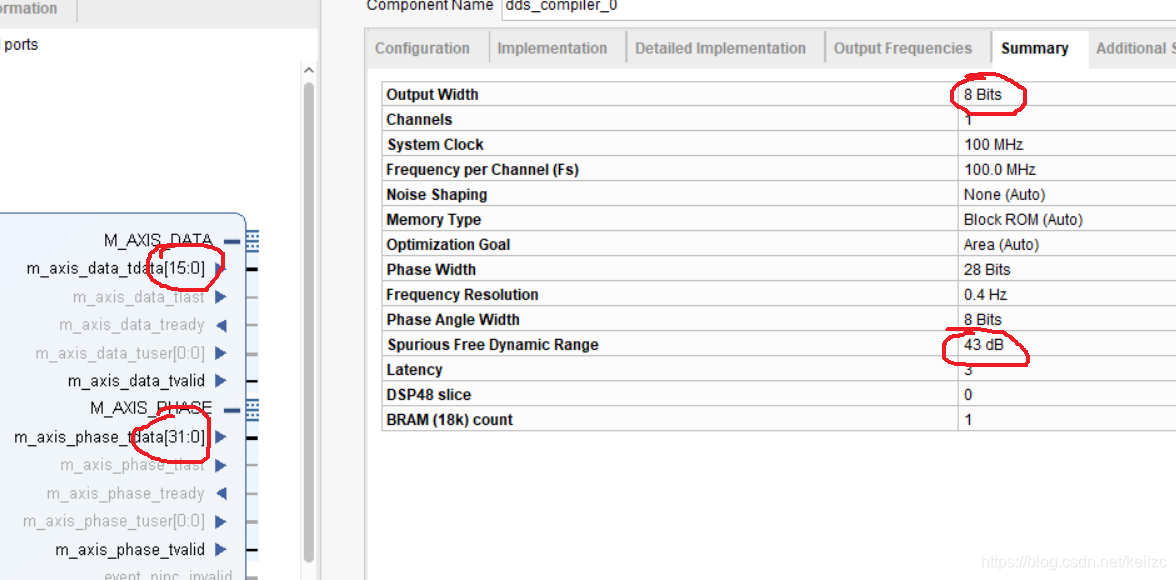

output width与sfdr设置测试

sfdr = 42时,output width = 7:

sfdr = 43时,output width = 8:(注意此时图形界面中data位宽为16)

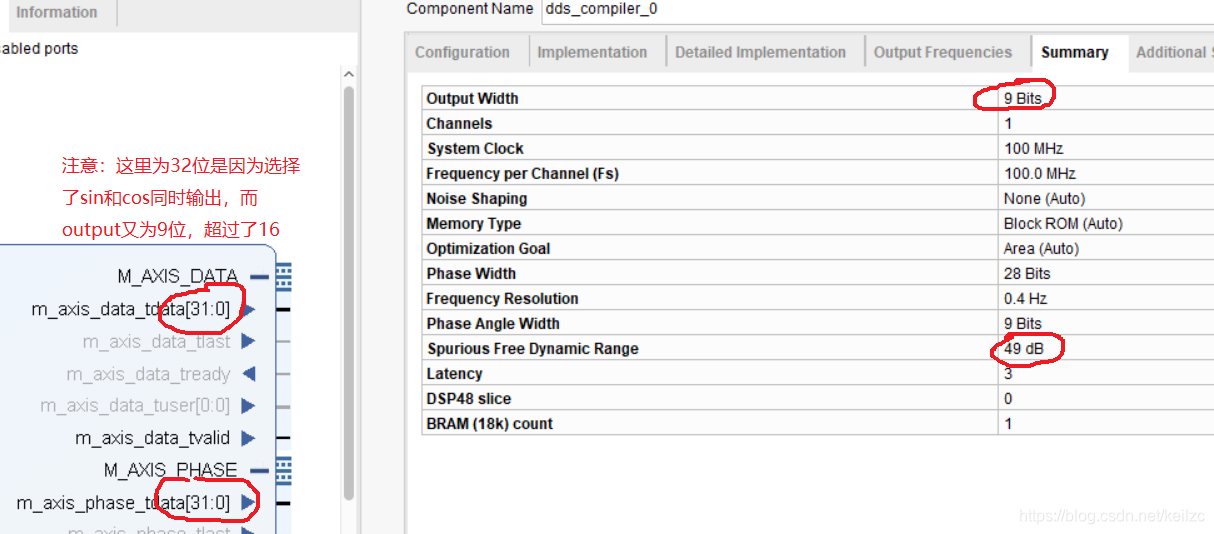

sfdr = 49时,output width = 9:(注意此时图形界面中data位宽为32)

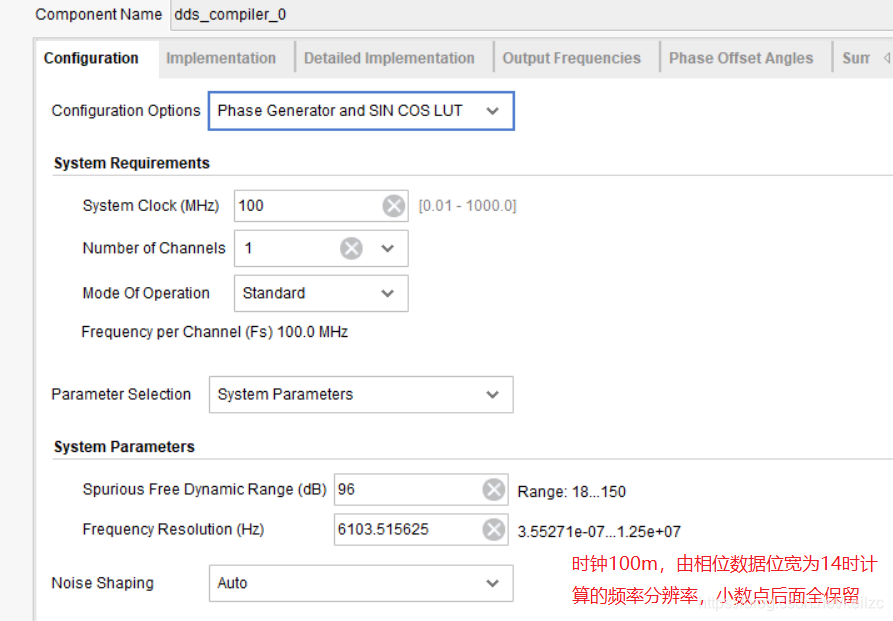

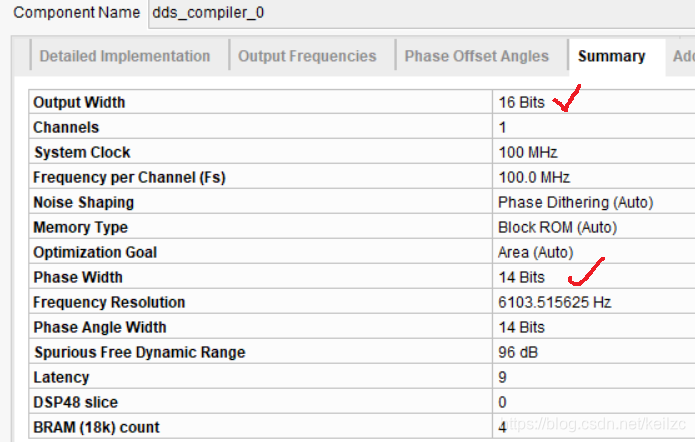

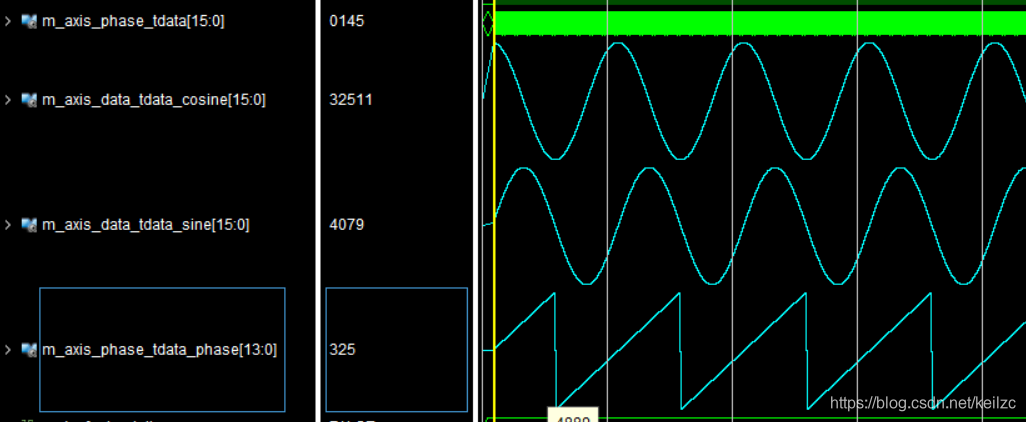

四、单通道配置

| 单通道 | 输入100MHz | 幅值位宽16bit | 相位位宽14bit | 输出1MHz |

注意此时相位位宽为14bits

五、多通道配置

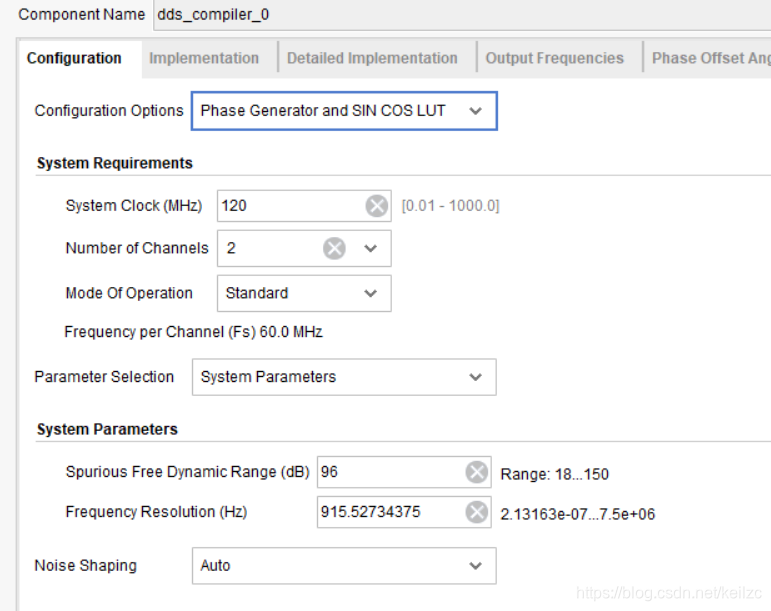

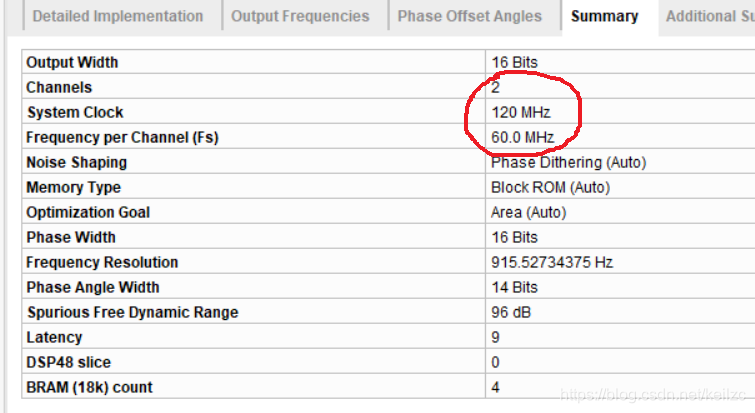

| 多通道 | 输入120MHz | 幅值位宽16bit | 相位位宽16bit | 输出1MHz和10MHz |

通道设置为2,我们就需要把Frequency Resolution重新设置:Frequency Resolution = 120000000/2^16 /2= 1831.0546875/2 = 915.52734375

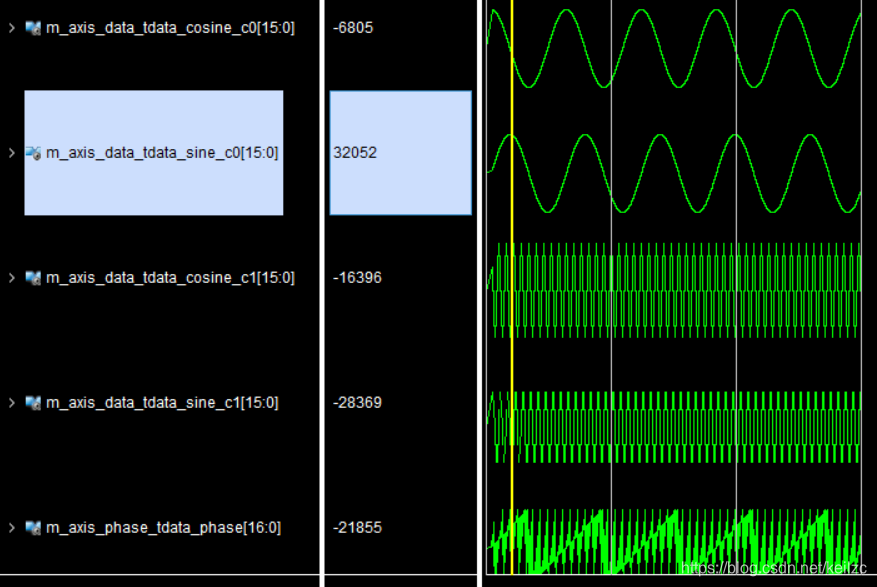

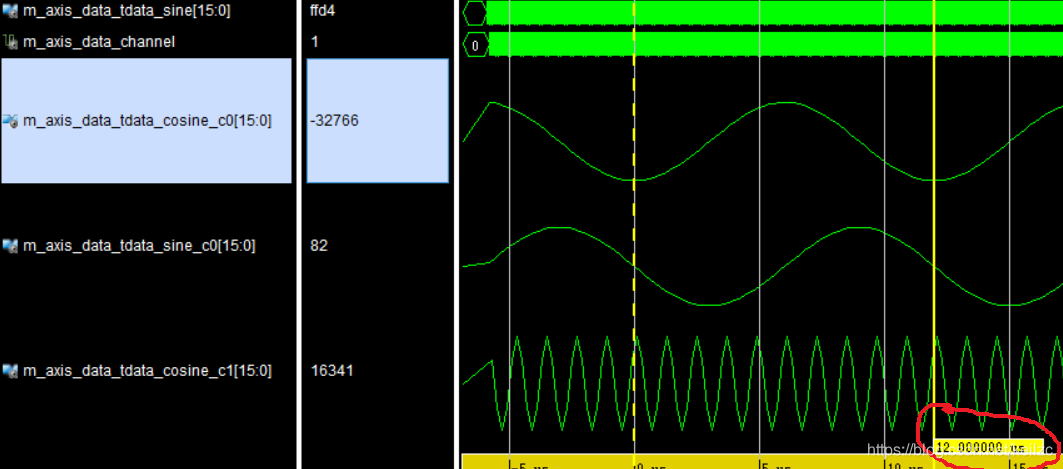

注意此处:这个地方需要格外注意,一开始有疑惑,为什么通道变成了2,数据宽度和接口都没有增加,原来是因为这双通道的数据是分时输出的,即交替输出。使用系统自带的testbench时,波形观察窗口会自动弹出两个通道的sin和cos波形,但是实际例化使用时需注意添加类似代码:

assign sin[15:0] = o_data_tvalid ? o_data_tdata[31:16]:16'b0;

assign cos[15:0] = o_data_tvalid ? o_data_tdata[15:0] :16'b0;

reg [15:0] sin_c0;

reg [15:0] sin_c1;

reg [15:0] cos_c0;

reg [15:0] cos_c1;

reg m_axis_data_channel = 1'b0;

always @(posedge aclk)

begin

m_axis_data_channel <= ~m_axis_data_channel;

if(m_axis_data_channel == 1'b0)

begin

sin_c0 <= sin;

cos_c0 <= cos;

end

else

begin

sin_c1 <= sin;

cos_c1 <= cos;

end

end

endmodule

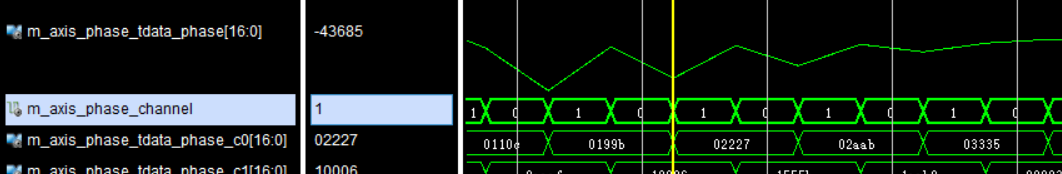

因为是分时输出的,所以体会下相位累加器变化规律:

通道值在切换,使用时根据该信号赋值:

六、仿真时间测量问题

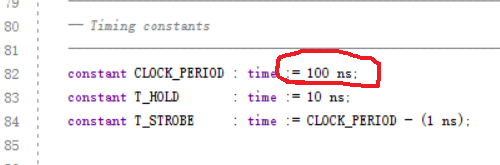

如上图所示,测量输出的1MHz信号的周期,结果为12us,理论值应该为1us,这是因为系统自带的仿真文件中,时间设置的是10MHz,如下图

而实际IP设置的是120MHz,12us对应120个10M的周期,而实际120个120M的周期就是1us,即1MHz信号。

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?